对某些人来说ESD是一种挑战,因为需要在处理和组装未受保护的电子元件时不能造成任何损坏。这是一种电路设计挑战,因为需要保证系统承受住ESD的冲击,之后仍能正常工作,更好的情况是经过ESD事件后不发生用户可觉察的故障。

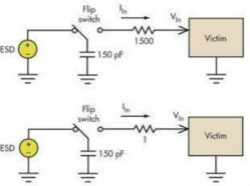

与人们的常识相反,设计人员完全可以让系统在经过ESD事件后不发生故障并仍能继续运行。将这个目标谨记在心,下面让我们更好地理解ESD冲击时到底发生了什么,然后介绍如何设计正确的系统架构来应对ESD。详细阅读>>

干货

干货

元器件静电放电隐患贯穿元器件设计、生产、检验、交接、运输、使用全过程,通用的防护手段不可或缺,但为满足新型号用元器件的发展对静电防护技术的提升需求,需要建立系统性、工程性的静电防护体系,遵循静电防护与全面质量管理相结合,静电防护与关键工序质量控制相结合,静电防护坚持领导、技术人员、基层员工三结合的原则,控制元器件静电放电损伤质量问题的产生,为保障型号元器件可靠性提供了有力的支撑。

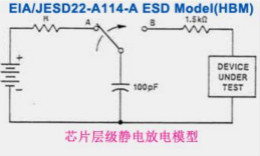

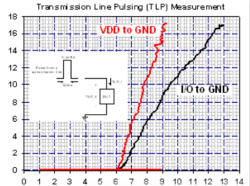

随着半导体技术的发展,大量集成电路被应用到电子产品中,静电放电也成为影响电子产品性能的关键因素。但是静电放电针对不同的环境也有不同的差异。最为明显的就是系统层级静电放电和芯片层级静电放电。详细阅读>>

智能手机设计在经历电磁兼容测试时候总是会出现或多或少的ESD静电放电抗扰问题,这些ESD问题都分布在哪里呢?主要是些什么样的ESD静电放电问题?有什么大的问题和后果?详细阅读>>

为实现十倍于USB2.0的传输速度,USB 3.0控制芯片必须使用更先进的制程来设计与制造,这也造成控制芯片对ESD的耐受能力快速下降。USB 3.0会被大量用来传输影音数据,对数据传输容错率会有越严格的要求,必要使用额外的保护组件来防止ESD事件对数据传输的干扰。详细阅读>>

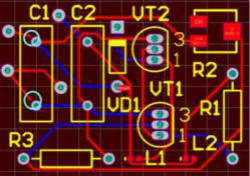

在PCB板的设计当中,可以通过分层、恰当的布局布线和安装实现PCB的抗ESD设计。通过调整PCB布局布线,能够很好地防范ESD.尽可能使用多层PCB,相对于双面PCB而言,地平面和电源平面,以及排列紧密的信号线-地线间距能够减小共模阻抗和感性耦合,使之达到双面PCB的1/10到1/100.对于顶层和底层表面都有元器件、具有很短连接线。详细阅读>>

静电,通常都是人为产生的,如生产、组装、测试、存放、搬运等过程中都有可能使得静电累积在人体、仪器或设备中,甚至元器件本身也会累积静电,当人们在不知情的情况下使这些带电的物体接触就会形成放电路径,瞬间使得电子元件或系统遭到静电放电的损坏(这就是为什么以前修电脑都必须要配戴静电环托在工作桌上,防止人体的静电损伤芯片),如同云层中储存的电荷瞬间击穿云层产生剧烈的闪电,会把大地劈开一样,而且通常都是在雨天来临之际,因为空气湿度大易形成导电通到。详细阅读>>

基础知识

基础知识

为了提高产品的耐受性,影响整个电子业的四个长期趋势,促使静电放电(ESD)保护在目的性工程的总体实践中日益重要。首先,与数年前相比,随着用户、信号I/O功能日益复杂和流行,产品上ESD的闪击进入点多了许多。尤其是对于信号I/O端口,以及小键盘、指示器、显示器。详细阅读>>

实际上,所有ESD测试标准都涉及了冲击源模型,例如人体、机器或充电器件。这些模型精确地解释了测试源的导电特性。最新的测试标准如普遍应用的IEC-61000-4-2,详述了冲击波形,进一步将测试源简化成测试源变量参数,为研究和评估各种高速瞬态缓解办法提供了关键信息。详细阅读>>

随着微电子技术的飞速发展,特别是随着集成电路特征尺寸的减小以及MOS集成电路的广泛使用,新型集成电路普遍具有线间距短、线细、集成度高、运算速度快、低功率和输入阻抗高等特点,因而导致这类器件对静电放电越来越敏感。详细阅读>>

ESD的设计学问太深了,这里只是抛砖引玉给大家科普一下了,基本上ESD的方案有如下几种:电阻分压、二极管、MOS、寄生BJT、SCR(PNPN structure)等几种方法。而且ESD不仅和Design相关,更和FAB的process相关,而且学问太深了,这里我也不是很了解,无法给再大家深入了。当然术业专攻学无止境,工作中只有不断学习才会创收更高效益。

关于我们 | About Us | 联系我们 | Contact Us | 隐私政策 | 版权申明 | 投稿信箱 | 网站地图

Copyright © WWW.CNTRONICS.COM All Rights Reserved

电子元件技术网 版权所有 粤ICP备10202284号 粤ICP证B2-20090022

未经版权所有人明确的书面许可,不得以任何方式或媒体翻印或转载本网站的部分或全部内容。