干货

干货

PLL(Phase Locked Loop): 为锁相回路或锁相环,用来统一整合时钟信号,使高频器件正常工作,如内存的存取资料等。PLL用于振荡器中的反馈技术。 许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步。一般的晶振由于工艺与成本原因,做不到很高的频率,而在需要高频应用时,由相应的器件VCO,实现转成高频,但并不稳定,故利用锁相环路就可以实现稳定且高频的时钟信号。

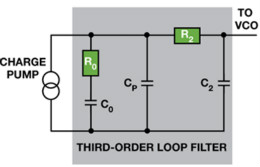

如参考文献中所描述,可采用标准过程来确定锁相环(PLL)中二阶环路滤波器的R0、C0 和CP 数值。它采用开环带宽(ω0)和相位裕量(ϕM)作为设计参数,并可扩展至三阶环路滤波器,从而确定R2 和C2(图1)。该过程可直接解出CP,然后推导出其余数值。详细阅读>>

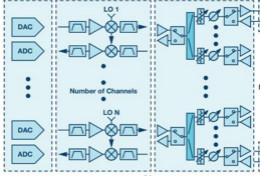

对于数字波束成形相控阵,要生成本地振荡器(LO) ,通常会考虑的实现方法是向分布于天线阵列中的一系列锁相环分配常用基准频率。对于这些分布式锁相环,目前文献中还没有充分记录用于评估组合相位噪声性能的方法。详细阅读>>

随着人们对通信系统的频率带宽、吞吐量和动态范围的需求日益提高,同时还要求毫米波5G使用更高的天线频率,因此对于通信系统或混合信号系统中使用的本地振荡器(LO)或时钟的质量也分别提出了更高的要求。详细阅读>>

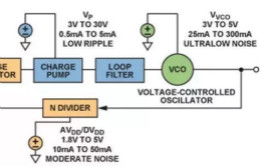

顾名思义,锁相环(PLL)使用鉴相器比较反馈信号与参考信号,将两个信号的相位锁定在一起。虽然这种特性有许多用武之地,但是PLL如今最常用于频率合成,通常充当上变频器/下变频器中的本振(LO),或者充当高速模数转换器(ADC)或数模转换器(DAC)的时钟。详细阅读>>

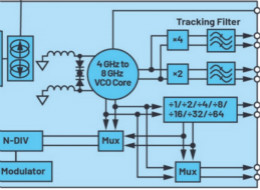

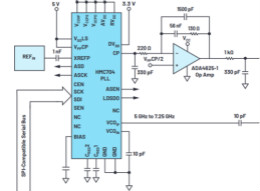

RF 和微波仪器(比如信号和网络分析仪)需使用宽带扫频信号来进行大多数基本测量。但宽带压控振荡器(VCO)通常会因最大限度扩大调谐范围所需的低 Q 和高 KVCO(VCO 的调谐灵敏度,单位:MHz/V)而具有最糟糕的相位噪声。钇铁石榴石(YIG)调谐振荡器凭借良好的宽带相位噪声性能和一个倍频程频率调谐范围巧妙地解决了该问题,但体积可能较大且费用昂贵...详细阅读>>

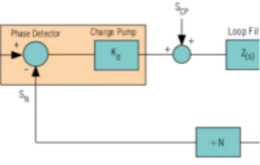

锁相环(PLL)是一种反馈系统,其中电压控制振荡器(VCO)和相位比较器相互连接,使得振荡器可以相对于参考信号维持恒定的相位角度。在使用PLL的过程中您都遇到过哪些问题呢?详细阅读>>

基础知识

基础知识

锁相环(PLL)是现代通信系统的基本构建模块,通常用在无线电接收机或发射机中,主要提供“本振”(LO)功能;也可用于时钟信号分配和降噪,而且越来越多地用作高采样速率模数或数模转换的时钟源。详细阅读>>

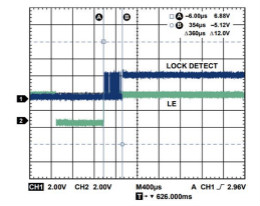

利用手动频段选择,锁定时间可从典型值 4.5 ms 缩短到典型值 360 μs。本文以高度集成的解调器和频率合成器 ADRF6820 为例,告诉大家如何手动选择频段以缩短PLL锁定时间。详细阅读>>

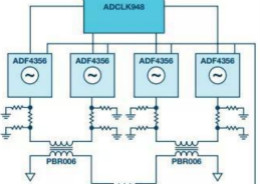

多年来,微波频率生成使工程师面临严峻的挑战,不仅需要对模拟、数字、射频(RF)和微波电子有深入的了解,尤其是锁相环(PLL)和压控振荡器(VCO)集成电路组件方面,还需要具备可调滤波、宽带放大以及增益均衡等专业知识。详细阅读>>

锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

关于我们 | About Us | 联系我们 | Contact Us | 隐私政策 | 版权申明 | 投稿信箱 | 网站地图

Copyright © WWW.CNTRONICS.COM All Rights Reserved

电子元件技术网 版权所有 粤ICP备10202284号 粤ICP证B2-20090022

未经版权所有人明确的书面许可,不得以任何方式或媒体翻印或转载本网站的部分或全部内容。