【导读】锁相环(PLL)是一种反馈系统,其中电压控制振荡器(VCO)和相位比较器相互连接,使得振荡器可以相对于参考信号维持恒定的相位角度。在使用PLL的过程中您都遇到过哪些问题呢?

ADI智库新上线的文档整理了PLL应用中的常见问题,包含PLL芯片接口相关问题、PLL芯片性能相关问题、PLL的调试以及如何为设计选择合适的PLL芯片等问题。在这里,扫描二维码可免费获取哦~

扫码免费下载《锁相环常见问题解答》

1 参考晶振有哪些要求?该如何选择参考源?

波形:可以使正弦波,也可以为方波。

功率:满足参考输入灵敏度的要求。

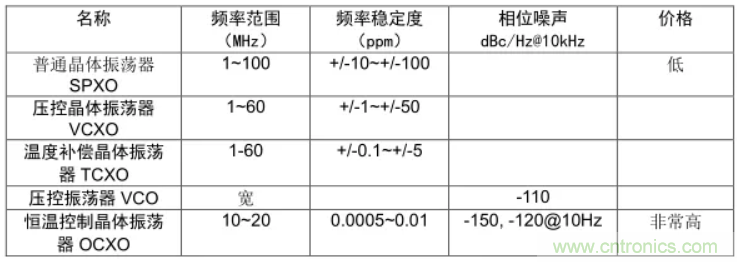

稳定性:通常用 TCXO,稳定性要求< 2 ppm。这里给出几种参考的稳定性指标和相位噪声指标。

频率范围: ADI 提供的 PLL 产品也可以工作在低于最小的参考输入频率下,条件是输入信号的转换速率要满足给定的要求。

建议

在PLL 频率综合器的设计中,我们推荐使用温度补偿型晶振(TCXO)。在需要微调参考的情况下使用 VCXO,需要注意 VCXO 灵敏度比较小,比如 100Hz/V,所以设计环路滤波器的带宽不能很大(比如 200Hz),否则构成滤波器的电容将会很大,而电阻会很小。普通有源晶振,由于其温度稳定性差,在高精度的频率设计中不推荐使用。

2 锁相环系统的相位噪声来源有哪些?减小相位噪声的措施有哪些?

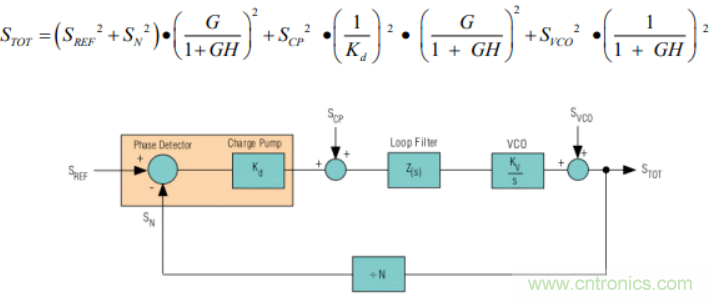

参考晶振(TCXO,VCXO)和 R 分频,PLL 电荷泵,压控振荡器(VCO),N 分频。锁相环系统的相位噪声来源于四个部分,参考输入,反馈分频 1/N,电荷泵,VCO,这四部分贡献项可以用公式来表示。

锁相环相位噪声贡献项模型

……(公式解说请扫描二维码下载完整文档查看)

减小相位噪声的措施:

(1)增大鉴相频率(N 变小)

(2)缩小环路带宽(限制噪声)

(3)增大电荷泵电流(Kd)

(4)参考晶振选用更低噪声的产品。

如果在频谱分析仪上测出的单边带相位噪声曲线的转折频率大于设计的环路带宽,说明系统的噪声太大,应该检查参考晶振,电荷泵的电流,PLL Core Power Level。

3 频繁地开关锁相环芯片的电源会对锁相环有何影响?

不建议频繁地开关锁相环的电源,这可能会使芯片暂时进入一种不稳定的电源状态(下电时电容泻放电荷不充分,上电时电容充电不充分),从而导致锁相环不能锁定。如果产品要求如此,则可使用芯片资料中提到的“CE pin method”来对芯片进行上电和下电。

4 到底用小数分频好还是整数分频好?

从相噪性能上看,小数分频锁相环可以工作在较高的鉴相频率,分频系数 N 小,在较小信道间隔的应用中,与整数分频的锁相环相比,可以获得较好的带内相位噪声。这时,小数分频的锁相环是首选。但是如果是单频或者信道间隔很大(>几百 kHz)的应用,小数分频的这种低相噪优势并不明显。整数分频的锁相环同样可以达到高鉴相频率,低相噪的目的,甚至会超过小数分频的锁相环。另外也需要考虑由于采用了杂散补偿电路,所以该电路会增加环内的相位噪声。

从杂散性能上看,在较小的信道间隔(<10kHz)上,小数分频锁相环远远好于整数分频锁相环,为什么呢?(请扫描二维码下载完整文档查看)

5 环路滤波器采用有源滤波器还是无源滤波器?

有源滤波器因为采用放大器而引入噪声,所以采用有源滤波器的 PLL 产生的频率的相位噪声性能会比采用无源滤波器的 PLL 输出差。因此在设计中我们尽量选用无源滤波器。其中三阶无源滤波器是最常用的一种结构。PLL 频率合成器的电荷泵电压 Vp 一般取 5V 或者稍高,电荷泵电流通过环路滤波器积分后的最大控制电压低于 Vp 或者接近 Vp。

如果VCO/VCXO 的控制电压在此范围之内,无源滤波器完全能够胜任;如果VCO/VCXO 的控制电压超出了 Vp,或者非常接近 Vp 的时候,就需要用有源滤波器。在对环路误差信号进行滤波的同时,也提供一定的增益,从而调整VCO/VCXO控制电压到合适的范围。

那么如何选择有源滤波器的放大器呢?这类应用主要关心一下的技术指标:

● 低失调电压(Low Offset Voltage) [通常小于 500uV]

● 低偏流(Low Bias Current) [通常小于 50pA]

如果是单电源供电,需要考虑使用轨到轨(Rail-to-Rail)输出型放大器。

PLL更多常见问题

● 控制多片 PLL 芯片时,串行控制线是否可以复用?

● 环路滤波器参数如何设置?

● PLL 对于 VCO 有什么要求?如何设计 VCO 输出功率分配器?

● 如何设置电荷泵的极性?

● 锁定指示电路如何设计?

● PLL 对射频输入信号有什么要求?

● PLL 芯片对电源的要求有哪些?

● 为何测出的相位噪声性能低于 ADIsimPLL 仿真预期值?

● 锁相环锁定时间取决于哪些因素?如何加速锁定?

● 为何锁相环在做高低温试验的时候,出现频率失锁?

● 非跳频(单频)应用中,最高的鉴相频率有什么限制?

推荐阅读: