【导读】在高频电路设计中,经常会用到AC耦合电容,要么在芯片之间加两颗直连,要么在芯片与连接器之间加两颗。看似简单,但一切都因为信号的高速而不同。信号的高速传输使这颗电容变得不“理想”,这颗电容没有设计好,就可能会导致整个项目的失败。因此,对高速电路而言,这颗AC耦合电容没有优化好将是“致命”的。

正确理解AC耦合电容

在高频电路设计中,经常会用到AC耦合电容,要么在芯片之间加两颗直连,要么在芯片与连接器之间加两颗。看似简单,但一切都因为信号的高速而不同。信号的高速传输使这颗电容变得不“理想”,这颗电容没有设计好,就可能会导致整个项目的失败。因此,对高速电路而言,这颗AC耦合电容没有优化好将是“致命”的。

下面笔者依据之前的项目经验,盘点分析一下我在这颗电容的使用上遇到的一些问题。

最开始要先明白AC耦合电容的作用。一般来讲,我们用AC耦合电容来提供直流偏压,就是滤出信号的直流分量,使信号关于0轴对称。既然是这个作用,那么这颗电容是不是可以放在通道的任何位置呢?这就是笔者最初做高频电路时,在这颗电容使用上遇到的第一个问题——AC耦合电容到底该放在哪。

这里拿一个项目中常遇到的典型通路来分析。

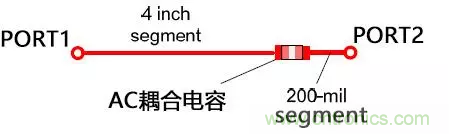

图1:AC耦合电容典型通路

在低速电路设计中,这颗电容可以等效成理想电容。而在高频电路中,由于寄生电感的存在以及板材造成的阻抗不连续性,实际上这颗电容不能看作是理想电容。这里信号频率2.5G,通道长度4000mil,AC耦合电容的位置分别在距离发送端和接收端200mil的位置。我们看一下仿真出的眼图的变化。

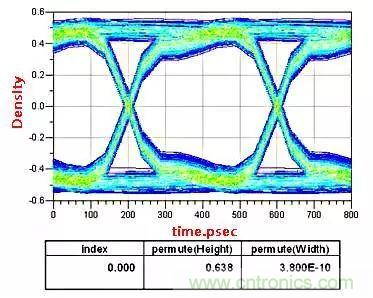

图2:AC耦合电容靠近发送端的眼图

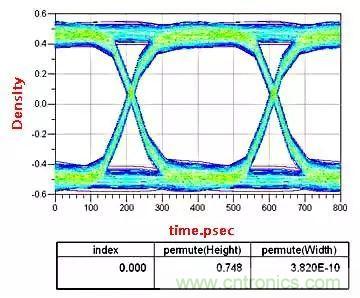

图3:AC耦合电容靠近接收端的眼图

显然,这颗AC耦合电容靠近接收端的时候信号的完整性要好于放在发送端。我的理解是这样的,非理想电容器阻抗不连续,信号经过通道衰减后反射的能量会小于直接反射的能量,所以绝大多数串行链路要求这颗AC耦合电容放在接收端。但也有例外,笔者之前做板对板连接时遇到过这个问题,查PCIE规范发现如果是两个板通常放置在发送端上,此时还利用到了AC耦合电容的另外一个作用——过压保护。比如说SATA,所以通常要求靠近连接器放置。

解决了放置的问题,另一个困扰大家的就是容值的选取了。这样说,我们的整个串行链路等效出的电阻R是固定的,那么AC耦合电容C的选取将会关系到时间常数(RC),RC越大,过的直流分量越大,直流压降越低。既然这样,AC耦合电容可以无限增大吗?显然是不行的。

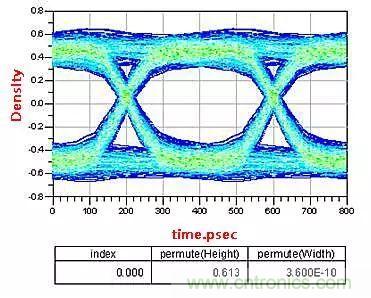

图4:AC耦合电容增大后测量到的眼图

同样的位置,与图3相比可以看出增大耦合电容后,眼高变低。原因是“高速”使电容变的不理想。感应电感会产生串联谐振,容值越大,谐振频率越低,AC耦合电容在低频情况下呈感性,因此高频分量衰减增大,眼高变小,上升沿变缓,相应的JITTER也会增大。

通常建议AC耦合电容在0.01uf~0.2uf之间,项目中0.1uf比较常见。推荐使用0402的封装。

最后,解决了以上两个问题,再从PCB设计上分析一下这颗电容的优化设计。实际在项目中,与AC耦合电容的位置、容值大小这些可见因素相比,更加难以捉摸的是板材本身(包括焊盘的精度、铜箔的均匀度等)以及焊盘处的寄生电容对信号完整性的影响。我们知道,高频信号必须沿着有均匀特征阻抗的路径传播,如果遇到阻抗失配或者不连续的情况时,部分信号会被反射回发射端,造成信号的衰减,影响信号的完整性。项目中,这种情况通常会出现在焊盘或者是板载连接器处。笔者最初涉及的高速电路设计时,经常遇到这个问题。

解决这个问题要从两个方面入手。首先在板材的选取上,我们在应用中通常选用高性能的ROGERS板材,罗杰斯的板材在铜箔厚度的控制上非常精确,均匀的铜箔覆盖大大降低了阻抗的不连续性;然后在消除焊盘处的寄生电容上,业内常见的办法是在焊盘处做隔层处理(挖空位于焊盘正下方的参考平面区域,在内层创建铜填充),通过增大焊盘与其参考平面(或者是返回路径)之间的距离,减小电容的不连续性。在笔者的项目中多采用介质均匀、铜箔宽度控制精确的ROGERS板材也有效提高了焊盘的加工精度。

通过仿真对比一下ROGERS板材做精确隔层处理前后的信号完整性。

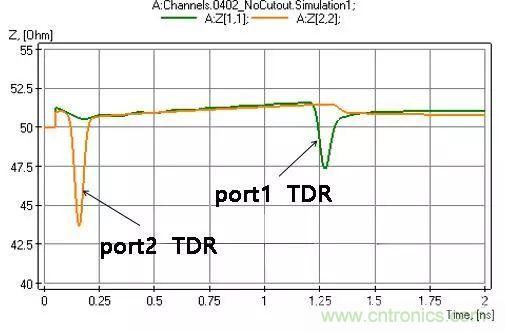

图5:做隔层处理前的TDR

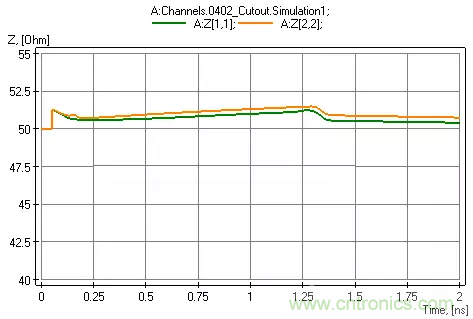

图6:做隔层处理后的TDR

图5图6对比,发现未处理之前阻抗的跳跃很明显,隔层处理后的阻抗改善很多,几乎没有任何阶跃与不连续。

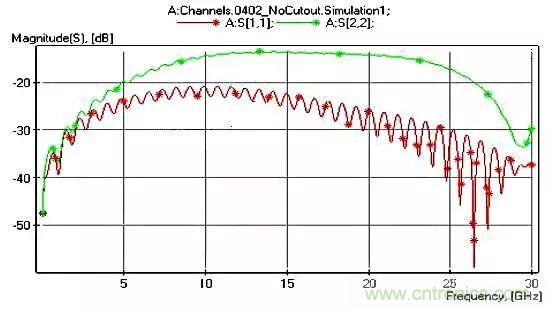

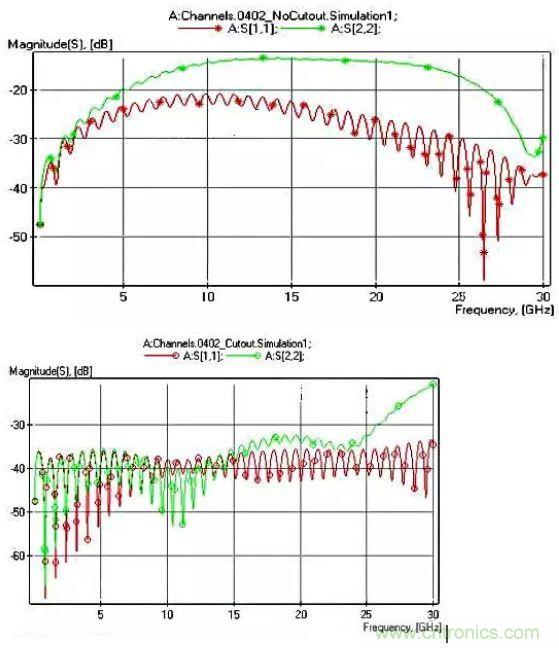

图7:做隔层处理前的回波损耗

图8:做隔层处理后的回波损耗

图7图8对比,在用ROGERS板材做隔层处理之后,相比未做隔层处理回波损耗下降到-30dB之内,大大降低了回波损耗,保证了信号传输的完整。

综上,想要搞定高频电路中这颗“致命”的AC耦合电容,不仅要做足电路设计上的功课,同时,选择性能更好的高频PCB板材料会让你事半功倍。

匹配电路的电感选择

对高频电路而言,电路之间的电感匹配很重要。电感匹配是指在信号的传输线路上,让发送端电路的输出阻抗与接收端电路的输入阻抗一致,匹配后,可以最大限度地把发送端的电力传送到接收端。

匹配电路使用电容器和电感器,但是实际的电容器和电感器与理想的元件不同,有损耗。表示该损耗的有Q值。Q值越大,表示电容器和电感器的损耗就越小。

电感的Q值与高频电路的损耗

匹配电路中使用的电感器的Q值的大小,对高频电路的损耗也会产生影响。

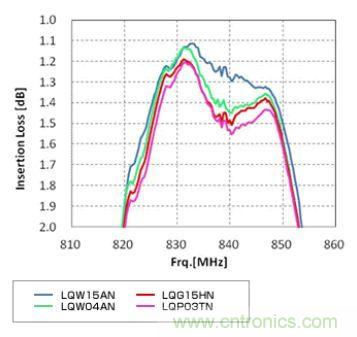

为了确认此事,我们采用了村田的SAW滤波器 (通频带800MHz频段) 和RF电感,在匹配电路中换装Q值不同的RF电感,测量和比较了SAW滤波器的插入损耗。

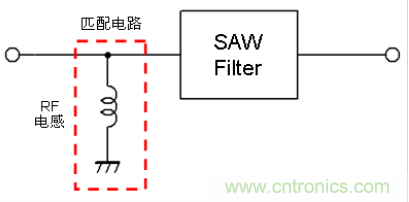

图9表示电路图。此次的电路,虽说是匹配电路,但是只有一个RF电感器。

图9: SAW滤波器与匹配电路

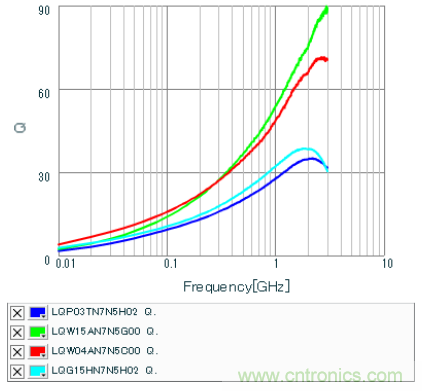

图10表示此次进行了换装的RF电感的Q值的频率特性,表1表示结构、尺寸、Q值 (800MHz时的Typ.值)

图10: RF电感的Q值比较 (均为7.5nH)

表1 RF电感的比较

※图10的图表是采用村田提供的设计辅助工具SimSurfing表示的。

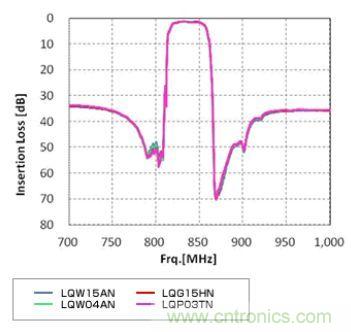

换装匹配电路的RF电感时的SAW滤波器的整体特性见图11,通频带特性见图12。

图11: SAW滤波器的整体特性

图12: SAW滤波器的通频带特性

从图12的通频带特性来看,可以确认SAW滤波器的插入损耗因所使用的RF电感而异。高频电路的这种水平的损耗越来越重要。

从此次的实验结果可知,RF电感的Q值越大 (损耗越小) ,SAW滤波器的插入损耗就越小。也就是说,电感器损耗的大小就是包括匹配电路在内的SAW滤波器损耗的大小。

请注意,使用的高频元件 (此次为SAW滤波器) 、匹配电路、频段等不同,损耗也将各异。

电感的偏差与对匹配电路的影响

另外,实际的电感器的阻抗值为1.0nH、1.1nH、1.2nH之类的不连续值。进行匹配时,有时必须采用细致的常数步骤进行微调。同时,阻抗值的偏差 (标准离差) 会变成匹配的标准离差,为了满足必要特性,有时需要偏差小的电感器。村田的电感器当中,薄膜型LQP系列最符合细致的常数步骤和偏差小的要求。

根据以上情况,有必要对SAW滤波器的整合回路RF电感的Q特性、偏差值、尺寸、成本等方面,进行比较讨论之后做出选择。在贴装空间有剩余的情况下,Q值偏高的卷线电感LQW15/LQW04为最佳选择。此外,贴装空间有所限制的情况下,小尺寸0603、拥有较高Q值的LQP03HQ/LQP03TN_02为最佳选择。

推荐阅读: