【导读】在芯片设计的精密体系中,复位信号本是保障功能启动的“安全锚点”,但当复位逻辑突破单一域的限制、跨越不同域边界时,这个原本可靠的“锚点”却可能演变为潜藏系统风险的“隐形裂缝”。跨复位域(RDC)问题正是这样一种隐蔽的挑战:它让功能仿真显示“一切正常”,却在芯片回片后的复杂工况下,因复位信号的异步释放、时序偏差等触发随机功能错误,轻则导致系统异常,重则造成流片失败。对于追求高可靠性的现代芯片开发而言,建立一套可靠的RDC签核流程是确保一次流片成功的关键。

核心概念:什么是复位域与RDC?

要理解RDC,首先要明确“复位域”的概念。复位域是指由同一个异步复位信号控制的一组寄存器或逻辑模块。根据复位策略的复杂度,系统可以分为:

单复位域系统:整个芯片使用一个全局复位信号,这是最简单、理想的情况。

多复位域系统:不同功能模块(如CPU核心、DMA控制器、外设)使用各自独立控制的复位信号。这些信号可能异步释放,也就是释放时间不同、甚至来自不同的逻辑区块或电源域。现代复杂的片上系统(SoC),从手机处理器到数据中心AI芯片,几乎都是复杂的多复位域系统。

跨复位域(RDC),就是指一个信号从一个复位域传输到另一个复位域的路径。当这两个域的复位信号在类型、时序或相位关系上存在差异时,RDC风险就产生了。

为何RDC是危险的“芯片杀手”?

RDC风险容易被忽视,通常缘于复位网络在大型设计中不像时钟网络那么复杂,设计者容易对此掉以轻心。然而其发生的后果与异步时钟域交叉引起的后果同样致命。RDC的核心风险源于复位的异步性,寄存器的异步复位输出由于缺乏时序上的约束,使得后续的时序电路可能引发一系列问题:

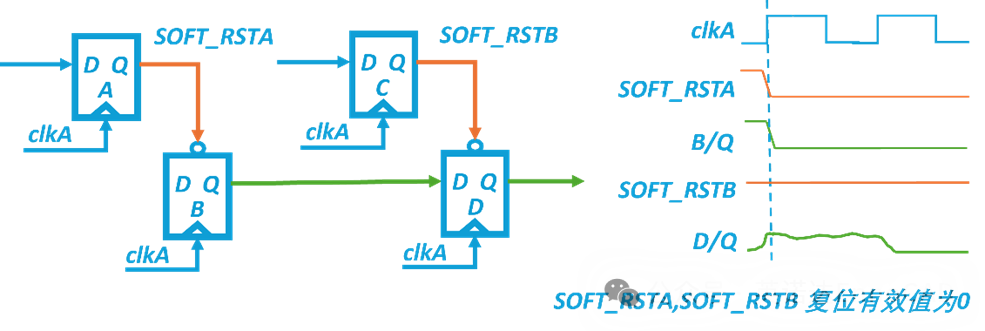

亚稳态风险:这是最经典也最危险的问题。如果发送域的复位先激活,其输出信号开始变化,而此时接收域的寄存器仍处于活跃状态,其时钟沿可能恰好采到正在变化的信号,导致寄存器输出陷入既非“0”又非“1”的亚稳态,并将这个不确定状态传播到后续电路,导致功能性错误。

复位毛刺传播:如果异步复位信号由组合逻辑产生,复位信号可能由于组合逻辑不同输入路径延迟不同产生毛刺,从而对时序电路进行未预期的复位,导致功能紊乱。

复位同步后的再汇聚问题:当两个源自相同复位域或不同步复位域的信号,经过不同路径(如不同长度的同步器链)同步到同一复位域后再次汇聚时,可能由于复位同步路径上的延迟差异而失去数据上的关联性,导致逻辑错误。

这些错误的隐蔽性极强,传统的验证方法,如STA或常规的功能仿真,很难捕捉到它们,因为问题只在特定、罕见的复位时序组合下才会被触发。 一旦带有RDC问题的芯片流入市场,故障现象间歇性出现,诊断和修复的成本极其高昂。

设计实践:从源头防范RDC

优秀的芯片设计不仅依靠后期验证,更在于前期的架构规避。工程师们有一系列成熟的设计准则来减少RDC风险:

首要原则-复位架构简化:在系统架构设计阶段,应尽量减少不必要的异步复位源。对于同一时钟域内的模块,尽量使用同步复位或统一的异步复位,从根本上减少异步复位跨域路径。

电路隔离与约束技术:对于电路中存在从“异步复位中”信号到“未复位”信号的路径,可以在路径上插入复位隔离单元,在发送域复位有效期间将输出钳位到已知安全值。

复位机制保障:对于数据流确定的电路,通过电路设计保证上游电路先于下游电路复位,或者下游电路永远跟随上游电路同时复位,这些复位机制能保证数据在跨复位域传输时消除风险。

现代验证利器:RDC专用签核工具

即使遵循了最佳设计实践,在数亿门级规模的复杂芯片中,人工审查所有潜在的RDC路径也是不可能的。这时,专业的RDC签核工具就成为了保证流片成功的必备。英诺达EnAltius®跨域检查工具,继支持时钟域交叉(CDC)检查功能后,将进一步推出RDC签核检查功能,帮助芯片开发者快速完成RDC的验证和收敛。

总结

跨复位域问题体现了现代芯片设计中异步复位架构的复杂性,行业内的成功实践表明,通过将前瞻性的复位架构设计、系统性的复位场景管理,与强大的自动化签核工具相结合,可以彻底地消除与复位相关的设计隐患。这不仅关乎工具的选择,更关乎一套涵盖设计、验证和调试的完整方法论的建立。只有通过如此严谨缜密的流程,才能确保每一颗高度复杂的数字芯片都能稳定、可靠地运行。