【导读】大家都知道,电源效率对于便携式设备以及模拟IC的噪声抗扰度来说都非常重要。本文主要介绍电压参考电路,其不仅支持极低的工作静态电流(低于250nA),而且还符合标准CMOS工艺。

这种电路针对各种应用进行了优化设计,适合便携式电子设备、汽车、医疗设备,以及高电源抑制比 (PSRR) 和开关噪声抗扰度都非常重要的片上系统 (SoC) 实施。

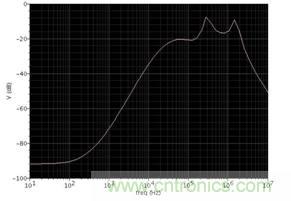

上述电压参考在低频率下支持90dB。输出电压变化的标准偏差是 0.5%,在–40℃至125℃温度范围内的温度系数为15ppm/℃。这些特性可在1.6V至5.5V的电源电压范围内实现。可实施各种用于为电压参考实现输入噪声抗扰度的方法。

介绍

几乎每款模拟电路都需要高精度高稳定参考电压或电流源。不过,在选择片上系统(SoC) 技术时,参考电压模块不应成为限制因素。也就是说这类系统所选用的技术工艺对于参考电压源来说并不一定总是最理想的。因此,其设计应该更稳健,才能适应各种技术工艺的变化。

电池通常可作为SoC的电源。这就更需要提高工作在大电源电压范围内的电压参考源的线性稳压性能。要延长电池使用寿命,就需要低静态电源电流。同时,还需要在宽泛频率下实现高电源抑制比(PSRR),以抑制来自高速数字电路、降压转换器或片上其它开关电路的噪声。本文主要介绍具有高PSRR的超低静态电流带隙电压参考。

基本带隙电压参考结构

改善 PSRR的主题思想是在低压降稳压器(LDO)后面布置一个带隙电压源。现有线性稳压器拓扑在静态电流、DC负载稳压、瞬态响应、去耦电容以及硅芯片面积要求方面存在很大差异。由于我们的目标是在没有外部电容器的情况下,在同一芯片上提供全面集成型 LDO,因而典型LDO结构并不适合。

这些结构与超低静态电源电流相矛盾。为了缓解这一矛盾,您可为LDO 使用与参考源相同的带隙。不宜采用标准LDO结构的原因在于它需要输出电容器来实现稳定工作。最佳选项是带一个增益级的结构,其无需输出电容器便可实现稳定。

低压降稳压器

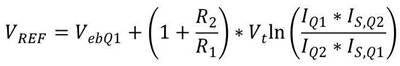

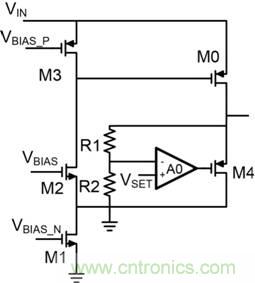

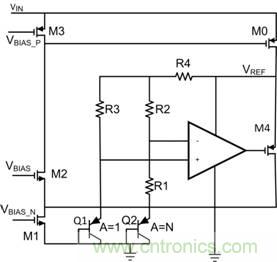

图1是该设计[1]中所使用LDO的内核及其简化原理图。图1[2]中的M0和M4代表翻转电压跟随器(FVF),其可实施无逆向功能及相关极点的单级稳压。静态电流由晶体管M1和M3确定。晶体管M2 可作为共栅放大器。

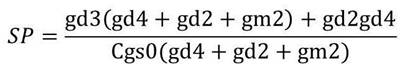

LDO的开环增益由第一个级联级(即晶体管M2和M3)决定。可作为负载的 M4 PMOS跟随器存在低阻抗源,因此 FET M0的输出增益接近1。在图2中的小型信号等效电路的帮助下,对所推荐的 LDO结构进行稳定性分析,结果显示只有一个极点(公式1):

可作为补偿电容器的M0栅源电容器可创建 LDO的主极点。因此无需去耦片外电容器,便可使LDO[3]稳定。

图1:具有翻转电压跟随器、无输出电容器的LDO

图2:LDO的小型信号等效电路

这种LDO的另一项优势是简单的自启动程序,其无需专用电路。最初,在电压VDD 为 0 时,VOUT也为 0,跟随器M4 在无反馈的情况下关闭,M1的偏置电流大于M3的偏置电流。因此,栅极电压M0 不仅可降低,而且还可驱动输出电压VOUT至所选的输出电压值。

这种架构的缺点是线路稳压及 PSRR差。原因在于低开环增益,因为它仅由一个增益级决定。合理的解决方案可能是第一级的级联电流源,其可提高增益,进而可提高线路稳压性能和PSRR。

图1中的LDO输出电压为(公式2):

其中,VSET为参考电压,VGS,M4是M4的栅源电压。

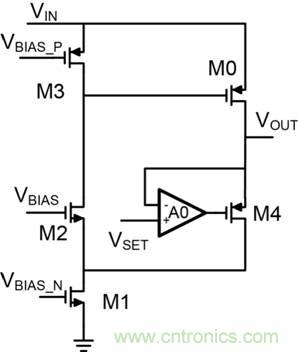

因此,输出电压对温度和工艺变化极为敏感。要避免这种问题,就必须创建一个更为理想的跟随器,其中 M4 是反馈环路的一部分(图3)。

图3:M4位于放大器反馈环路中、无输出电容器的LDO。

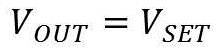

这种情况下的输出电压为公式3:

其中,A0是放大器的开环增益反馈。对于高反馈放大器增益而言,可使用公式4:

图4:具有电阻式分压器、M4位于放大器反馈环路、无输出电容器的 LDO

在反馈环路(图4)中添加电阻式分压器后,输出电压转变为:

VOUT=VSET(1+R1/R2)

FVF反馈放大器不影响整体 LDO稳定性,因为它位于主LDO反馈环路的外部。对于本地反馈环路而言,只要求设计方案稳定。

[page]

带隙内核说明

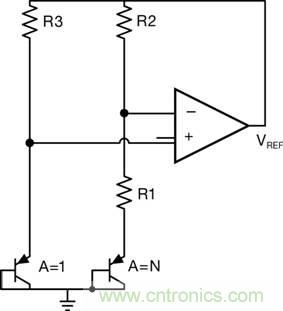

所选用的带隙内核(图5)采用在标准CMOS 技术中广泛使用的经典结构。

图5:所推荐带隙电压参考内核的简化方框图

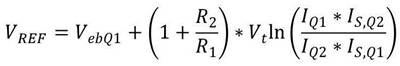

通过添加双极性晶体管的负温度系数基射极间电压,可获得带隙电压的低温系数,从而可通过在不同电流密度下偏置的两个基射极间电压之差获得正温度系数电压。为电阻器R2和R3选择相等的值,参考电压就可表示为公式5:

其中VEB是Q1的基射极间电压,VT是热电压,IQ1和IQ2是通过晶体管Q1和Q2的电流,而 IS,Q1和IS,Q2则分别是Q1和Q2的饱和电流。

误差源

要为任何带隙电压参考实现良好的精确度,必须定义总体精度误差的主要形成因素[4]。以下是所推荐架构的最大误差源:

放大器失调电压

电阻器R1与R2之间的不匹配

双极性晶体管的饱和电流不匹配

电阻器R1、R2和R3的变化

放大器失调电压

放大器失调电压对于参考电压精确度来说很关键,因为它通过与发射-基极电压差相同的方式放大。尽管我们可以通过增大双极性晶体管的面积比来减少对放大器失调电压的影响,但由于电压差具有对数尺度,因此我们会受到这个比例的合理值限制。在本例中,我们选择的比例为24。

对放大器失调电压影响最大的是输入级晶体管阀值电压变化。它可通过增大放大器输入对的尺寸来改善(公式6)。

电阻器R1与R2之间的不匹配

电阻器R1与R2之比可定义公式5中正温度系数项的增益。为了让该增益系数准确,我们使用较大面积单位电阻器。使用特殊的电阻器布局,可实现0.1%的误差比例精度。

双极性晶体管的电阻器与饱和电流的变化

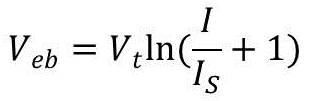

这两种变化会导致双极性晶体管的基极-发射极电压Veb发生偏移。基极-发射极电压可按公式7确定:

其中,I是发射极电流,IS是双极性晶体管的饱和电流。引起IS变化的主要原因是Q1和Q2晶体管面积的不匹配以及杂质浓度的变化。

电阻器R1的变化可影响通过晶体管Q2 的电流I的绝对值,它是负温度系数项VEB的一部分。

电阻器R2和R3分别可确定通过Q1和Q2 的电流值。R2和R3的变化可导致参考电压(公式5)的正温度系数不准确。不过,可通过对电阻器R2与R3进行良好匹配来降低该变化所引起的误差。

高PSRR带隙电压参考电路

由于上述传统电压参考架构的所有缺点,我们建议采用改进的电压参考,它是带隙电压参考与低压降稳压器的整合解决方案(图6)。

图6:带隙电压参考结合低压降稳压器的方框图

该示例中的输出电压可由公式8确定:

VREF节点既是带隙参考的输出节点,同时也是带隙核心电路的电源线。这有助于我们通过 LDO保护带隙核心电路免受电源电压纹波影响。

要获得小静态电流,电阻器 R1、R2、R3和R4的值就会比较大,推荐电路的电阻为8MΩ。这可使通过 Q1和Q2的电流降低至 40nA。推荐架构的整体静态电流为250nA。除此之外,我们还可采用一款静态电流为100nA的偏置电流电源。

偏置电流电路

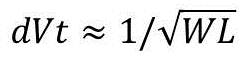

所推荐的偏置电流电路基于一种著名的电路结构(如图7所示),在参考文献5[5]中有详细介绍。

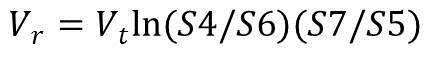

在该电路中,两个N型晶体管M5和M7构成第一个增益为S7/S5 的电流镜,而两个P型晶体管M4和M6 则构成第二个增益为S4/S6 的电流镜,其中S4、S5、S6和S7是相应晶体管的面积。

偏置发生器通常不需要特别启动电路,这可减少静态电流和占用面积。如果电流足够小,电阻R 就可以忽略。由M5/M7和M4/M6构成的两个电流镜可互连成一个闭环。

该环路增益大于单位增益,因此两个分支中的电流都会增大,直至达到均衡为止。这将由电阻R的压降定义,可表示为公式9:

图7:具有动态启动电流的偏置生成器

要加快启动速度并避免可能的漏电影响,可使用一款附加启动电路。晶体管M0 可作为具有极大电阻的横向双极性 NPN晶体管使用,其可最大限度地降低启动电流。电容器 C 不仅可在电路加电时提供快速瞬态启动,而且还可防止启动电路发生振荡。在启动之后,电路由晶体管M2阻断。偏置模块的偏置电流是40nA。总流耗是 80nA。

[page]

验证结果

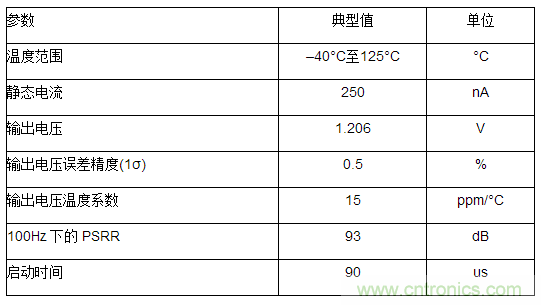

所推荐带隙参考不仅可用于超低噪声、高PSRR的低压降稳压器,而且还可采用CMOS 9T5V 技术实施。PSRR值如图8所示,输出电压精度的蒙特卡洛温度变化仿真结果如图9所示。测量结果请参见表1。

图8:电压参考源的PSRR

图9:输出电压精度

表1.测量数据

总结

我们不仅介绍了采用 CMOS9T5V 0.18μm工艺实施的、高PSRR 的极低功耗带隙电压参考,而且还详细介绍了最大限度降低功耗和最大限度提高PSRR的设计条件。将带隙电压参考与低压降稳压器相结合,可在100Hz下获得93dB的高PSRR。该电路的最大静态电流仅为250nA,是超低功耗应用最具吸引力的选择。

参考文献

J. Guo和K. N. Leung,《采用 90 纳米 CMOS工艺技术实施的、无输出电容器的小型 6uWLDO》,摘自《IEEE固态电路杂志》2010年9月第 48卷第 9 号;

Blakiewicz, G.,《支持更快时间响应的CMOS低压降稳压器》,摘自《2011年第18届国际大会会议记录 — 集成电路与系统混合设计 (MIXDES)》2011年6月16 ~ 18 日第 ××卷第 ×× 号的第 279 页 ~ 282 页;

P. Hazucha、T. Karnik、B. A. Bloecher、C. Parsons、D. Finan 和 S. Borkar,《支持超快负载调节的小型线性稳压器》,摘自《IEEE固态电路杂志》2005 年 4 月第 45 卷第 4 号;

S. Strik,《带隙电压参考:误差及其最小化方法》,摘自《BEC 2006会议记录》2006年10月2日第 123 页 ~ 126页;

E. Vittoz 与 J. Fellrath,《基于弱反向工作的CMOS模拟集成电路》,摘自《IEEE固态电路杂志》1977年6月SC-12卷第 3 号;

如欲了解有关LDO的更多详情,敬请访问:www.ti.com/ldo-ca。