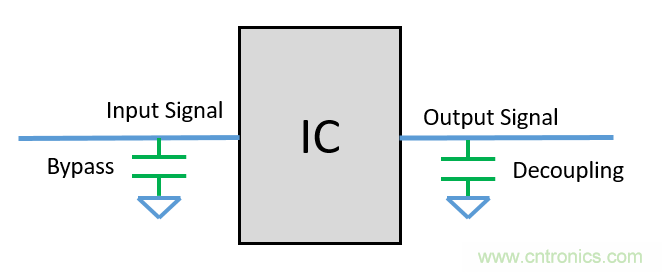

【导读】去耦电容是电路中装设在元件的电源端的电容,此电容可以提供较稳定的电源,同时也可以降低元件耦合到电源端的噪声,间接可以减少其他元件受此元件噪声的影响。今天聊聊有意思的去耦电容的摆放设计。先来看看Bypass和decoupling充满画面感的区别。请看图。

从远处而来的信号(不一定是有用信号)经过电容滤波,这时候的电容所起到的作用,起了一个好听的名字,叫Bypass;

从源段输出去的信号经过的滤波电容,这个电容叫decoupling;

EN,蛮有想像力的。

在低频场合,许多人根本就不关心EMC,上次一个朋友说,你说那么多高速的东西,可我做电力的,用不上呀,听起来好像是我不好,我应该多顾及一下他听课的感受。不过,这个时代是高速的时候代,DDR4都3200了,你还窝在50/60Hz,是不是该多充充电了。

同样,低频场合,许多EMC设计规则都是看不见的。在高频场合,许多细节就需要关心了,一不小心就一堆EMC问题。比如今天要聊的电容的摆放。

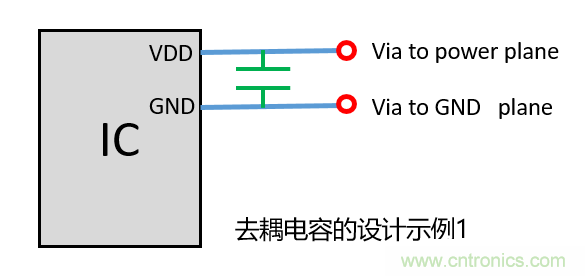

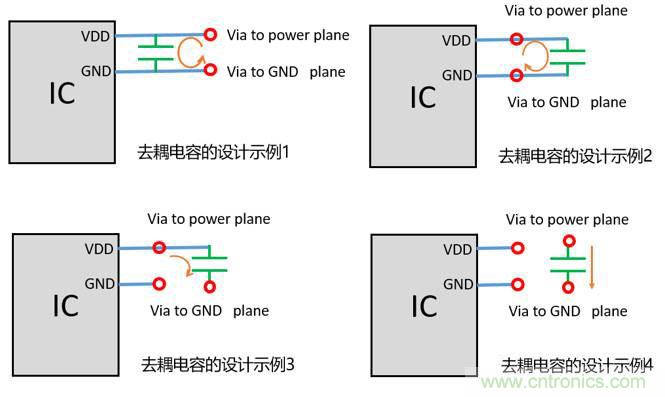

图例1是最常见的做法,VDD和GND PIN脚拉出来,并上电容,再打孔到各自的层。看起来好像是没啥问题。

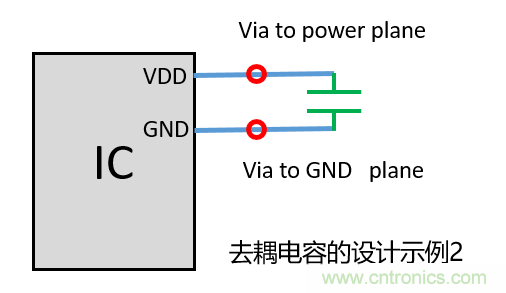

图例2是把过孔打在了的出来的两根线上,这个好像也有好多人做呀。

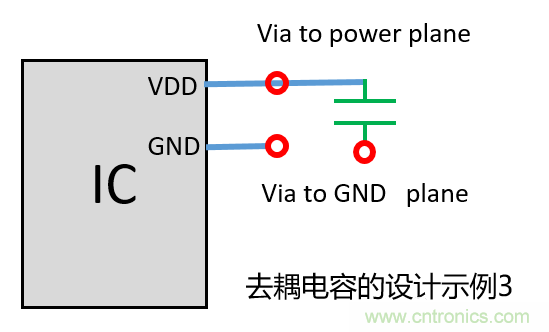

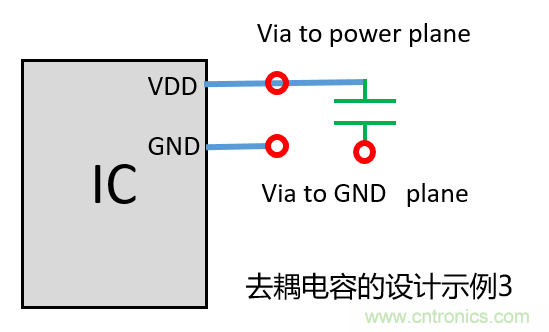

图例3,把回流的GND线打断了,GND的脚和去耦电容的GND直接打到了GND平面上,介个,介个,想法有点另类,貌似好像不错的样子。

图例4就更历害了,VDD和GND两个直接打孔到对应的平面,在附近的位置打孔上来再放一颗去耦电容。完美!

四个图放完之后,有没有发现什么好玩的地方。仔细想想,哪种摆放最好?是基于什么考虑的?

图例1和图例2有一个去耦电容组成的小小环路。

图例3稍好一些,环路较前两者更小一些。

图例4霸气侧漏,几乎是最小环路了。

其实这篇有点接昨天的Return Path的味道。细微之处显功夫,对于环路的控制,EMC工程师需要练就火眼金睛,才能在未来的整改中省下必要的时间成本。

以上内容转载自电磁兼容小小家。

推荐阅读: