【导读】当前许多精密模数转换器(ADC)具有串行外设接口(SPI)或某种串行接口,用以与包括微控制器单元(MCU)、DSP和FPGA在内的控制器进行通信。控制器写入或读取ADC内部寄存器并读取转换码。SPI的印刷电路板(PCB)布线简单,并且有比并行接口更快的时钟速率,因而越来越受欢迎。而且,使用标准SPI很容易将ADC连接到控制器。

一些新型ADC具有SPI,但有些ADC具有非标准的3线或4线SPI作为从机,因为它们希望实现更快的吞吐速率。例如,AD7616, AD7606 和 AD7606B系列有两条或四条SDO线,在串行模式下可提供更快的吞吐速率。AD7768, AD7779和AD7134系列有多条SDO线,用作SPI主机。用户在设计微控制器SPI以配置ADC和读取代码时往往会遇到困难。

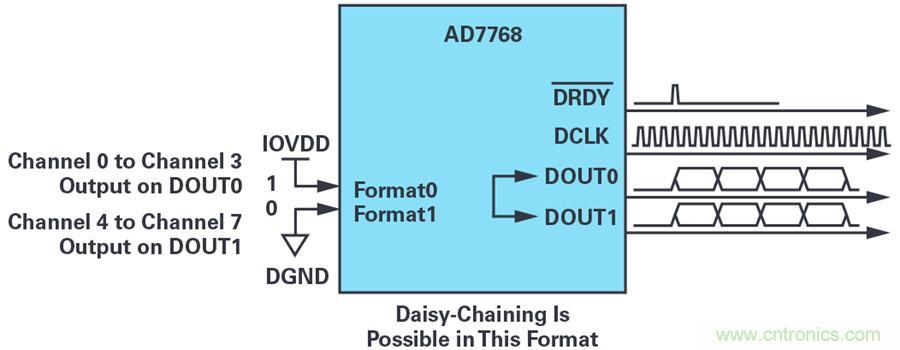

图1. AD7768用作串行主机,具有两个数据输出引脚(14001-193)。

与ADC的标准MCU SPI连接

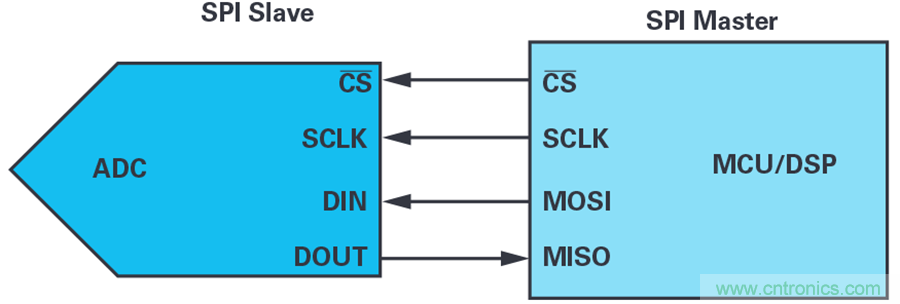

SPI是一种同步、全双工、主从式接口。来自主机或从机的数据在时钟上升沿或下降沿同步。主机和从机可以同时传输数据。图2显示了典型的4线MCU SPI接口连接。

图2. 与ADC从机的标准MCU SPI连接。

要开始SPI通信,控制器必须发送时钟信号,并通过使能 CS 信号(通常是低电平有效信号)来选择ADC。SPI是全双工接口,因此控制器和ADC可以分别通过MOSI/DIN和MISO/DOUT线同时输出数据。控制器SPI接口允许用户灵活选择时钟的上升沿或下降沿来采样和/或移位数据。为了在主机和从机之间进行可靠的通信,用户必须遵守微控制器和ADC芯片的数字接口时序规范。

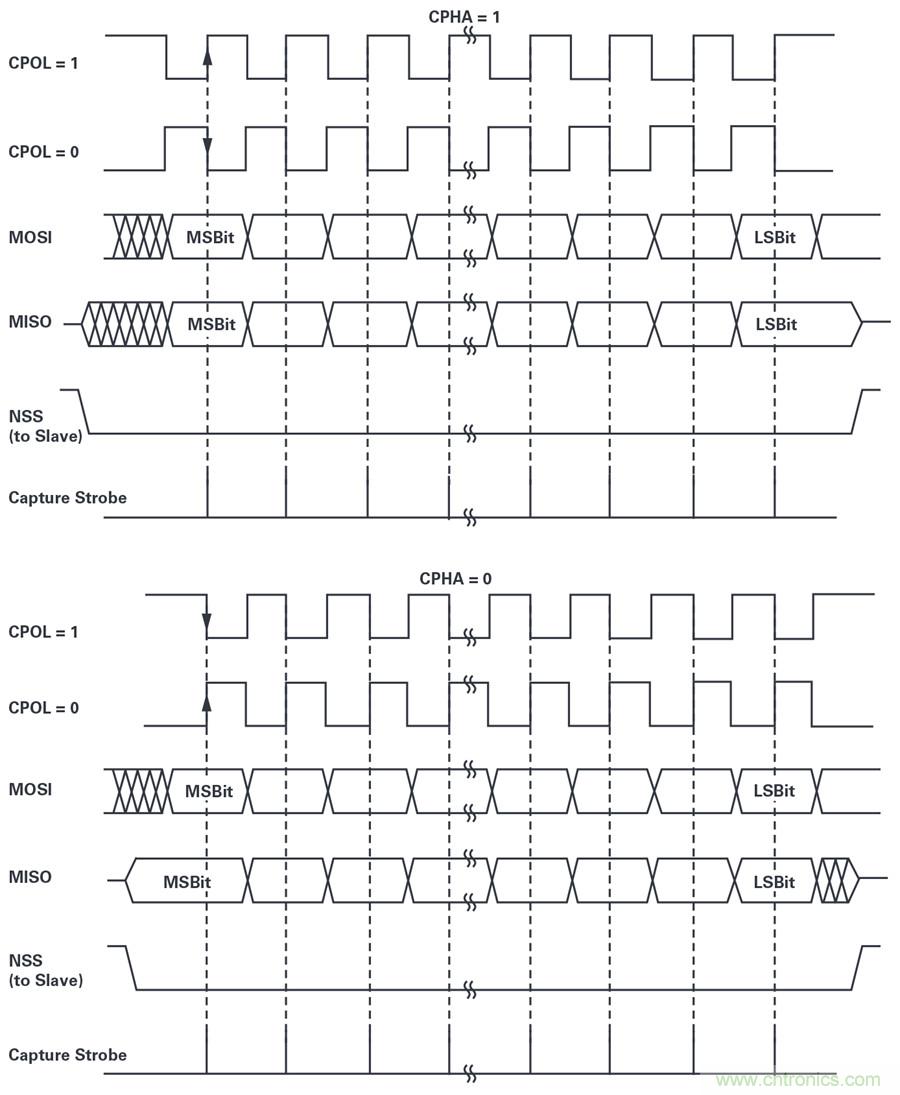

图3. SPI数据时钟时序图示例。

如果微控制器SPI和ADC串行接口具有标准SPI时序模式,那么用户设计PCB布线和开发驱动器固件不成问题。

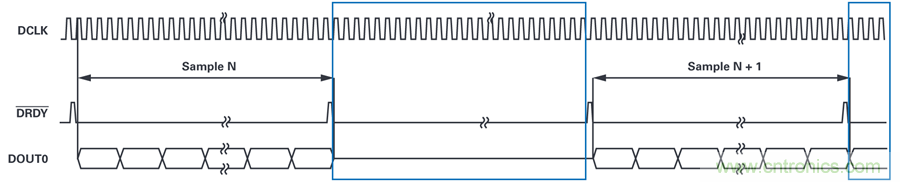

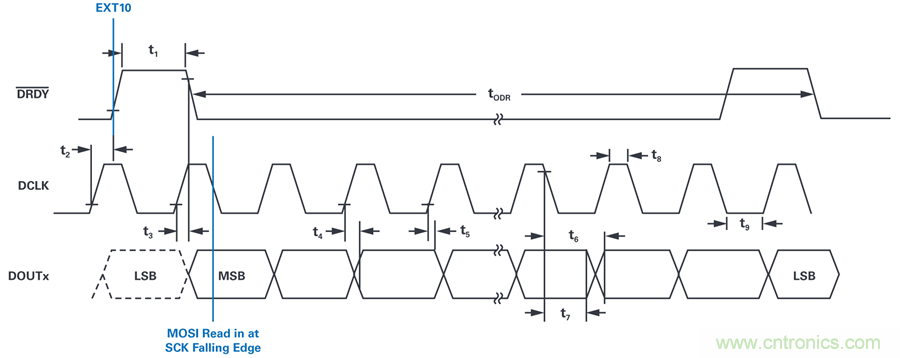

但是,有些新型ADC的串行接口端口不是典型的SPI时序模式。MCU或DSP似乎不可能通过AD7768串行端口(一种非标准时序SPI端口)读取数据,如图4所示。

图4. AD7768 FORMATx = 1×时序图,仅通过DOUT0输出。

与STM32F429 SPI连接

如何操纵标准微控制器SPI以便与具有非标准SPI端口的ADC接口读取数据呢?以STM32F429微控制器读取AD7768数据为例。如图4所示,当FORMATx = 11或10时,通道0至通道7仅通过DOUT0输出 数据。在标准工作模式下, AD7768/AD7768-4 作为主机工作,数据流入MCU、DSP或FPGA。AD7768/AD7768-4向从机提供数据、数据时钟(DCLK)和下降沿帧使能信号(DRDY)。

STM32Fxxx系列微控制器广泛用于很多不同的应用中。该MCU有多个SPI端口,可以使用典型的SPI时序模式将其配置为SPI主机或从机。

AD7768/AD7768-4分别为8通道和4通道同步采样∑-∆型ADC,每通道均有∑-∆型调制器和数字滤波器,支持交流和直流信号的同步采样。这些器件在110.8 kHz的最大输入带宽下实现了108 dB动态范围,具备±2 ppm INL、±50 µV偏置误差和±30 ppm增益误差的典型性能。AD7768/AD7768-4用户可在输入带宽、输出数据速率和功耗之间进行权衡,并选择三种功耗模式之一以优化噪声目标和功耗。AD7768/AD7768-4的灵活性使其成为适合低功耗直流和高性能交流测量模块的可重复使用平台。

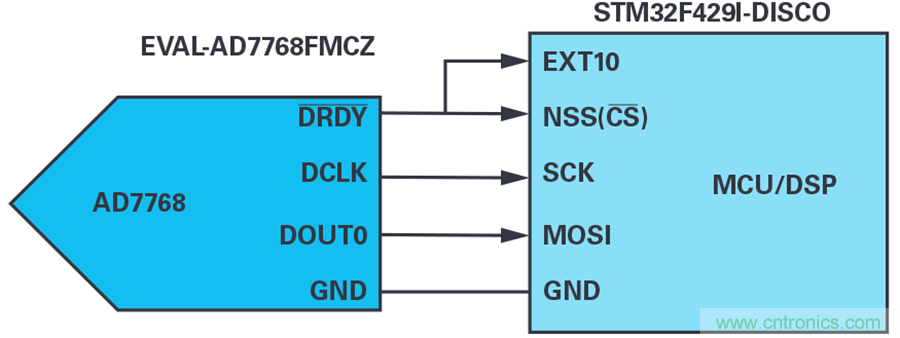

遗憾的是,AD7768的串行接口不是典型SPI时序模式,而且AD7768充当串行接口主机。一般而言,用户必须使用FPGA/CPLD作为其控制器,例如,使用32F429IDISCOVERY和AD7768评估板。变通SPI线的连接如图5所示。在这种设置下,AD7768的所有八通道数据仅通过DOUT0输出。

图5. AD7768通过DOUT0将数据输出到STM32F429 MCU SPI连接。

需要解决的问题:

● AD7768用作SPI主机,故必须将STM32F429I SPI配置为SPI从机。

● DRDY 高电平脉冲只持续一个DCLK周期,这不是典型的CS。

● 完成所有通道数据位的输出之后,DCLK继续输出,DRDY为低电平。

图6. 时序解决方案中的AD7768数据位读取。

解决方案:MCU SPI作为从机,通过一条DOUT线与SPI主机ADC接口。

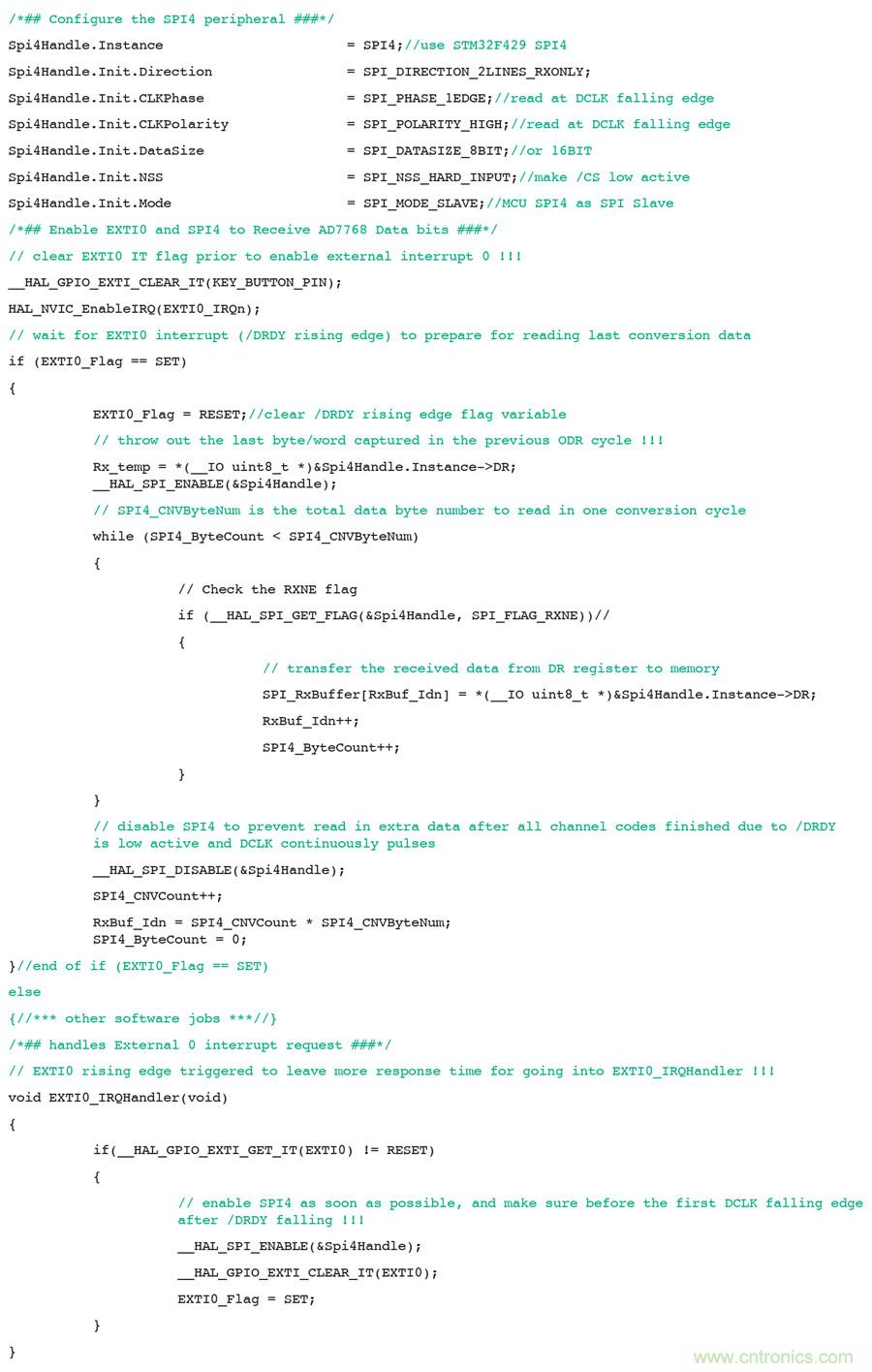

● 将STM32F429的一个SPI端口(如SPI4)配置为从机,以DCLK速率接收MOSI上的数据位。

● 将AD7768DRDY 连接到STM32F429外部中断输入引脚EXTI0和NSS (SPI CS) 引脚。 DRDY 的上升沿将触发EXTI0处理例程,以使SPI从机能够在DRDY 变为低电平之后的第一个DCLK下降沿开始接收数据位。时序设计在这里至关重要。

● 接收到通道0至通道7的所有数据后,应禁用SPI以防止读取额外的无效数据,因为 DRDY 会使SPI从机 CS 变为低电平,并且DCLK保持切换。

MCU固件开发注意事项

图7. 配SPI4外设。

当软件处于中断模式时,DCLK运行速率可以高达4 MHz,实现8 kSPS的 ODR。软件应进入中断处理程序,在一个半DCLK周期(375 ns)内启动SPI。为使软件更轻松地进入中断例程,MCU可以在DCLK上升沿读取数据,从而提供额外的半个DCLK周期时间。但是, t5 DCLK上升到DOUTx无效最小值为–3 ns(IOVDD = 1.8 V时为–4 ns),因此DOUTx上的传播延迟(>|t5| + MCU 保持时间) 应通过PCB布线或缓冲增加。

推荐阅读: