【导读】内插器可以很好地节省器件成本,在这里,可以将无源器件嵌入进来从而降低整体封装尺寸。像电容、电阻、电感这样的无源器件会占据超过50%的宝贵晶片面积,所以如果把它们从处理器的管芯上移除掉,会让集成整合更加高效。但是这就能解围3D封装的迟迟不来吗?

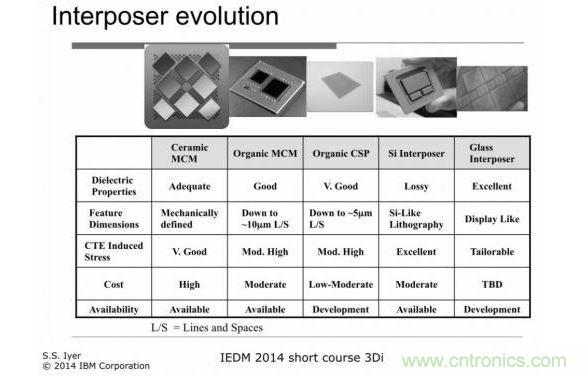

IEDM 2014会议期间提供了一些课程教材,其中,关于3D IC的幻灯片引起了我的注意。下面图中幻灯片给出了关于半导体行业中所使用的不同内插器的概述。

在这个教程中,我看到了大家关于内插器怎样改变半导体行业的一些讨论。在早期,内插器的功用在于可以使器件拥有非常大的IO数量,这样一来内插器是作为层叠平台的扩充套件形式存在的,但现在,它可以很好地节省器件成本,在这里,可以将无源器件嵌入进来从而降低整体封装尺寸。像电容、电阻、电感这样的无源器件会占据超过50%的宝贵晶片面积,所以如果把它们从处理器的管芯上移除掉,会让集成整合更加高效。这张幻灯片让我想到在一个内插器中集成无源器件(IPD)及其成本评估。我很想知道,是否会有芯片制造商染指这个领域。

我发现,2014年的IEDM大会上有一篇来自台积电的论文,在文中他们描述了采用铜镶嵌工艺在硅内插器上实现的一种MIM电容。硅内插器具有从顶部和底部两侧连接到外部器件的能力。在最顶部金属层的上面,有一个重分布的层连接到一个u型凸点上,有助于和处理器管芯的连接。而在基片的底部,一个硅通孔连接到一个C4凸块焊盘上,从而附着到封装基板上。相信这应该是目前在硅内插器上嵌入无源器件的最尖端的案例。

接下来我又搜索了关于在玻璃衬底上嵌入无源器件的资料。玻璃衬底一直在吸引大量的关注,特别是在高频应用中,因为玻璃可以在跨度很大的工作频率和温度区间内保持低损的特性。这种技术的主要玩家有佐治亚理工学院、IMEC、意法半导体、弗劳恩霍夫研究所、肖特集团、旭硝子与道康宁。所有这些公司都在玻璃内插器上进行了深入的研发,而且所有公司都在玻璃衬底上制造了无源器件,并在若干个会议中展示了他们的研究成果。大多数情况下,会在玻璃衬底上沉积一层有机体,然后在这个有机层上生产无源器件。佐治亚理工学院的网站上同样展示了采用玻璃通孔工艺的无源器件。

不过,可能是因为我搜索的资料有限,我并没有找到在一个内插器上实现的带有IPD的商业化芯片,这样的芯片中,内插器是连接到处理器上的。如果是这样,这实际上是一种2.5D的集成方案,对玻璃衬底也是如此。由于存在一些固有的制造挑战,在这个方案上,玻璃内插器落后于硅内插器。比如,你可以在硅衬底上应用所有已知的半导体行业的专业知识。采用先进的印刷技术可以将精细的尺寸图案化,在硅衬底上可以实施高密度的硅通孔,而且载体晶圆可以很容易做到厚度低于50微米。而对于玻璃而言,却很难应用这些技术,把玻璃衬底削薄也充满了挑战。然而,玻璃也并非一无是处,它也存在一些优势属性:它可以做到900毫米x900毫米,这样一来这些大型面板便可以产生非常高数量的玻璃内插基板,这比从300毫米的硅晶圆上切割出的硅内插器的数量要高出一个量级,从而降低了这些玻璃基板的整体价格。而且,玻璃的低损耗特性非常适合于高频应用,尤其是电感一类的无源器件。当然,硅和玻璃这两种材料都各有自己的优缺点。

基于研究和会议记录,很显然,半导体行业将使用嵌入无源器件的内插器以实现小型化和增加功能。这个进程可能会因为生产良率、测试和质量标准以及可靠性等问题而有所拖延。

处理器是一种高质量规格的产品,如果我们把它连接到一个实现了无源器件的内插器,可能会带来一些额外的可靠性考虑,特别是处理器和内插器的连接处的可靠性。嵌入式组件进行返工是不大现实的,所以嵌入式无源器件具有很高的良率至关重要。我们知道在系统级封装(SIP)中嵌入无源器件的重要性,所以行业将很快确定最具成本效益的2.5D集成工艺。大型芯片制造商、研究组织和OSAT成员在内插器上进行了大量的研发活动,所以,很可能,我们不用等太久就可以看到在内插器中实现IPD的商业产品成为主流。