【导读】很多人都会想这么短的线应该不会有什么问题的吧,随便拉连上就好了。可是我们要看到这个不是普通的信号,而是28G的高速信号,也许在低速信号阶段可以这样随便拉拉就好了,但到了高速信号还能这么任性吗?

最近高速先生走进千家万户(客户现场)活动进行的如火如荼,受到了邀请单位的热烈欢迎,目前我们已经在成都、西安、长沙、武汉、广州、上海、南京、杭州等地开展了部分活动,大家的赞誉让我们更有了分享的乐趣,同时我们也听到了很多宝贵的意见。大家的支持和认可是我们四处奔波的动力,也是我们继续写下去的源泉。

有人错过什么了吗?什么?你不知道高速先生的千家万户活动?还记得小陈在前几期(具体哪期忘记了,好像是码字难那一篇吧)里面说到的如果大家对高速设计有兴趣的,可以邀请高速先生亲临现场探讨对高速设计的一些理解,答疑解惑等。这个绝对不是随口一句话说说而已的哦,虽然没有官方的正式发文,但我们已经在某些地方受邀和大家互动了。在此再透露点更具体的实施细节,只要能组织5个人以上的伙伴(前提是对高速设计有兴趣或疑问的),就可以邀请高速先生去贵司现场进行交流啦(免费哈),深圳的可随约随到,话题有高速设计与仿真相关、高速板材选择、DDR3/4设计以及电源完整性设计与仿真等,约吗?

下面又到了我们案例分享的时间,事情是这样的。

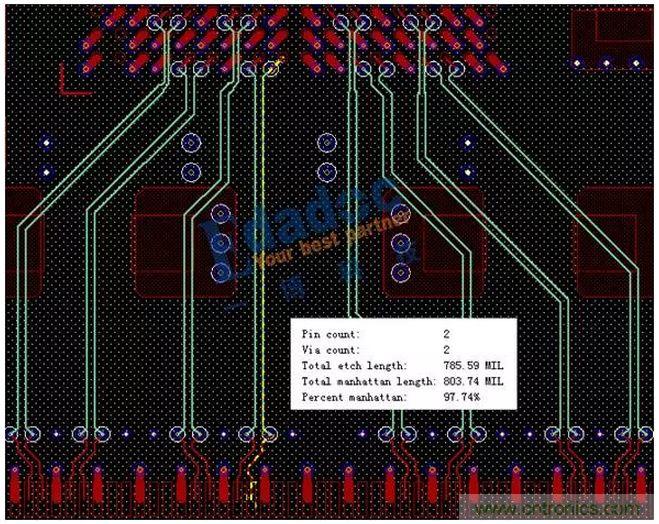

一个朋友前不久设计了一款28G-VSR协议的板子接光模块,光口连接器采用的是CFP2的表贴连接器,由于PHY芯片到光口连接器距离很短,所以当初设计的时候就直接从芯片打孔连线过来,没有经过任何特殊的处理,最后板上走线总长度约800mil,如下图一所示。

图一

很多人都会想这么短的线应该不会有什么问题的吧,随便拉连上就好了。可是我们要看到这个不是普通的信号,而是28G的高速信号,也许在低速信号阶段可以这样随便拉拉就好了,但到了高速信号还能这么任性吗?

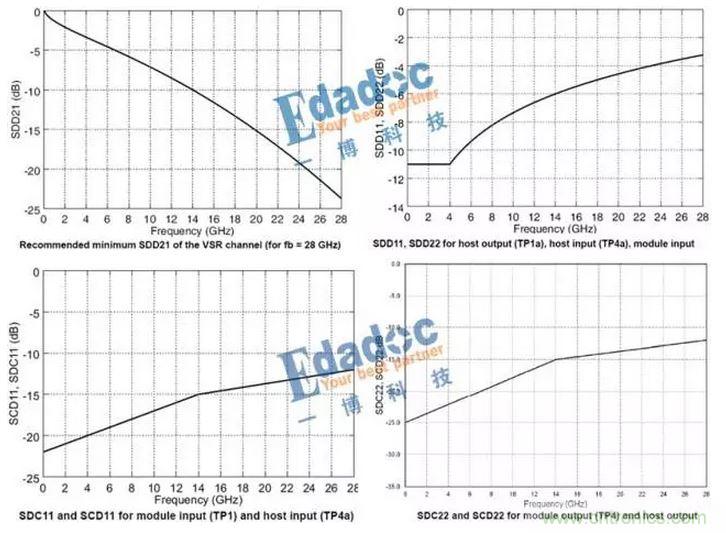

我们还是先来看看28G-VSR协议里面到底定义了通道的哪些东西吧,如下图二所示,有插损、回损及模态转换的一些无源要求。

说到这里,有些人可能已经猜到了这个设计最终的结果,既然是案例,当然是有问题的,最后的结果是运行过程中经常出现一些莫名其妙的误码。