【导读】本文分析讨论了生长前氢气蚀刻时间和缺陷密度之间的关系。事实上,透过发光致光和光分析方法,我们发现层错形式的外延层缺陷和表面缺陷的数量随蚀刻时间增加而增多。增加氢气蚀刻时间后,衬底位错变大,外延层缺陷数量增多。

碳化硅(SiC)在大功率、高温、高频等极端条件应用领域具有很好的前景。但尽管商用4H-SiC单晶圆片的结晶完整性最近几年显着改进,这些晶圆的缺陷密度依然居高不下。经研究证实,晶圆衬底的表面处理时间越长,则表面缺陷率也会跟着增加。

碳化硅(SiC)兼有宽能带隙、高电击穿场强、高热导率、高载流子饱和速率等特性,在大功率、高温、高频等极端条件应用领域具有很好的前景。尽管商用4H–SiC单晶圆片的结晶完整性最近几年显着改进,但这些晶圆的缺陷密度依然居高不下。

经研究证实,晶圆衬底的表面处理时间越长,则表面缺陷率也会跟着增加。表面缺陷严重影响SiC元件品质与矽元件相比,碳化硅的能带隙更宽,本征载流子浓度更低,且在更高的温度条件下仍能保持半导体特性,因此,采用碳化硅材料制成的元件,能在比矽元件更高的工作温度运作。碳化硅的高电击穿场强和高热导率,结合高工作温度,让碳化硅元件取得极高的功率密度和能效。

如今,碳化硅晶圆品质和元件制造制程显着改进,各大半导体厂商纷纷展示了高压碳化硅解决方案,其性能远超过矽萧特基势垒二极体(SBD)和场效应电晶体(FET),其中包括阻断电压接近19kV的PiN整流管;击穿电压高于1.5kV的萧特基二极体;击穿电压高达1.0kV的 MOSFET。

对于普通半导体技术特别是碳化硅元件,衬底材料的品质极其重要。若在晶圆非均匀表面上有机械性紊乱区和氧化区,使用这些晶圆制造出的半导体元件,其产品性能将会受到影响,例如重组率提高,或者在正常工作过程中出现无法预见的性能降低现象。商用碳化硅晶圆需要机械抛光处理,晶圆表面容易被刮伤,经常看到晶圆上有大量的刮痕。

过去的研究报告证明,如果在外延层生长前正确处理衬底表面,晶圆衬底表面上的缺陷将会大幅减少,这是生长高品质外延层的关键所在。我们知道,氢气蚀刻方法可以去除数百奈米的体效应材料,从而改善晶圆表面的缺陷问题。

S. Soubatch等科学家研究了在1,400~1,600℃温度范围内氢气气相蚀刻方法对零偏4H-SiC(0001)晶圆的形貌和结构的影响。在1,600℃高温时,两种不同的蚀刻缺陷比较常见,分别是在台阶流程式蚀刻期间形成的缺陷,以及结构性蚀刻缺陷。

前者包含大阶梯和全晶包高度台阶,后者则以螺型位错为典型。最好的表面形貌是有一系列等距台阶的区域,生长在1,400℃。

C. Hallin等科学家研究了采用氢气和氢丙烷蚀刻系统的4H-SiC和6H-SiC衬底表面原位制备方法。研究发现,蚀刻后4H零偏表面更加不规则,有大台阶区和蚀坑,可能原因是在缺陷区蚀刻速率较高;与表面平行的微管和晶粒边界变大,形成三角形蚀坑,表面渗有微管和其它位错。然而,我们在4H氢气蚀刻晶圆上看到更宽的带状缺陷,即层错。透过在氢气蚀刻流程增加丙烷,可以取得最佳的蚀刻条件,可去除刮痕而不留下任何矽滴痕迹。

该实验研究了衬底表面的氢气蚀刻时间对4H-SiC外延层缺陷的影响,同时还用AFM分析法研究蚀刻时间对外延层表面的影响。

表面处理时间与缺陷率呈正函数关系

本文利用一台商用低压力热壁化学气相沉积(LP-CVD)反应器,将蚀刻时间扩至正常生产所用时间的三倍,观察研究生长前蚀刻时间对同质外延层的影响。经过检查与分析发现,蚀刻时间与缺陷率之间关系明显。此外,汞探针CV和FT-IR测量结果证明,掺杂和晶圆厚度均匀性也与蚀刻时间有关系。

该实验使用反应器完成同质外延层生长,透过SiH4/C3H8系统分别供给矽和碳。载气和外延层生长还原剂使用高纯度工业级氢气气体;添加10%的氮气气体充当掺杂剂。本实验中使用的反应器是东京威力科创出品的商用低压力热壁化学气相沉积反应器。在偏向方向4°的4H-SiC(0001)矽面n-型(~1018at/cm-3)衬底上,生长1E16 at/cm3 n-掺杂浓度的n-SiC外延层,以避免外延层上形成粗糙的马赛克图形。

本实验针对中高压二极体或MOSFET生长9.0微米薄膜外延层;操纵变因为蚀刻时间,分别使用二分之一参考蚀刻时间、参考蚀刻时间、两倍参考蚀刻时间和三倍参考蚀刻时间来研究其外延层的研究生长过程;掺杂浓度为1E16 atm/cm3。

KLA-Tencor Candela CS920是一个晶圆表面缺陷检查系统,可以在一个单一检测平台上实现表面探测和光致发光(PL)技术,用于检测微蚀坑、萝卜状蚀坑、彗星状蚀线、三角形蚀坑和层错等表面缺陷。透过参数不同的通道之间的交叉相关(镭射波长、表面角度、散射光幅度),实现巨集微缺陷检测和自动分类。

汞探针电容电压(Hg-CV)测量法用于评估掺杂浓度(从原级平台到顶部直径是17点)。掺杂浓度固定为1。

其他仪器方面,本实验使用傅立叶变换红外光谱仪(FT-IR)测量样品厚度。表面分析实验则使用Dimension 3100原子力显微镜(AFM)。显微镜为接触测量模式,装备一个单晶矽针尖。为取得更大的扫描区域,扫描尺寸是90×90μm2,扫描速率是1.0Hz。

生长过程中的层错(SF)是比较常见的层内缺陷,一般是在外延层生长初期开始成核(Nucleated),可能导致双极元件的正向压降变大。基面位错(BPD)是萧特基二极体层错的核心,在双极元件工作过程中扩大,导致双极元件的正向特征变差。

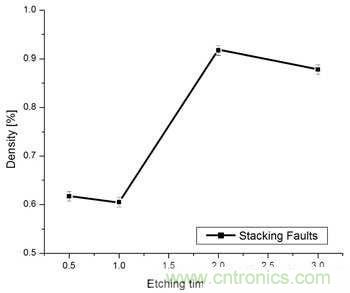

为了在化学机械抛光(CMP)后降低衬底表面粗糙度,氢气表面蚀刻是生长过程中的一个关键程序,但是会放大衬底位错现象。层错密度是氢气表面蚀刻时间的函数,我们使用PL方法分析该参数的趋势,如图1所示,当表面蚀刻时间是参考蚀刻时间的一半和三倍时,层错密度从0.6%上升到0.9%。

图1.层错密度是蚀刻时间的函数,随蚀刻时间增加而上升。

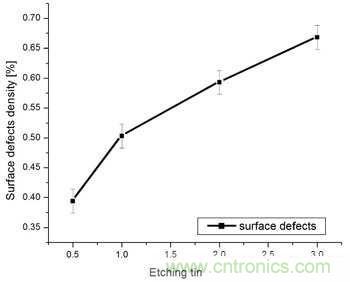

我们观察到,表面缺陷密度与蚀刻时间具有相同的函数关系。如图2所示,表面缺陷密度随着氢气蚀刻时间变长而升高。衬底表面蚀刻时间延长导致衬底位错严重,结果在外延层出现更多的表面缺陷和层错。

图2.表面缺陷密度与蚀刻时间呈函数关系。

氢气蚀刻连带引发外延层缺陷 阶褶密度明显上升

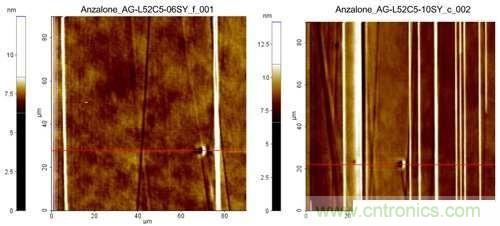

我们发现,氢气蚀刻制程可以改进表面形貌,但同时也在外延层上引起不同类型的微阶褶(SB)和整体阶褶现象。AFM表面粗糙度分析表明,阶褶会影响对样品表面均匀性。两个样品都显示一个约6nm高、1μm宽的阶褶。图3显示了x0.5(左图)和x3(右图)样品在阶褶密度上存在明显差异。

图3.不同蚀刻时间会在晶圆表面留下不同程度的阶褶。图左的蚀刻时间为二分之一参考时间,图右为三倍参考时间。

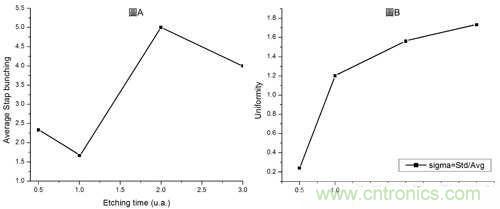

图4a和图4b分别描述了阶褶数量和表面均匀度随蚀刻时间增加而发生的变化。具体讲,如图4a所示,阶褶是蚀刻时间的函数,随蚀刻时间增加而提高。测量值是在不同测量区的不同测量值的平均数。从这些测量值看,我们在晶圆上发现SB晶圆均匀性(Sigma/Mean)存在差异。透过延长蚀刻时间评估均匀性恶化,我们发现在x3样品内有高阶褶密度区,而x0.5样品的均匀性更好(在每个被分析部分,大约有2个阶褶)。

图4.图A为阶褶数量与蚀刻时间的关系。图B表面均匀度与蚀刻时间的关系。

本文分析讨论了生长前氢气蚀刻时间和缺陷密度之间的关系。事实上,透过发光致光和光分析方法,我们发现层错形式的外延层缺陷和表面缺陷的数量随蚀刻时间增加而增多。增加氢气蚀刻时间后,衬底位错变大,外延层缺陷数量增多。AFM分析结果显示,阶褶密度和均匀性会随着氢气表面蚀刻时间增加而提高。