【导读】"时间至关重要"——这个古老的惯用语可以应用于任何领域,但当应用于现实世界信号的采样时,它是我们工程学科的支柱。当尝试降低功耗、实现时序目标并满足性能要求时,必须考虑测量信号链选择何种ADC架构类型:∑-Δ还是逐次逼近寄存器(SAR)。一旦选择了特定架构,系统设计人员便可创建所需的电路以获得必要的系统性能。此时,设计人员需要考虑其低功耗精密信号链的最重要时序因素。

"时间至关重要"——这个古老的惯用语可以应用于任何领域,但当应用于现实世界信号的采样时,它是我们工程学科的支柱。当尝试降低功耗、实现时序目标并满足性能要求时,必须考虑测量信号链选择何种ADC架构类型:∑-Δ还是逐次逼近寄存器(SAR)。一旦选择了特定架构,系统设计人员便可创建所需的电路以获得必要的系统性能。此时,设计人员需要考虑其低功耗精密信号链的最重要时序因素。

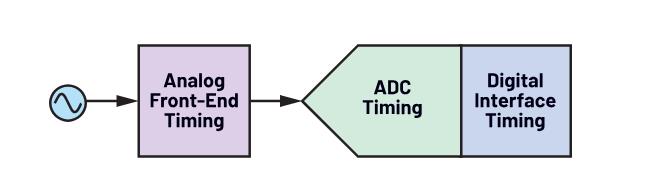

图1. 信号链时序考量

需要高速度:低功耗信号链选择SAR型还是∑-Δ型?

过去,当探索低功耗系统时,设计人员会选择∑-Δ ADC来实现对缓慢移动信号的较高精度测量。SAR被认为更适用于需要转换较多通道的高速测量,但新型SAR(如 AD4630-24 )正在进入传统上使用∑-Δ ADC的高精度领域,因此以上说法并不是硬性规定。关于ADC架构的实际例子,我们来看两款低功耗产品并考虑与ADC信号链架构相关的时序:AD4130-8 ∑-Δ ADC和 AD4696 SAR ADC,如表1所示。

表1. 超低功耗ADC

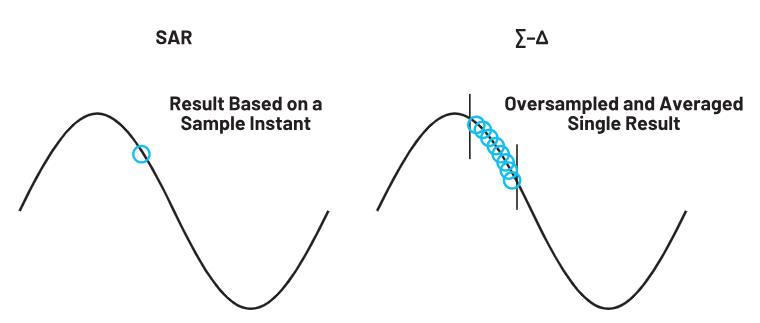

SAR转换器对输入进行采样,在已知时间点捕获信号电平。初始采样(和保持)阶段之后是转换阶段。获取结果所需的时间很大程度上取决于采样频率。

不同技术获取转换结果的方式有所不同,SAR产品文档使用的概念是采样频率(fSAMPLE),而∑-Δ产品的数据手册使用输出数据速率(ODR)。当相对于时间详细讨论这些架构时,我们会引导读者区分二者。

图2. SAR (ƒSAMPLE)与∑-Δ (ODR)的比较

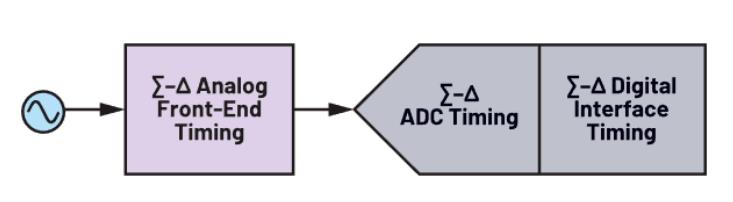

如果选择的ADC是∑-Δ型而非SAR型,则需要考虑一组特定的时序因素。查看信号链时,需要探索的主要方面是模拟前端时序、ADC时序和数字接口时序,如图1所示。

我们将分别探讨这三个模块,从模拟前端(AFE)开始。AFE可能因设计类型而异,但有一些共同方面适用于大多数电路。

图3. AFE ∑-Δ时序考量

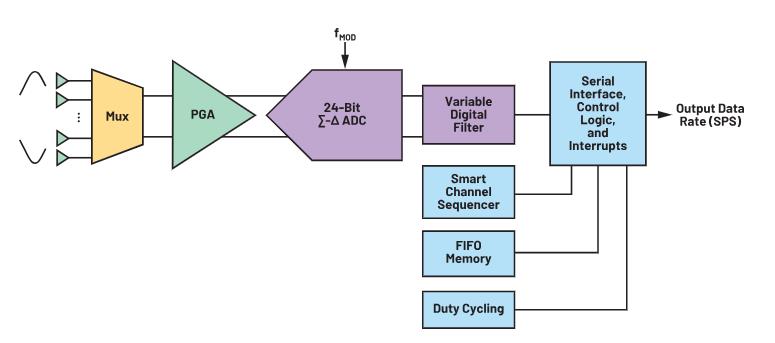

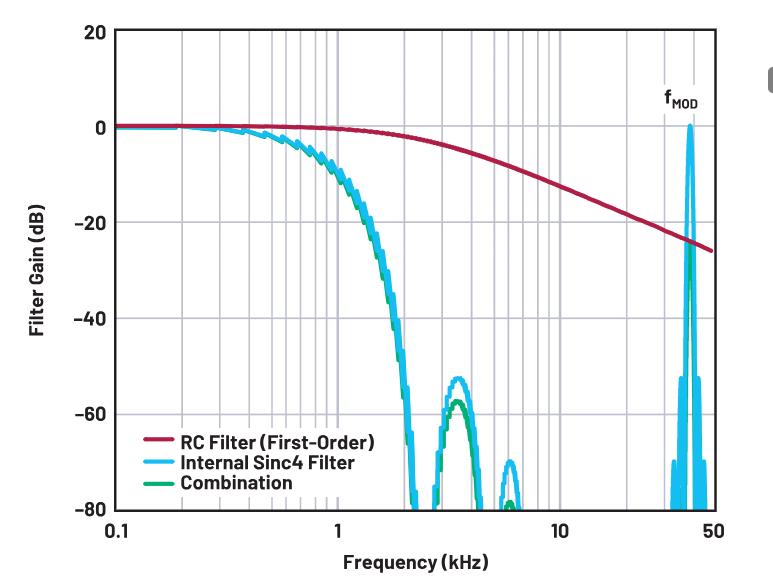

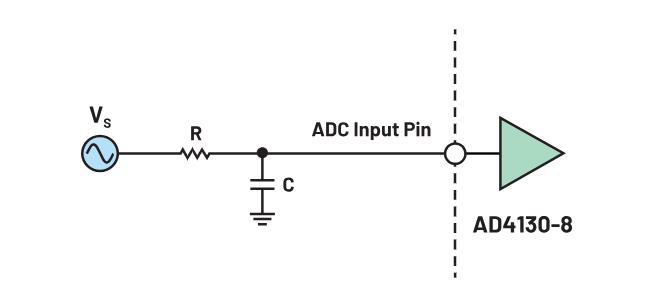

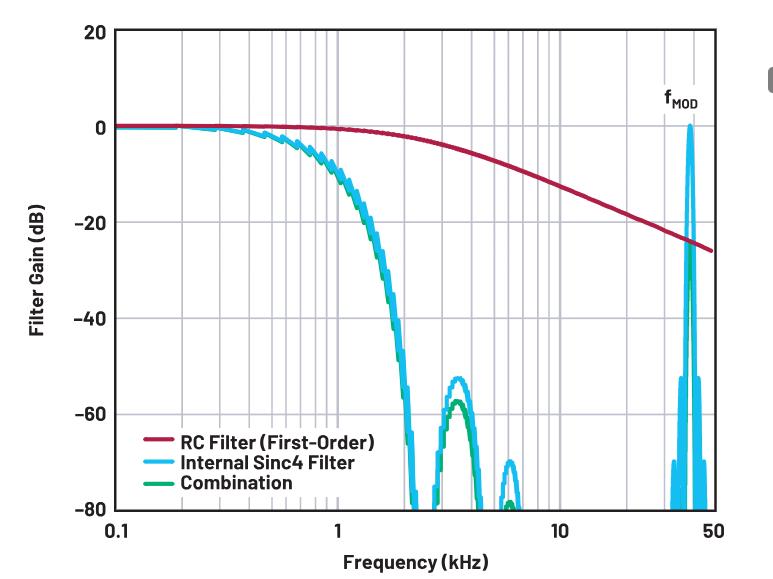

此器件的AFE包括一个片内PGA,其使模拟输入电流最小化,从而无需外部放大器来驱动输入。过采样之后的数字滤波器确保带宽主要由数字滤波器控制。AD4130-8提供多个片内sinc3和sinc4滤波器,另外还有用于抑制50 Hz和60 Hz噪声的滤波器。sinc3和sinc4数字滤波器需要外部抗混叠滤波器作为补充。该抗混叠滤波器的作用是限制输入信号的带宽量。这是为了确保噪声(例如变化率为调制器频率fMOD的噪声)不会混叠到通带和转换结果中。

图4. AD4130 ∑-Δ简化系统模块

图5. 外部和内部组合滤波的仿真

抗混叠滤波器

可以使用更高阶的抗混叠滤波器,但通常使用一阶、单极点、低通滤波器来满足要求。滤波器基于对目标信号的采样进行设计,式1决定滤波器的3 dB带宽:

根据此电容上可以看到的最大电压阶跃确定电路充电所需的时间非常重要。

图6. 一阶低通抗混叠滤波器

电容上的电压将随时间变化,变化率为

VC = 某个时间点电容两端的电压,t = 时间

图7. 响应1 V满量程阶跃变化的一阶低通滤波器建立时间

图7显示,经过4个时间常数(