【导读】如何能够实现在很多电源连接时还能减少引脚接地数量?在降低热电阻的同时,还能改进PCB设计?本文就来解析使用裸露焊盘和打地线的方式来改进PCB设计性能,同时还能有效的减少引脚数量。

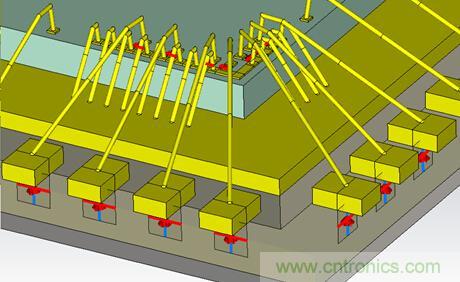

具有裸露芯片焊盘的引脚架构芯片级封装(LFCSP)和四方扁平封装(QFP)提供了一种将热量从元件传递到印刷电路板(PCB)、从而降低热阻的有效解决方案。芯片焊盘的底部是裸露而不是封装的,应作为集成式散热器焊接到PCB上。推荐的PCB设计包含一个用于裸露焊盘的焊盘。 该焊盘应包括连接到PCB上的多个接地层的通孔阵列,从而为热能提供低热阻路径。

裸露焊盘允许在封装内使用打地线,从而提供更多的灵活性和优势。 这些焊线从芯片上的接地垫直接连到芯片焊盘,而不是某一个封装引脚。外部连接接地层的裸露焊盘还构成一个低阻抗的电气路径。 有经验的设计人员都知道,高性能IC通常在相邻引脚上有电源连接和接地连接,以形成紧密耦合的低电感环路,用于传导接地回路电流。 电源和接地电流的相反极性产生的互感可以降低阻抗。

在混合信号设计中,电源和接地连接上的瞬态电流是由数字电路开关、I/O活动、模拟信号摆幅产生的。 这些瞬态会在电源上产生噪声,或耦合至器件内的敏感节点,从而降低模拟电路的性能。 打地线常用于构建紧密耦合的电流环路,无需额外的封装引脚。 空闲出来的引脚可以用于其他信号、功能和电源连接。

这些内部打地线通常缺少资料,导致用户对ADC或DAC如何实现高性能且无需相同数量的电源和接地连接感到迷惑。 某些情况下,器件可能没有任何接地引脚,因而完全依赖外部焊盘提供所有接地连接。

带打地线的LLP封装