【导读】在边缘智能与物理AI浪潮的推动下,移动终端、物联网及音视频设备等对系统级芯片(SoC)的性能与能效提出了前所未有的高要求。作为芯片的“基石”,接口与连接IP直接决定了设备的交互体验与运行效率。在2026年嵌入式世界展(EW26)上,SmartDV以“全栈IP解决方案提供商”的身份,重磅展示了其专为边缘与连接场景打造的IP矩阵。本篇章将深入剖析SmartDV如何通过覆盖音视频、存储、网络通信的全品类IP产品,凭借其高速、低功耗、易集成的核心优势,为芯片设计企业赋能,助力其在万物智联时代突破技术瓶颈,加速产品创新与落地。

例如在5G和NTN、机器人、智能汽车、超高清影音、工业智能及物联网这些正在快速普及的应用中,设备制造商们都在要求芯片设计企业提供具备高速数据传输、低功耗运行、多协议兼容的核心能力,而接口与连接IP作为通信、连接和存储芯片的“基石”,其性能直接决定了智能设备的交互体验与运行效率。

SmartDV在不久前于德国纽伦堡展览中心举办的2026年嵌入式世界展(Embedded World 2026,简称EW26)上,以“全栈IP解决方案提供商”的定位展示了汽车IP、AI与高性能计算(AI & HPC)、边缘和连接(Edge & Connectivity)三大核心IP解决方案。之前发出的两篇文章分别介绍了汽车IP和AI & HPC解决方案,这些IP解决方案获得了用户和读者们的一致认可。

本篇则聚焦边缘和连接(Edge & Connectivity)解决方案,详细阐释SmartDV是如何为越来越多的上述设备打造高速、低功耗的IP产品,精准契合行业对边缘互联与智能技术的迫切需求与严苛要求。

一站式接口IP矩阵,支撑万物互联时代终端芯片创新

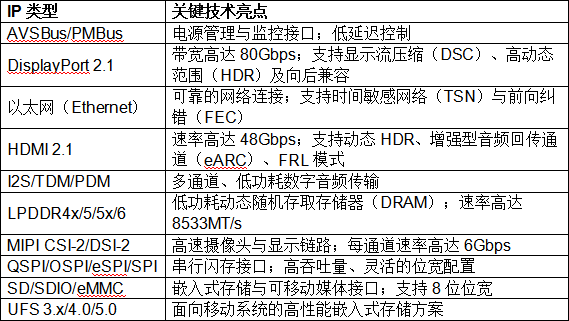

各种边缘或者端侧智能设备的兴起带来了对主控SoC与连接SoC的巨大需求,也要求这些产品针对相关的最新协议,在符合性、性能、功耗和面积(PPA)等方面进行优化,并加快设计周期来应对市场快速变化等方面的需求,SmartDV构建了覆盖音视频传输、高速存储、网络通信、音频处理、外设通信及电源管理的全品类接口IP矩阵,从而赋能各种终端设备能够实现高速、低功耗和可持续升级的特性。

基于此,SmartDV一站式提供多种设计IP和验证IP(VIP),并提供IP定制服务。

多维优势,夯实边缘互联IP底层能力

SmartDV提供专为移动设备、边缘智能、新消费电子、工业智能与物联网SoC打造了多样化的接口和连接IP产品组合,可实现符合多种协议最新版本要求的高速数据传输、先进的媒体处理与高能效边缘计算,从而助力设计人员更快地打造更智能、更高速的终端设备主控SoC。SmartDV完整的边缘与连接(Edge & Connectivity)IP解决方案的核心优势包括:

1.成熟的技术和团队:SmartDV的设计IP与VIP已获得全球领先的移动、消费电子及物联网SoC设计企业的广泛认可和信赖,此次将相关技术和产品团队结合在一起,成为芯片设计团队的一站式IP提供商和技术合作伙伴;

2. 全面的产品组合:覆盖媒体处理、存储与连接等领域内全品类设计IP和VIP,一站式满足设备互联的多元需求;

3. 卓越的性能与可靠性:针对边缘及终端SoC芯片对高速、低功耗等需求进行了优化,从而支持覆盖显示、存储与连接接口领域内的最新协议版本;

4. 领先的技术标准:基于HDMI 2.1、DisplayPort 2.1、UFS 5.0等最新行业规范打造,支持SoC设计企业紧跟前沿技术;

5. 易集成特性:可配置、经过验证的IP,使这些产品可实现快速部署;

6. 全球化技术支持:从设计阶段到落地部署,为客户提供响应迅速的全流程技术服务。

SmartDV凭借其全面且领先的边缘与连接IP解决方案,精准地回应了市场对高速、低功耗、多协议兼容芯片设计的迫切需求。通过提供从设计IP、验证IP到模拟IP的一站式服务,并结合SmartCompiler工具的定制能力,SmartDV不仅为客户提供了符合HDMI 2.1、UFS 5.0等最新技术标准的高性能产品,更构建了从前端设计到后端实现的完整技术闭环。