中心议题:

- 上升沿和下降沿取决于基顶值和基底值的确定

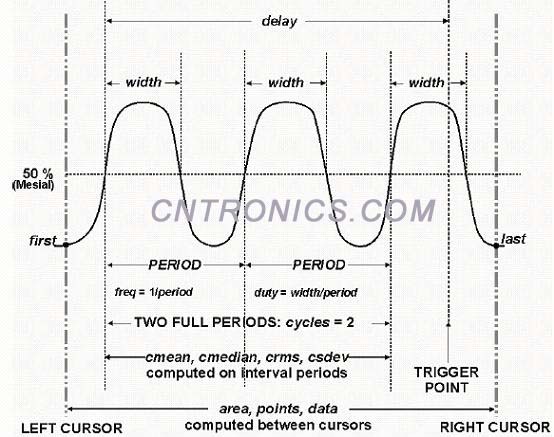

- 宽度、周期和延迟等时间参数在中间线处测量

- 合理设置水平轴测量中的Hysteresis(磁滞)能有效防止噪声或其它干扰

问题:

“在测试信号边沿的上升/下降时间的时候,跟我选择的存储深度有没有关系。比如我使用40GS/S的采样率测试PCIE CLK,如果在屏幕上显示一个时钟周期测试它的上升下降时间和我调节时基到8M的存储深度时测试到的上升下降时间有没有区别?”

回答:

你知道示波器中上升时间是怎么确定的吗?如果说是“上升沿”的10%-90%,那“上升沿”指的是什么呢?如果你会从波形的下面指到上面,那是指下面的最小值点到上面的最大值点还是下面的平均值位置到上面的平均值位置呢?这些都涉及示波器对上升时间的算法定义。

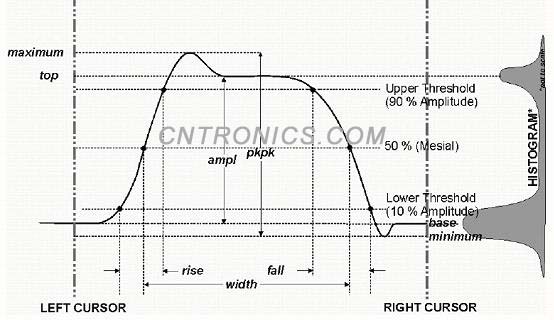

示波器里计算上升沿需要定义“算法”。IEEE定义的算法如图一所示。上升沿的确定取决于参数“top”(基顶)和“base”(基底)的确定。 正确的确定基顶和基底是正确的参数计算的基础。在分析的开始,示波器首先计算一个波形数据的直方图,时间跨度由两个时间光标之间的时间值确定,默认情况下光标是从最左边到最右边。例如,如果波形是在两个状态跃变的,那么其直方图将包括两个波峰。分析方法将尝试识别包含了最大的数据密度的这两组数据。于是,和这两组相关联的最大概率的状态将被计算出来,以决定基顶和基底。基顶相对应于上部的最大概率位置,基底相对应于下部的最大概率位置。

图一 示波器中一些常用测量参数的算法定义

顶部和底部样本数的多少会影响到基顶和基底确定的准确性。如果示波器上只一个时钟周期,顶部和底部的样本数很少,如果时钟信号上有一点点的过冲或下冲就会影响到直方图的分布的最大概率状态的确定。因此,在测量时钟我们建议屏幕上采集的周期数尽量多一些。至此,上面的问题的答案已是不言而喻的了。

值得说明的是,有时候示波器的参数下方的状态显示中有 的图标,脉冲上的一个十字表示示波器不能够确定基顶和基底,但是,测量仍然是有效的。[page]

图二 一些时间参数的定义

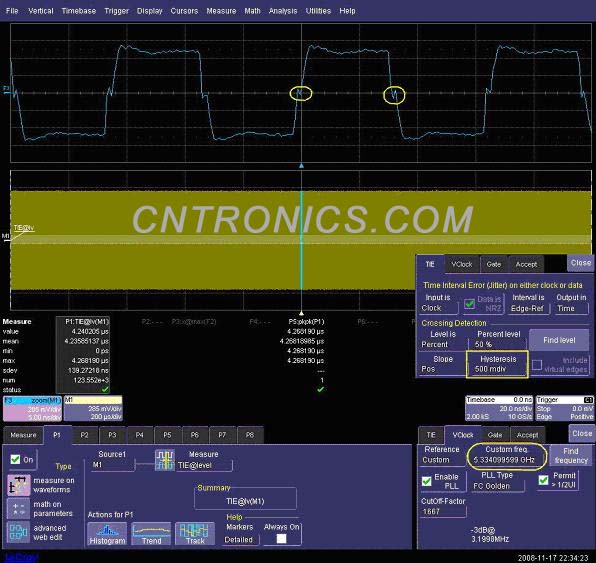

在示波器水平轴测量中有一个常被忽略的选项叫Hysteresis(磁滞)。 Hysteresis选项利用了电平之上或之下的限制,这能防止测量到噪声或其它干扰。Hysteresis的设置以milli-divisions(千分之一格)为单位指定,其设置的原则是:

1. Hysteresis 必须大于您希望忽略掉的最大噪声尖峰。

2.可用的最大Hysteresis 值小于从电平到最近的波形极值的距离。

3.除非您知道将在任何周期内发生的最大的噪声和最近的极值电平,否则就在电平的两侧留出余量。

图三所示为测试频率为61.44MHz时钟的TIE@lv参数,但PLL在计算频率时得到的结果为5.334099599GHz,这是因为缺省时Hystersis系数为500mdiv(即0.5格),示波器中将时钟上升沿和下降沿的回钩都当作了是一个个小的脉冲来计算频率,TIE@lv的测试结果也当然错了。

图三 使用TIE的缺省设置,Hysteresis值为500mdiv

图四 修改TIE的Hystersis设置