中心议题:

- WCSP 的优点介绍

- WCSP 面临的诸多挑战

- WCSP 的未来发展趋势

晶圆芯片级封装 (WCSP) 去掉了许多传统的封装步骤,例如:裸片焊接、引线接合以及芯片级倒装片 (flip chip) 连接工艺等。这种方法使半导体客户加速了产品上市进程。WCSP 应用正扩展到一些新领域,并逐渐出现基于引脚数量和器件类型的细分市场。集成无源分立 RF 和存储器件的 WCSP 应用也正扩展到逻辑 IC 和 MEMS。但是这种发展也带来了许多挑战,包括裸片尺寸和引脚数的增长对板级可靠性所产生的影响。本文将介绍我们当前面临的诸多挑战,以及集成化和硅过孔 (TSV) 技术等一些未来发展趋势。

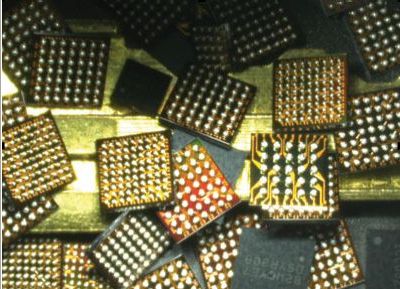

晶圆芯片级封装具有各种裸片尺寸、焊球间距和封装厚度,这些都是 WCSP 的所有关键实现因素。

WCSP 在过去十年获得了长足的发展,已成为主要尺寸封装之一。WCSP 专业技术公司已经从一些小公司发展成为大型封装分包商,以及一些拥有 150mm、200mm 和 300mm 制造能力(制造能力和赶超能力需求迅速增长)的大型集成器件厂商。由于早期的一些用户集成了无源器件和分立器件,使应用空间也获得了相当大的增长。

由于 WCSP 已经发展成熟,大型裸片和器件类型变得多样化。在整个发展过程中,始终保留着一个关键属性:在不使用倒装片底层填充 (underfill) 的情况下获得可靠性(限制裸片尺寸)。

焊球间距始终主要为 0.5mm,而大批量生产时仍为 0.4mm。0.3mm 的凸焊能力已得到证明,但其采用受到安装表面贴装技术 (SMT) 工具集功能、基板成本以及倒装片底层填充潜在需求的阻碍。

材料组合以及对工艺条件的理解能力都已得到提高。这些反过来又支持更高的可靠性,以及敏感器件更低的固化温度,例如:存储器等。

为什么采用 WCSP?

WCSP 具有许多优点,包括封装尺寸缩小、更低的成本、更高的电气性能以及比传统封装相对简单的结构等。相比倒装片板上组件,WCSP 器件一般不要求倒装片底层填充。实际上,已经得到证明的是:0.4mm 最小焊球间距和 126 引脚数的 WCSP 器件并不需要使用倒装片底层填充来满足板级可靠性要求。随着 WCSP 尺寸和引脚数的不断增加,这一优点也受到了挑战,但如果使用了正确的协同设计策略这种优点仍然可以保留。由于 WCSP向 0.3mm 焊球间距转移,很可能会要求使用倒装片底层填充来确保满足板级可靠性要求。尽管拥有很多优势,但也存在众多挑战——最明显的便是可靠性和设计挑战。

WCSP 的挑战

相当多的研究已经帮助克服了这些挑战,而 WCSP 封装已在许多新的器件类型和应用得到应用。除可靠性和设计挑战以外,其他主要的挑战还包括测试和晶圆处理。未来的一些机遇(包括 3D/TSV)将带来更多的挑战,从而需要创新型解决方案。

板级可靠性。一般而言,板级可靠性 (BLR) 测试包括温度周期变化、压降测试和弯曲测试。但是了解对组件应用可靠性的影响也很重要,包括使用实例和贴装结构(贴装至印刷线路板 (PWB) 层压板模块还是陶瓷模块)。焊盘过孔和非焊盘过孔混合结构使用的一些模块应用在获得 BLR 方面最为困难。但是,我们可以使用一些协同设计策略来提高 BLR 性能,包括层叠结构、智能焊球数量减少以及独特的重新分布层 (RDL) 设计。

由于移动设备厂商压低其印刷电路板 (PCB) 上无源组件的高度,半导体供应商也同步降低了封装高度。结果,随着焊料基准距的减小,板级温度周期性能也被降低,因为硅和 PCB 材料之间热膨胀的错配系数。在低引脚数模拟器件中,例如:音频放大器等,这些整体应力并不是一个大问题。但是,随着器件功能增加以及更多组件集成到同一块硅片中,最远焊球 DNP(到中性点的距离)会更大,从而增加 BLR 风险。

[page]

新一代 WCSP 将侧重于封装的掩模组减少。掩模减少,可以实现更短的产品上市时间和更低的封装成本。但是,必须要在不牺牲电迁移和 BLR 的情况下实现这种转变。在 WCSP 中,我们习惯上认为最必需的一层是凸块底部金属层,其会减缓焊料中锡和 RDL 之间的反应。进一步来说,扩散阻隔层将会与重分布层混合,从而除去 UBM 层。

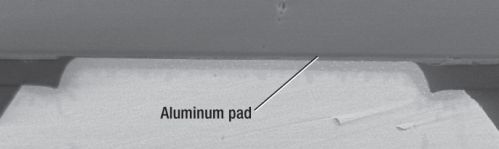

图 1 晶圆制造厂 RDL(直接位于硅铝焊盘上的凸块)

设计。WCSP 供应商在从焊盘到区域阵列范围 (area array pattern) 的什么地方构建布线所需的 RDL 存在争议。晶圆加工厂方法(请参见图 1)中,通常将一个额外增加的铝层用于这种连接。这种方法的缺点是凸块支持会占用很多的顶层金属面积。

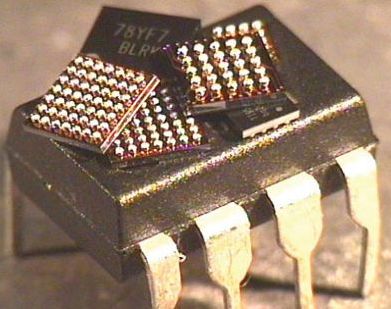

图 2 凸块晶圆厂 RDL(RDL 线迹上的凸块)

最常见是使用铜的凸块晶圆厂RDL(请参见图 2)方法。这种方法具有更高的电流密度和可靠性,因为可以使用更厚的电介质和金属层。凸块晶圆厂 RDL 还允许将出货晶圆分成不同的封装类型,包括传统的引线接合封装或者 WCSP,其为产品开发阶段理想的选择,因为可以很容易地生产电气特性的快速批量样片。相同器件可以使用不同方法时,客户会根据散热额定值、单价以及最适合其应用的尺寸来选择某种封装。未来,随着晶圆厂采用一些创新型铜工艺解决方案/结构,并增加更厚的电介质容量,业界对于从单独凸焊厂向晶圆厂转移的这一过程可能会进行重新评估。

另一个重要的挑战是了解 RDL 布局对 RF 性能的影响。作为协同设计努力的一个部分,IC 处于平面布局说明时就必须对 RDL 进行设计,旨在优化器件性能。另外,必须遵循一种结构化的协同设计方法,以保证电气性能和机械可靠性,因为组件焊球的位置也在平面布局期间确定。多种封装配置(WCSP、引线接合 BGA、倒装片 BGA)中相同硅设计的使用,也可以在结构化协同设计尝试期间确定。

随着硅节点的技术进步以及裸片尺寸的缩小,我们必须注意其他一些挑战。我们必须理解低介电常数 (low-k) 电介质的 WCSP 完整性、划片街区 (saw streets) 宽度减少以及多个晶圆厂和组装厂的整合,目的是确保 WCSP 封装的完整性和可靠性得到维持。

WCSP 的更多挑战

测试。典型 WCSP 工艺的一个常见问题是缺少最终封装测试。大多数情况下,最终电气测试都是在凸块回流后在晶圆层进行。因此,在制造过程的这一“后端”部分,必须进行高强度的目视检查,其包括激光标记、切割和封装。随着这种封装进入汽车和医疗行业,工艺控制和质量检查系统便成为必需。

晶圆承载。从合格制造到 SMT 组装的整个过程期间,正确的 WCSP 器件承载都至关重要。为了确保 WCSP 生产期间较高的组装良率,很重要的一点就是将所有过程步骤都实现自动化,从而保证操作员晶圆承载从少到无。在合格检查期间,在应力测试和电气测试之间承载器件时,使用试片板等临时载板可以帮助防止对器件的损坏。WCSP组件一般在切割成形以前以晶圆形式测试,其有助于避免承载单个封装带来的器件损坏。

随着 WCSP 封装厚度不断减小来满足终端客户高度要求,晶圆承载变得越来越重要,同时也越来越富有挑战性。更薄的 WCSP 封装意味着更薄的晶圆,其在 WCSP 制造过程期间导致晶圆弯曲变形。另外,终端客户 SMT 工艺必须能够在没有组装损坏的情况下承载薄硅片。

WCSP 的未来趋势

随着 WCSP 的发展,我们将见证 TSV 互连技术的融合,其提供有源端到裸片后端的电气连接。这种能力允许 IC 或者其他组件(MEMS、无源组件等)堆叠,从而构建起高集成度的芯片组或者系统级封装 (SiP) 系统。

[page]

针对 CMOS 图像传感器 (CIS) 和 MEMS 产品的一些 TSV 型解决方案已经投产,同时将这种技术用于那些要求高性能、低功耗、异构功能集成、小体积和低成本的产品应用很有益处。

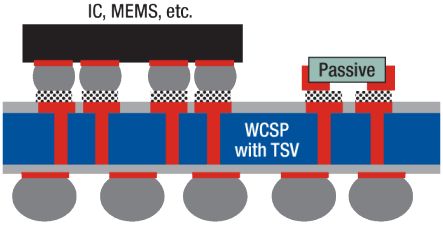

图 3 WCSP 的未来发展趋势是堆叠封装配置结构,其包括 WCSP与 TSV、无源组件、MEMS 和 IC 的组合。

图 3 描述了堆叠 WCSP 封装概念。底部 TSV 晶圆可以是一个有源 WCSP 器件(一个中介层)或者是一个集成无源中介层,而顶部则可以为一个 IC、MEMS 器件、分立无源器件或者另一个此类器件。

由于这种堆叠 WCSP 封装组装的配置结构和方法有很多种,因此在选择产品集成流程或路径以前,需要仔细考虑集成方案、可靠性问题、商业模式(供应链)和成本。就 TSV 制造来说,较普遍的流程是“中间过孔”工艺(BEOL 层中晶圆变薄以前形成的过孔),然后是“后过孔”工艺(完成包括变薄等 WCSP 晶圆处理以后形成的过孔)。

后过孔工艺成本较低,因为 TSV 和后端 RDL 同时生产。要求细间距和更小过孔直径时,中间过孔工艺具有优势;这些要求的目的是获得高性能,以及实现芯片尺寸符合要求。随后,堆叠组件的组装涉及使用引线接合、SMT 或者倒装片工艺的连接,之后是二次成型步骤(如果需要)。另外一种可能性是,最终封装仅为一种独立 TSV-WCSP,各种组件堆叠在其上面,同 POP(堆叠式封装)类似,也可以简单地将其嵌入到基板或 PCB 层压板中。

堆叠 WCSP 制造流程的重点开发领域之一是 TSV 蚀刻及电镀步骤(部分或者全部填充)、组件堆叠互连及组装方法(取决于散热预算)、二次成型材料的选择(可产生最小晶圆级和封装级扭曲变形)、兼容二氧化物沉淀和堆叠组件组装工艺的载体晶圆粘合剂的选择以及薄未模塑或模塑晶圆或者薄裸片的承载和出货。

WCSP 的小体积和高可实现引脚数将带来许多新的应用机遇。

所有这些都要求追加资金实现载体晶圆支持系统,用于接合/剥落器件晶圆或堆叠晶圆配件、芯片到晶圆 (C2W) 抓放或倒装片接合机、晶圆级模机、后端光刻以及氧化物沉积工具等。

正如任何新的封装技术一样,都会面临巨大的可靠性和可制造性挑战。在 WCSP 封装中使用倒装片底层填充和模具复合材料后,封装湿度敏感水平 (MSL) 级别不再是 MSL1。中间过程步骤期间和最终封装级的扭曲控制,对避免出现 SMT 问题至关重要。

TSV 裸片本身的强度较低,其会转化成裸片开裂或者电介质开裂和脱层问题。其他一些潜在的可靠性问题还包括 TSV 氧化物衬垫开裂、CTE 错位带来的空隙、微凸块或互连可靠性以及 RDL 层脱层或线迹开裂等。

结论

对于那些寻求更低成本和更短产品上市时间的一些客户来说,WCSP 具有明显的优势,但却并非没有挑战。随着时间的推移,WCSP 将会不断发展,对它的需求也会不断增加。我们今天面临的挑战正逐一得到克服,为新一代封装铺平了道路——包括集成技术和 3D 结构,它们将会为半导体产品增加更多的功能。

作者简介

David Stepniak 毕业于凯斯西储大学(Case Western Reserve U) ,获电子工程理学士学位,后又毕业于巴特勒大学 (Butler U.),获 MBA。他现任 TI WCSP 和 3D 封装经理,联系方式:Dallas support bldg., TI Blvd., Dallas, TX 75243 MS 3221; 214-567-9252; d-stepniak@ti.com。

Craig Beddingfield 毕业于美国密西西比州立大学 (Mississippi State U.),获电子工程理学士学位,现任 TI 无线终端业务封装开发经理。

Chris Manack 毕业于俄克拉荷马大学 (U. of Oklahoma),获电子工程理学士学位,现任 TI 高性能模拟封装开发工程师。

Rajiv Dunne 先后毕业于印度伯拉理工学院(Birla Institute of Technology & Science (BITS), India),获机械工程理学士学位;美国波士顿大学 (Boston U.),获航空航天工程硕士学位;佐治亚理工学院 (Georgia Institute of Technology),获机械工程博士学位。他现任 TI 封装开发工程师。