【导读】对于需要一系列同步模数转换器(ADC)的高速信号采样和处理应用,解偏斜和转换器的延迟变化匹配是至关重要的。围绕该特性展开的系统设计极为关键,因为从模拟采样点到处理模块之间的任何延迟失配都会使性能下降。对于交错式处理而言,样本对齐同样是必需的;在交错式处理时,一个转换器样本后紧跟另一个样本,且时间仅为一个时钟周期中的一小部分。

JESD204B 第三代高速串行转换器接口的一个重要特性,是其能够确立系统中每个转换器的确定性延迟。正确理解并利用该特性,便可在单系统中针对多个ADC创建同步或交错采样系统。

由于确定性延迟是相对较新的转换器接口特性,系统设计人员经常就如何建立、目标信号以及如何部署为同步或交错式处理等方面存有诸多疑问。下文的部分常见问题与解答针对多个与FPGA一同采样的JESD204B转换器并使用确定性延迟进行系统设计而言。

什么是确定性延迟,它在JESD204B中是如何定义的?

JESD204B链路的确定性延迟定义为串行数据从发送器(ADC或源端FPGA)的并行帧数据输入传播至接收器(DAC或接收端FPGA)并行去帧数据输出所需的时间。该时间通常以分辨率为帧时钟周期或以器件时钟进行测量。

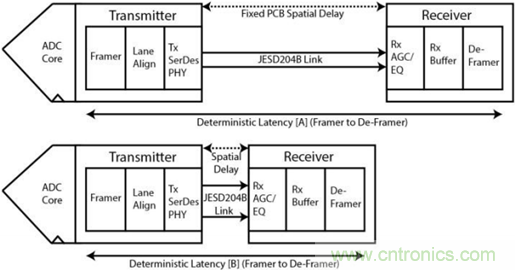

JESD204B的确定性延迟规格没有考虑到ADC模拟前端内核或DAC后端模拟内核的情况。它只基于输入和输出JESD204B数字帧的数据。不仅两个有源器件在这种延迟计算中作为函数使用,与两个器件接口的空间信号路由也将作为函数参与计算。这意味着每条链路的确定性延迟在多转换器系统中,可能较大或较小,具体取决于JESD204B通道的路由长度及其各自的延迟情况。接收器的缓冲器延迟有助于弥补路由造成的延迟差异(图1)。

图1.两个JESD204B器件之间的确定性延迟取决于三方面:发送器成帧器到输出端的延迟、空间路由延迟和输入端到解帧器的接收器延迟。来自同一个系统中两个不同ADC的数据可能各自具有独特的确定性延迟。

与简单的串行链路配置不同——比如低压差分信号(LVDS)——JESD204B接口将数据样本打包为定义帧。几个或多个样本的每一个帧边界在链路握手或初始通道对齐序列(ILAS)阶段均由来自发送器的特殊控制字符标记。更大的已定义帧群——称为多帧——在ILAS阶段同样采用相应的控制字符标记。然而,该序列完成后,便不再需要控制字符,并且可以获取链路的全带宽。帧边界和多帧边界分别与帧时钟和多帧时钟重合。

JESD204B子类与确定性延迟的关系意味着什么?

JESD204B协议的三个子类定义了链路的确定性延迟。子类0向后兼容JESD204 和JESD204A,不支持确定性延迟。子类1通 过称为SYSREF的系统参考信号支持确定性延迟。子类2通过对~SYNC信号的双重使用支持确定性延迟,并同样允许接收器初始化握手ILAS例程。精确将SYSREF与~SYNC以相对于时钟的时间关系对齐的能力表明目标系统所需的子类。

确定性延迟如何用作多个转换器的采样对齐?

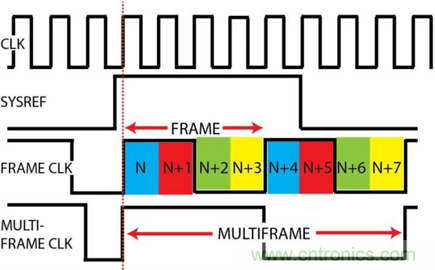

对于子类1而言,帧时钟和多帧时钟将于出现系统参考边沿(SYSREF)时在每个器件内部对齐。检测到SYSREF边沿时,这些时钟与该点时间对齐。由于这些时钟对每个器件而言都是内部的,它们在发送器内的边界可利用控制字符通过串行链路通信。

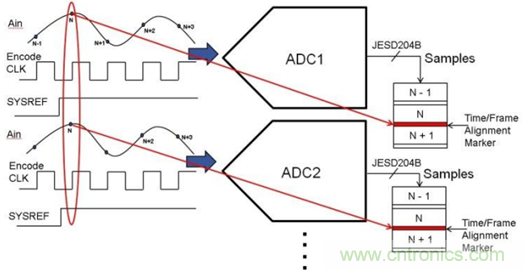

每个接收器相对其自身时钟——这些时钟具有相同的名称——并相对所有发送器间接解码发送器帧和多帧时钟位置。这使得接收器可以解偏斜相对较早到达的数据样本,从而利用缓冲器延迟,以最后到达的数据匹配链路(图2)。

图2.在JESD204B发送器内,样本于时钟锁存系统参考(SYSREF)边沿后对齐帧和多帧时钟。为直观起见,本文定义的多帧仅由8个样本组成。

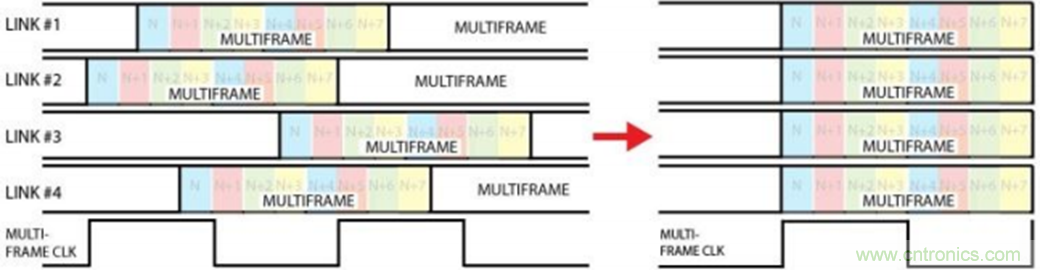

对于同步采样而言,这些数据链路可在FPGA内按时间排列。对于交错采样而言,每个链路都能以其对应的相对相位延迟进行偏置。确定性延迟可通过按时间对每个链路进行测量而加以识别,即从接收器多帧时钟边沿到每个对应链路的多帧控制字符。此处需注意,每个链路的确定性延迟必须不能超过一个多帧时钟周期(图3)。

图3.利用缓冲器延迟,来自JESD204B发送器并以多帧形式出现的样本能与多帧时钟对齐。

确定性延迟是否等同于总转换器延迟?

ADC的总延迟表示其输入一个模拟样本、处理、并从器件输出数字信号所需的时间。类似地,DAC的总延迟表示从数字样本数据输入器件直到模拟输出相应样本的时间。通常,对这两者都以分辨率为采样时钟周期进行测量,因为它们与频率有关。它与单个转换器元件内的模拟处理架构部分相关。这在原理上与JESD204B链路部署中描述的确定性延迟的定义有所不同;该定义表明其与三个元件有关。

对齐多个转换器的解偏斜预算最大是多少?

在ILAS处理阶段,发送器发送多帧控制字符,标记多帧时钟边界。接收器识别这些字符,并创建自有局部多帧时钟,与上游链路的所有发送器对齐。对于采用多个接收器的大型阵列系统,多帧时钟同样需在所有这些器件中对齐。因此,任意转换器链路的确定性延迟都不可超过单个多帧时钟周期。这是链路上的总偏斜时间预算。

多帧时钟的持续时间通常为采样时钟周期的数十倍。它甚至还能通过设置参数变量,在链路握手期间调节为更长或更短。

该特性能否在ADC或DAC上正确对齐至同样的模拟采样点?有没有其它要求?

确定性延迟按照以JESD204B成帧器时间为顺序的时间点,提供样本对齐方式。除此时间之外,ADC还将具有更多延迟时钟周期,可用来处理来自JESD204B成帧器以前的前端模拟样本。转换器供应商必须指定该时间周期位于成帧器之前,长度为时钟长度。相反,解帧器处理样本并以模拟形式输出后,DAC将需要额外的时钟周期。

在有效模拟样本数据可用以前,对齐过程需多长时间?

SYSREF边沿发送至转换器和FPGA,开启对齐过程。此事件后,需要完成多个多帧时钟周期以及ILAS序列,才能获取有效样本数据。这与许多采样时钟周期的相对时间等效。特定的持续时间可能取决于转换器内部的JESD204B内核特有确定性延迟,该数据由供应商提供。在该时间内,链路关断,不传输有效数据。在绝对时间内,持续时间将是采样时钟频率的函数。

对于系统设计而言,实现同步采样最大的挑战在哪里?

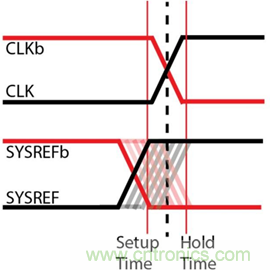

在子类1中,实现低至样本级的同步或交错处理所遇到的最大挑战之一,是在多个转换器中按序对齐SYSREF的使能边沿。此外,每个SYSREF边沿都要满足其对应采样时钟的建立和保持时间要求。这将消耗一部分可用的时序裕量。主动、独立地偏斜SYSREF和时钟之间的精细相位将有助于实现转换器上的时序收敛。

SYSREF是单次事件还是重复事件?每种情况下分别需要了解什么?

SYSREF对齐边沿可以是单次脉冲、周期信号、带隙周期信号或重复非周期信号。它将根据系统的需要,以及源端的时钟与SYSREF之间的相位偏斜时序灵敏度而定。对于重复SYSREF信号而言,帧和多帧时钟将在每次事件发生时重新对齐。然而,由于目标是保持一组对齐的时钟,重复周期SYSREF信号的使能边沿应当在多帧时钟边界下降。由于时钟应当已经在第一个SYSREF边沿后对齐,因此这样可以防止不必要的重复对齐。

周期性SYSREF信号的一个不利影响,就是可能会耦合至目标模拟信号。这便是为什么不建议始终采用周期信号的原因;仅在万不得已时才使用周期信号。如果使用了周期性SYSREF,则必须仔细地将其与ADC模拟前端正确隔离。

SYSREF偏斜调节至单时钟周期以内的方法有哪些?

理想情况下,用于每个转换器和FPGA的SYSREF和时钟可精确路由,其时序裕量满足所有元件的苛刻建立时间和保持时间要求。但随着高性能转换器的采样速度不断增长,仅通过精密印刷电路板(PCB)路由已无法始终满足时序收敛要求。不同器件的引脚间差异以及电源和温度偏差会在高速转换器阵列上产生一个相对较大的时序偏斜。可能需要高级时序调节功能来提供主动SYSREF相位偏斜。

例如,来自ADC的警报可以识别SYSREF边沿是否锁存至建立时间并保持在阻挡时序窗口中。如果确实如此,那么对于哪个时钟边沿(时钟[N]或时钟[N+1])用于时序参考将存在不确定性。取决于何处检测到SYSREF边沿,相对于SYSREF的采样CLK边沿相位在时钟源处可能存在延迟,以保持有效时序条件,满足建立和保持时间要求。

另一种方法是利用采样时钟的下一个下降沿(而非上升沿)来获取相位裕量的半周期。系统中的所有转换器均能以这种方式进行调整,前提是时钟源针对相应的SYSREF和CLK具有独立的相位调整(图4)。

图4.如需在高速下达到低至样本级的对齐性能,则满足相对于输入时钟的SYSREF建立-保持时间要求可能有难度。 在相位的早期阶段(相对于CLK)偏斜每一个SYSREF输入以防建立时间偏差的能力有助于满足系统中多个转换器的时序收敛要求。

支持子类1和子类2的转换器需要使用确定性延迟功能吗?

如JESD204B规格定义,子类1和子类2是仅有支持确定性延迟的子类。在子类1中,SYSREF信号定义确定性延迟。在子类2中,~SYNC信号定义该延迟。然而,某些转换器供应商创建了子类0部署,用来支持样本对齐的同步方案。这种情况下,不使用转换器和FPGA之间的多帧时钟对齐步骤。

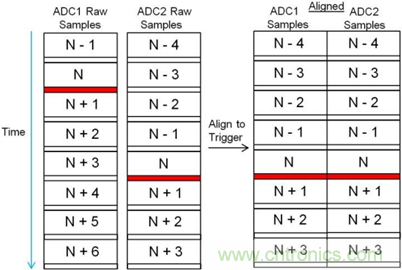

利用附加的辅助信息(称为控制位),可在样本级采用时间戳机制标记SYSREF的出现情况。与SYSREF边沿重合的每一个样本均以唯一控制位标记。在FPGA内,所有拥有此时间戳的链路可以延迟至等于最长路径然后互相对齐,与转换器之间的延迟差别无关(图5和图6)。

图5.利用SYSREF控制位时间戳,在一个FPGA处理模块内可实现子类0中的样本对齐,而与模拟输入到JESD204B输出之间多个ADC上的实际延迟差异无关。

图6.利用附加的控制位作为触发器(红色,标记为与前端模拟输入重合),则FPGA可以对齐具有不同延迟的信号链样本。

小结

虽然确定性延迟是JESD204B中较为复杂的一项特性,但若善加利用便可成为高性能信号处理系统设计中的一项强大特性。来自ADC阵列的样本可通过缓冲器延迟在FPGA内部对齐并解偏斜,从而实现同步或交错采样。JESD204B子类识别对于理解系统的时序对齐能力非常重要。时序收敛于SYSREF以及系统ADC的CLK输入引脚对于实现样本的时间对齐而言极为关键。

本文转载自亚德诺半导体。

推荐阅读: