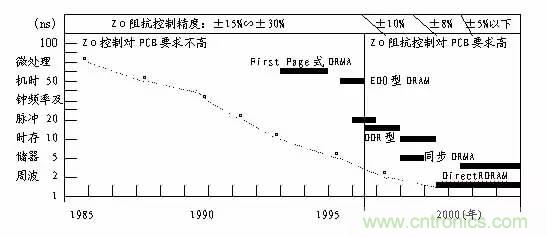

【导读】随着电子整机产品的高速化发展,这就要求所使用PCB的特性阻抗控制要求达到高精度化。以计算机高速化进展为例,就可以说明这一需求的发展趋势。

最初对PCB确立±10%的控制精度要求是由电路中800MHz频率信号的Direc Rambus 型的DRAM模块(RIMM)应用所提出的,这是为了保证计算机主机和交换机的内部电路实现更高速的动作。不仅搭载RIMM的计算机产品,而且很多的电子产品也需要基板上的电路能很好地与之匹配,一些客户相应使用的PCB板件的特性阻抗控制精度不在局限于原来的±15%或±10%,有的阻抗控制精度要求提高到±8%甚至±5%,这对PCB制造厂来说确实是很大的挑战。本文主要针对如何满足客户严格的阻抗控制精度要求方面进行阐述,希望能对PCB制造业同行有所帮助。

阻抗控制精度分析

一般多层板的传输线系统要达到60±10%Ω还算容易,但要达到75±5%Ω,甚至50±5%Ω时就会有点难度,误差5%即使对于技术规格要求较高的应用而言也是不常见的,但还是有一些客户对阻抗控制精度提出了±5%的要求,现举例来说明。

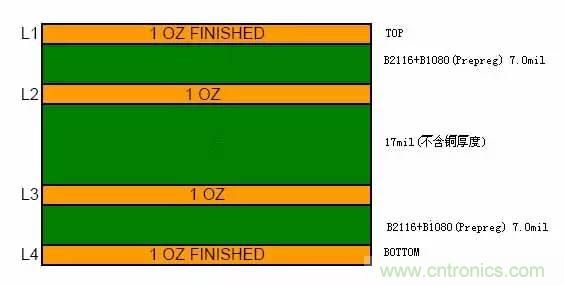

以下是我司生产的一种板件,该板的要求:4层板,完成板厚1.0±0.10mm,板材采用FR4,客户有指定的叠层结构,见下图

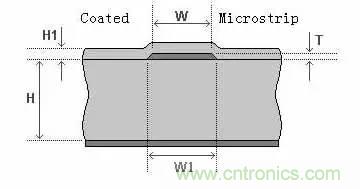

其中TOP层有单线阻抗要求,参考层为第2层,其中单线阻抗线宽W1要求12.0MIL,阻抗要求50±5%Ω(50±2.5Ω),其结构如下:

对于客户如此严格的阻抗控制精度要求,如何去满足?下面来谈谈我们公司是如何去进行控制的。

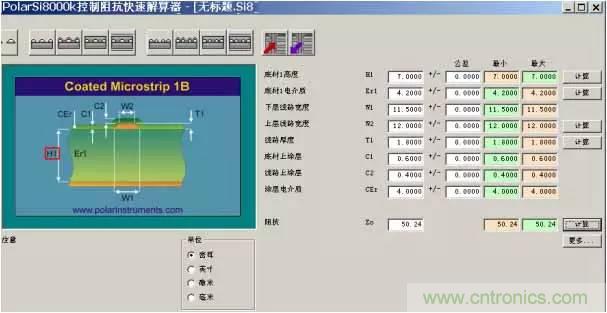

PCB特性阻抗的模拟计算

对于有阻抗控制要求的板,目前,PCB工厂比较常见的做法就是在PCB的生产拼版板边适当位置设计一些阻抗试样,这些阻抗试样具有与PCB相同的分层和阻抗线构造。在设计阻抗试样前会预先采用一些阻抗计算软件对阻抗进行模拟计算,以便对阻抗进行预测。其中英国POLAR公司开发的CITS测试系统及计算软件自1991年起已经为许多PCB制造商所使用,而且操作简单、具有强大的功能计算能力。但不管该系统功能有多强大,其计算能力及计算阻抗的场求解工具都依赖于使用“理想的”材质,模拟计算的结果与实际测量的阻抗结果之间总会存在一定的偏差。因此,对于客户阻抗控制精度要求±5%的情况下,采用计算精度比较高的软件进行较为准确的模拟预测就显得尤为重要了。为此,我们采用英国POLAR公司开发的最新计算软件Polar SI8000K 控制阻抗快速解算器进行模拟预测,由于客户要求:为了满足50±5%Ω的阻抗允许PCB厂可对叠层结构做适当调整,而阻抗线宽不可调整,为此,模拟结果如下:

根据上面的模拟结果可看出,为了满足客户50Ω阻抗要求,需将客户原有TOP层到第2层的介质层厚度9mil调整为7mil,同时,为了满足客户完成板厚,需将芯板厚度也做相应调整。结合内层线路的布线密度,调整为如下叠层结构:

PCB的生产过程控制

采用平行光曝光机进行生产

因为非平行光是属于点光源,发射的光是散射的光,因此,这些光线透过菲林底片进入感光干膜或其他液态抗蚀刻剂膜等是呈各种各样角度曝光的,经过曝光显影出来的图形与底片上的图形会有一定的偏差,而平行光是以垂直方向照射到感光干膜或其他液态抗蚀刻剂膜进行曝光的,因此,感光层上曝光出来的导线宽度会十分接近菲林底片上的导线宽度,这样,可以得到更为准确的导线宽度,从而减少这种偏差对阻抗带来的影响。

外层基铜选用薄铜箔

由于精细线路的迅速发展,薄铜箔已得到大量的发展并被全面使用,铜箔厚度已由早些年的1OZ走向1/2OZ为主,而且早也开发出1/3OZ和 1/4OZ,甚至更薄的如1/7OZ铜箔。因为较薄的铜箔厚度有利于制造和控制导线宽度及导线的完整性,从而有利于保证阻抗控制精度。由于客户对外层铜厚要求为1OZ, 因此,对于该四层板压合时外层我们选用了1/3OZ 铜箔进行压合,再经过后面的电镀后即可达到客户表面铜厚1OZ的铜厚要求,这样既满足了客户表面完成铜厚的要求,又有利于蚀刻时对导线宽度均匀性的控制。

采用铜箔通电加热压机层压

层压机的加热方式有电加热和蒸汽加热两种,而我公司所使用的是意大利CEDAL公司采用ADARA技术生产的多层真空压机,该系统利用成卷的铜箔环绕着半固化片及内层板的叠层一层一层叠板,在层压机内对铜箔通电,达到加热的效果,温度分布,整个叠板的温度分布可到达177±2°C,由于加热快,温度分布均匀,压合过程中树脂流动性比较均匀,层压出来的板的板厚平整度可达到±0.025mm,层间介质层的厚度比较均匀。

采用整板电镀进行生产

为了获得比较 均匀厚度及宽度的导线以保证阻抗在规定的公差范围内,PCB在经过孔化后是直接采用全板电镀生产的,其中电流密度进行适当降低.由于PCB 在经过孔化后直接进入全板电镀,在一定的镀液条件下,整板的制板面上接受的是均匀的电流密度,因而整个板面及孔内的铜厚是比较均匀的,这样有利于控制面铜厚度及导线宽度的均匀度(因为不均匀的铜厚度会对蚀刻均匀性方面带来不利),从而有利于对PCB特性阻抗的控制及减少其的波动性。

其他方面

当然,为了满足客户50±5%Ω(50±2.5Ω)的阻抗控制要求在蚀刻线路,丝印绿油等方面也应加以控制,以确保导线宽度及导线表面绿油层厚度的均匀性。

PCB的阻抗测量

阻抗测量通常使用时域反射计 (TDR) 来完成,TDR(时域反射计)已成为测量印刷电路板上的特性阻抗的既定技术。对于测量阻抗要求精度为±5%的特性阻抗来说阻抗测量也是非常重要的,一定要确保测量的正确性,否则会导致阻抗合格的板件误测为不合格。

测量前采用可跟踪的阻抗标准进行校正

因为用于阻抗测量的 TDR 是高精度的 RF 测量工具,在测量过程中,TDR测量要求在迹线前端与后端DC条件相同的环境下进行的,由于大多数的阻抗COUPON都未端接,因而最好采用经过可跟踪标准校正的参考空气管路。使用高精度负载电阻校准TDR可以将阻抗测量误差减少。

测量时切不可将手放在阻抗COUPON上

将手或手指放在阻抗COUPON上时其表面的阻抗结构发生了变化,其结果导致测量的阻抗下降,为此,测试人员在进行测试过程中不可将手或手指放在阻抗COUPON上。

测试时采用固定的测试夹具将阻抗COUPON固定测试

一般测试阻抗时常的做法是将阻抗COUPON直接放置在工作台面上进行测试,这都会影响测量的结果,因为工作台面具有它本身的绝缘常数,阻抗 COUPON如果与工作台面直接接触,得到的阻抗测试结果都会偏低,当然,对于阻抗控制精度要求不是很严的情况下尚可,而对于测试类似测量阻抗要求精度为 ±5%的特性阻抗时就应该采用固定的测试夹具将阻抗COUPON固定测试。

测量时检查RF线缆和探针磨损

RF 线缆和探针的使用寿命有限,用户在使用过程中会磨损,一旦RF线缆和探针破损都会影响阻抗测量结果,因此, 测量时检查RF线缆和探针磨损,以保证确保测量的正确性.

其他方面

当然,为了保证测量的准确性,在测量过程中要求测试区域附近的移动电话关闭,在测量中要求TDR阻抗测试探针与阻抗测试COUPON接触保证良好等。

结果与讨论

以下是采用TDR测试系统测试该板的阻抗测试结果,从结果可看出该板所测试的阻抗都在47.5∽52.5Ω之间,即完全满足客户50±5%Ω(50± 2.5Ω)的阻抗要求. 因此,可看出对于客户±8%甚至±5%的阻抗控制精度要求只要在生产前采用计算精度比较高的软件进行较为准确的模拟预测,结合模拟预测的结果对相应的一些参数做适当调整,在生产过程中对重点工序加以特别的控制,同时,测量时确保测量的正确性,还是可以达到的。

参考文献

(1)英国POLAR 公司 CITS500s 测试仪

(2)英国POLAR 公司 CITS25 阻抗计算软件

(3)Si8000K 软件,Polar Instruments。

(4)林金堵,PCB的特性阻抗与电磁干扰(Ⅱ),《印制电路信息》,2000.10

推荐阅读: