【导读】在AI大模型、超算集群和云原生数据中心蓬勃发展的今天,芯片内部和节点中的“数据高速公路”和“存储中枢”正成为制约处理器算力释放和节点整体性能的核心瓶颈。作为半导体IP领域的创新先锋,SmartDV在Embedded World 2026上以“全栈IP解决方案提供商”的身份惊艳亮相,精准切中这一行业痛点。继深入解析其汽车IP布局后,本文将目光聚焦于SmartDV的AI & HPC核心解决方案——通过构建高带宽、低延迟、可扩展的“数据高速公路”,SmartDV正利用其全面的高速接口与存储控制器IP组合,为下一代AI处理器与数据中心芯片注入强劲的性能基因,助力客户在算力竞赛中打破瓶颈,实现指数级的性能跃升。

本篇则聚焦SmartDV的AI与高性能计算(AI & HPC)全面IP解决方案,深度剖析其如何以高带宽、低延迟和低功耗的极致特性,助力芯片性能实现指数级提升。SmartDV提供专为下一代人工智能加速器、数据中心处理器和高性能计算的处理器和系统级芯片(SoC)而打造的全面的高速互连和存储控制器IP产品组合。SmartDV的IP可实现卓越的带宽、超低延迟和多芯片可扩展性,从而力助客户缩短产品设计周期,实现最佳的芯片性能、功耗和面积(PPA),最终以最优的总体成本实现卓越的系统性能。

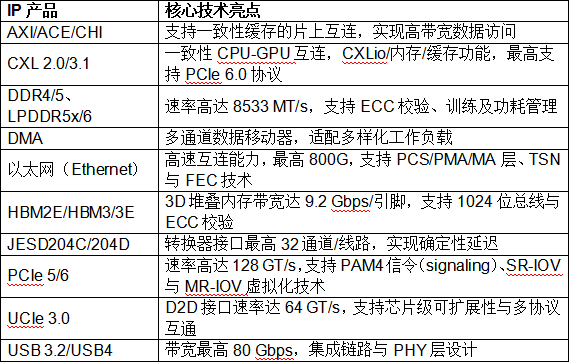

完整互联与控制IP覆盖:高速接口与互联、内存控制器及数据通路IP

SmartDV的IP产品覆盖多类关键接口与控制器,各项技术指标表现出色:

六大核心优势力助AI产业因需而变

当前,AI技术和产业自身正在高速演进和演变,业界不仅迎来了自动驾驶、物理AI和边缘AI等全新的应用场景和交互范式,而且从智算中心到边缘计算都面临着进一步降低算力成本、功耗和错误率的巨大压力,从而给AI芯片和节点设计带来了新的挑战。而SmartDV凭借AI & HPC全面IP解决方案,致力于在以下六个方面支持芯片设计团队更好地实现性能和成本目标。

1. 汇聚成熟的技术和团队:SmartDV将已广受AI加速器、HPC集群与云基础设施领域内的全球领导性企业信赖的技术结合在一起,成为芯片设计团队的一站式提供商和技术合作伙伴。

2. 全面的产品组合:覆盖互连、存储、芯片级集成IP全栈产品,使芯片集成设计的工作量大大降低。

3. 性能与可靠性:专门针对低延迟、高带宽场景深度优化。

4. 满足最新技术标准和规范:基于最新的UCIe 3.0、CXL 3.1与PCIe 6.0协议规范打造,紧跟行业技术迭代节奏。

5. 易集成特性:可配置、经过验证的IP,使这些产品本身亦可实现快速部署。

6. 全球化技术支持:从设计阶段到落地部署,为客户提供响应迅速的全流程技术服务。

从AI大模型的训练集群到数据中心的高效运维,从面向科研的高性能计算到实现万物智联的边缘计算,算力的竞争也离不开数据传输效率的竞争。SmartDV的AI& HPC解决方案并非简单的单一IP集合,而是一套建立在设计IP、验证IP与模拟IP(系列PHY)坚实底座之上的全栈技术体系,从而使得SmartDV能够从逻辑层、物理层到验证层全方位赋能AI & HPC芯片设计,真正实现“可快速落地、可高度信赖、可即刻量产”的全栈交付。

从逻辑层的协议规范到物理层的信号完整性,SmartDV通过六大核心优势,为客户构建了从设计到量产的完整闭环。在算力需求呈爆发式增长的今天,SmartDV凭借其“可快速落地、可高度信赖、可即刻量产”的交付能力,不仅解决了数据传输的效率难题,更为芯片设计团队提供了应对未来不确定性的坚实底座。选择SmartDV,即是选择了在AI与HPC赛道上实现性能、功耗与成本最优平衡的战略伙伴。