中心论题:

- DC-SIR滤波器介绍

- 滤波器设计

- 滤波器级数和初始尺寸的选取

- HFSS仿真分析

解决方案:

- 使用SIR结构设计滤波器

- 在Ansoft HFSS中建立三维模型,分别仿真单腔的谐振频率、外部品质因素Qe和耦合系数k

引言

微波滤波器是微波系统中的关键元件,针对不同的应用领域和场合,它可采用多种不同的结构来实现。通常,当滤波器通带的相对带宽大于15%时可以采用交指型结构,大于5%时可以采用梳状型结构,而小于5%时则采用同轴型结构。由于实际项目对滤波器的体积有特殊要求,因而采用 g/4的DC-SIR结构。该结构的滤波器具有Q值高、插损小、体积小、带外抑制好以及方便控制杂散谐振频率等优点,可应用于许多场合。

普通SIR(Stepped Impedance Resonators)滤波器中心导体内部没有电磁场,即这些空间对增加Q值没有任何意义,而在设计中为了调试方便和减小谐振器的重量,在谐振杆开路端增加了一个圆柱形的空腔。

为了简化设计,首先忽略双同轴腔体滤波器谐振杆低阻抗部分空腔的影响,通过计算得到普通SIR滤波器的基本尺寸参数,然后在Ansoft HFSS场仿真软件下仿真优化该空腔的尺寸及谐振杆低阻抗部分的长度,并计算耦合系数与耦合窗、外部品质因素Qe的关系,最后整体仿真优化并加工调试。

DC-SIR 滤波器介绍

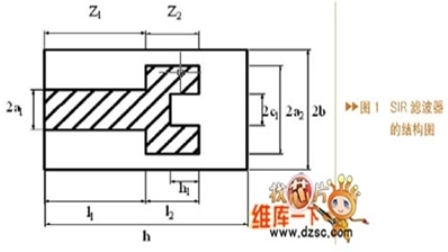

DC-SIR (Double Coaxial Stepped Impedance Resonators)滤波器的内部谐振器由两种或两种以上不同特征阻抗的同轴传输线结合而成,并且在谐振杆的低阻抗部分开了一个空腔。与普通的滤波器相比它具有更小的体积。通过选择较小的阻抗比RZ(不同特征阻抗的比值)可以无限地缩短DC-SIR谐振器的长度,减小RZ也可以使杂散谐振频率远离基本谐振频率。图1为DC-SIR滤波器的单腔结构图。

图中,a1为谐振器高阻抗部分的半径,a2为低阻抗部分的半径,b为谐振腔的边长之半或同轴腔的外径(具体视外腔为矩形腔或圆形腔而定),h为谐振腔的长度,c1为空腔的半径,h1为空腔的深度,l1和l2分别为高低阻抗谐振器的长度,它们分别对应于电学长度θ1和θ2。

这种结构的谐振腔的谐振条件为:Ln0=4(arctan Rz)/π (1)

其中Ln0为归一化谐振器长度。在设计滤波器时可以通过选择阻抗比Rz或归一化谐振器长度来确定另外一个参数。如果不考虑开路端边缘电容和阻抗不连续性的影响,在设计时可以取l1和l2的长度相等,谐振器的总长为l1+l2。在实际设计中首先需要考虑阻抗不连续性和开路端边缘电容的影响,通过计算传输线接合面不连续性电容,确定谐振杆长度,并在此基础上缩短l2的长度以达到消除开路端电容影响的目的。然后考虑谐振杆空腔的影响,在前面计算的基础上通过仿真优化确定空腔的尺寸及谐振杆低阻抗部分的长度。

滤波器设计

本文使用SIR结构设计滤波器,其通带3976±20MHz内S21<1.5,S11>15,带外抑制大于40dB(3976±60MHz)。滤波器的尺寸要求为:长×宽×高<50mm×15mm×15mm。

滤波器级数的选取

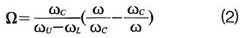

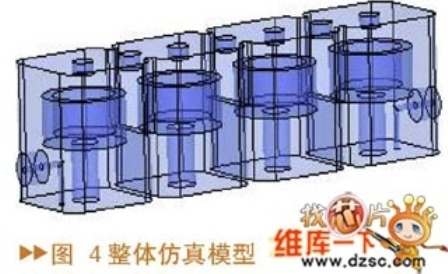

利用带通滤波器的频率变换公式:

其中ωU和ωL分别为通带的上、下截至频率,ω_{C}=\sqrt{ω_{U}ω_{L}},ω=ω_{C}±60MHz。计算得2.96或3.02;查表可得滤波器的阶数为n=4。滤波器低通原型归一化元件值为g0=1,g1=1.1088,g2=1.3061,g3=1.7703,g4=0.8180,g5=1.3554。

滤波器初始尺寸的选取

通带中心插损L0可以通过如下公式得到:

经计算可以确定未加载Q0值为1465。

考虑到实际加工中滤波器的外壁厚度等因素,暂时设定谐振腔长度为11mm,谐振杆初始长度为10mm,空气腔型SIR结构的归一化谐振器长度由下式决定:Ln0=lT/l0=10/18.86=0.53

其中lT为谐振器长度,l0为1/4波长。由公式(1)可得,RZ=0.195。由归一化Q值与线阻抗的关系图可以看出Q0=0.8QCM,当滤波器材料为铜的时候:QCM=2670b f0=5324b

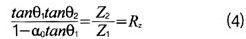

故可计算出b=3.4mm。在实际中必须考虑通带边缘插损加大和导体表面粗糙度等使无载Q值减小的实际因素,在设计时无载Q值必须留有足够的余量。在本文中,外导体选择b=5mm,即边长为10mm的矩形腔,根据阻抗比RZ和归一化Q值与线阻抗的关系图,用Agilent Appcad软件可以计算得到同轴腔的高、低阻抗段的内径为4mm和1.3mm。由J.R.Whinnery的结论可知阻抗不连续性电容为0.33pF,为消除其影响可用包含了传输线接合面不连续性电容的SIR谐振计算公式,修正谐振器长度。

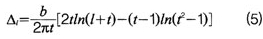

式中α0=ω0CdZ1,ω0为角谐振频率,取θ1=θ2计算;经计算得到l1,l2长为4.6mm。为消除开路端边缘电容影响可由公式修正低阻抗部分l2的长度

经计算Δl=0.83mm≈0.8mm,故谐振器长度为l1+l2=4.6mm+3.8mm=8.4mm。

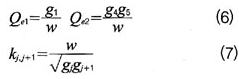

将前面的滤波器归一化低通元件值代入公式(6)和(7):

式中w为相对带宽。

经计算可得Qe1=Qe2=110.2;k1,2=k3,4=0.0836;k2,3=0.066

HFSS仿真分析

在Ansoft HFSS中建立三维模型,分别仿真单腔的谐振频率、外部品质因素Qe和耦合系数k。根据计算的结构参数,在Ansoft HFSS里面建立单腔的谐振频率扫描模型。在仿真扫描谐振频率的时候不需要加激励,在Eigenmode模式中改变谐振器顶部加载的频率调谐螺钉长度,可以调节谐振腔的谐振频率。当频率调谐螺钉长度增加时,加载的电容增大,谐振频率降低。

建立外部品质因素Qe计算模型(图2),在单腔模型中加入激励可以计算Qe,在边界设置的时候把激励在腔外的一段设置成LumpRLC边界,并且设置这段导体的阻抗为50Ω。通过扫描激励的高度和激励到谐振杆的距离可以得到期望的Qe。

建立耦合系数扫描模型(图3),建立两个谐振腔,中间通过矩形空气孔耦合连接起来,通过扫描耦合孔的宽度和深度,可以得到不同的耦合系数,具体耦合系数的计算公式为:

其中f1和f2为Eigenmode模式下的谐振频率。

在设计中,仿真扫描耦合系数时一般都要在耦合孔上面加耦合螺钉,以便设计调试滤波器时修正加工与仿真的误差。

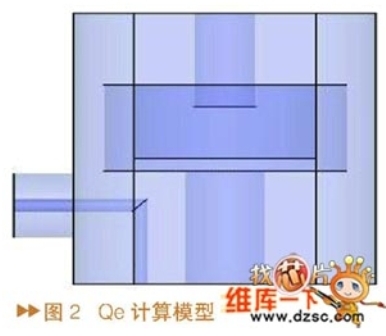

通过与前面计算的耦合系数理论值的比较,可以选择合适的耦合孔及耦合螺钉的初始值建立整体仿真模型(图4)。一般这种初始值进行整体仿真的结果与期望的滤波器指标有一定的偏差,通过调节耦合螺钉的深度、激励的位置以及频率调谐螺钉的深度可使滤波器达到期望的指标。

在该滤波器的结构实现中,选择方腔边长10mm,方腔高度11mm,谐振杆低阻抗部分半径4mm,低阻抗部分长度3.5mm,谐振杆高阻抗部分半径1.3mm,高阻抗部分长度4.6mm,谐振杆顶部空腔半径3mm,空腔高3mm。

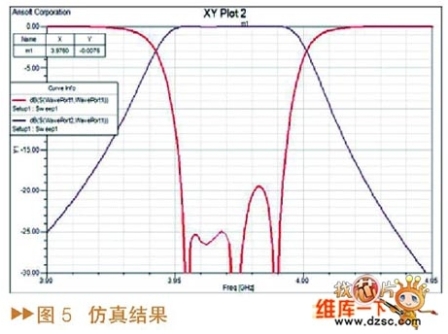

仿真结果及分析

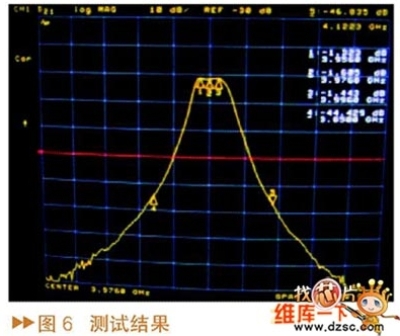

通过优化得到滤波器的仿真结果如图5所示,在仿真过程中为了提高仿真速度,全部的材料都设置成理想材料,所以仿真结果中滤波器插损为零。实际测试的滤波器的波形如图6所示,可以看出,该方法设计的滤波器实际测试的结果与仿真的结果非常吻合,能够达到指标要求。

在本文中首先忽略DC-SIR的空腔对谐振杆结构的影响,通过计算得其基本结构参数,再使用Ansoft HFSS场仿真软件对空腔的尺寸及谐振杆低阻抗部分的长度进行优化,并对滤波器的外部品质因素Qe、级间耦合系数和谐振频率等进行单独仿真,最后整体仿真,确定滤波器的最终尺寸。测试结果表明,实际滤波器指标与仿真结果基本一致,说明了该方法设计滤波器的可行性。