【导读】作为国内领先的高端PCIe SSD主控芯片和方案提供商,忆芯科技一直走在技术创新的前沿,为了满足各行业对于数据处理和存储的需求,其推出多款极具出色性能和稳定性的产品,包括支持PCIe 3.0的STAR1000P、PCIe 4.0的STAR2000、以及最新的PCIe 5.0高性能芯片STAR1500。未来随着数据传输速率和接口带宽的迅猛提升,电源完整性(Power Integrity)成为了保障产品稳定运行的重中之重。

作为国内领先的高端PCIe SSD主控芯片和方案提供商,忆芯科技一直走在技术创新的前沿,为了满足各行业对于数据处理和存储的需求,其推出多款极具出色性能和稳定性的产品,包括支持PCIe 3.0的STAR1000P、PCIe 4.0的STAR2000、以及最新的PCIe 5.0高性能芯片STAR1500。未来随着数据传输速率和接口带宽的迅猛提升,电源完整性(Power Integrity)成为了保障产品稳定运行的重中之重。

电源完整性的挑战 从低频到高频

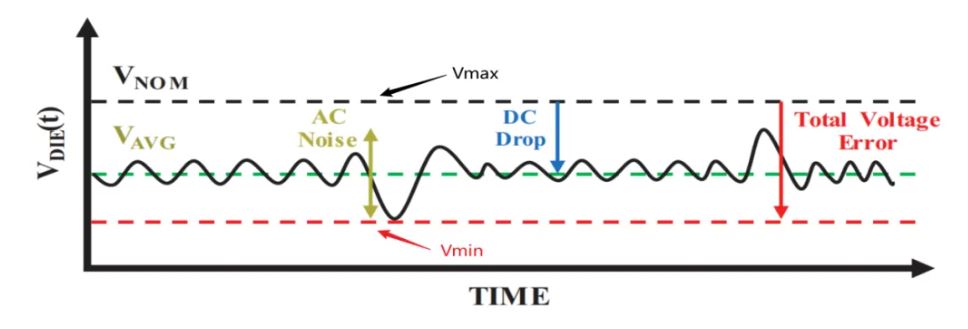

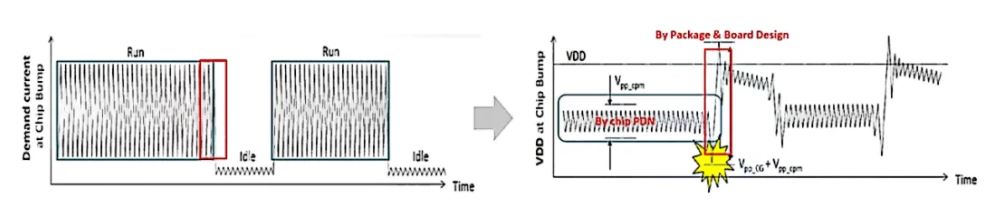

在现代高速数字系统中,电源完整性指的是电源分配网络(Power Distribution Network, PDN)为负载(如CPU、FPGA或SSD主控芯片)提供干净、稳定电源的能力。随着芯片频率的提升,电源噪声、瞬态电流需求和信号完整性之间的相互影响愈发复杂,例如忆芯科技最新主控芯片STAR1500集成了高密度的晶体管和复杂的信号处理模块,这使得电源分配网络(PDN)的设计非常复杂,不仅需要在低频段稳定提供直流电压,还需要在中高频段有效抑制噪声,最终保证在die侧电压的波动满足power domain的SPEC要求,如图1。

图1 die侧电压波动

电源分配网络(Power Distribution Network)

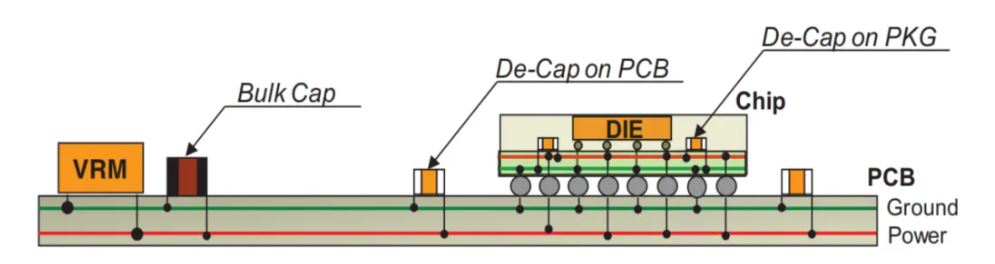

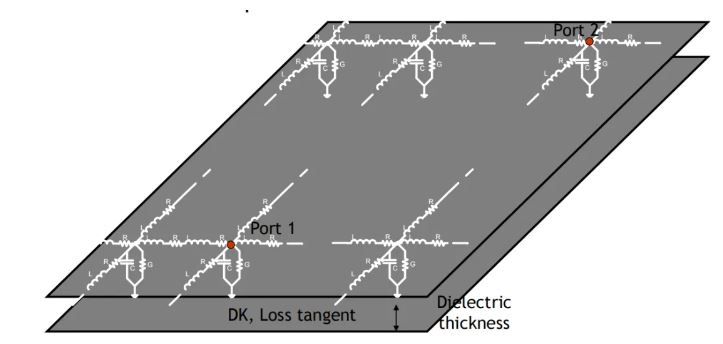

如图2所示,典型的PDN系统由VRM、解耦电容器、平面和集成电路组成。从图中可以看出各个部件与die的临近程度,VRM和Bulk电容离die最远,封装平面和封装电容器离die则较近。各个部件自身的频率响应、它们与die的距离以及各部件和die之间寄生效应决定了各部件对来自die侧电流需求的反应能力。

图2 电源分配网络(PDN)模型

图3是全通路PDN的电路示意图,由电压调节模块(VRM)、电源/地平面对、各种电容组成,这些组件在控制电源分配系统阻抗时,分别作用在不同的频段。VRM响应的频率范围为DC~1KHz;电解电容在1kHz~1MHz内保持较低阻抗;高频陶瓷电容在1MHz~百MHz内保持较低阻抗;电源/地平面对则可以在100MHz以上发挥作用;片上电容则可以在GHz都提供较低的阻抗特性。

图3 全通路PDN电路示意图

造成PDN中电源不稳定的原因

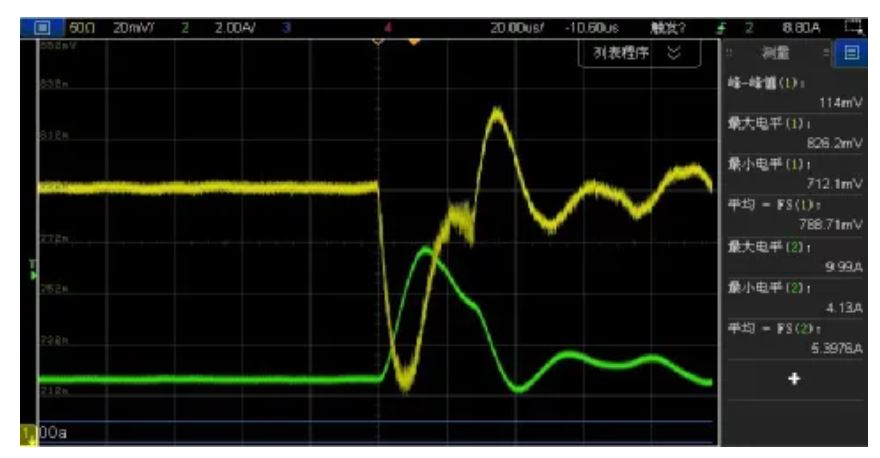

PCIe 5.0高带宽带来的一个显著挑战是瞬态电流的快速变化。当芯片从空闲状态切换到满负载时,内部逻辑电路在高速开关状态下产生的瞬态交变电流过大,使得电源无法实时响应负载对电源需求的快速变化,导致电源电压出现快速压降。即![]() ,电源响应速度慢、瞬态电流大、或者电容储能不够,造成了为提供电荷而引起的电压波动。

,电源响应速度慢、瞬态电流大、或者电容储能不够,造成了为提供电荷而引起的电压波动。

图4 瞬态电流突变导致电压跌落(黄色:电压,绿色:电流)

由于整个PDN通路上存在各种寄生电感,无论键合线、PTH、管脚、走线的寄生电感还是去耦电容的寄生电感(自感和安装电感),甚至包括缝隙电感和过孔电感,使得高频处的阻抗增加进而导致电压出现大的波动,即![]() 。

。

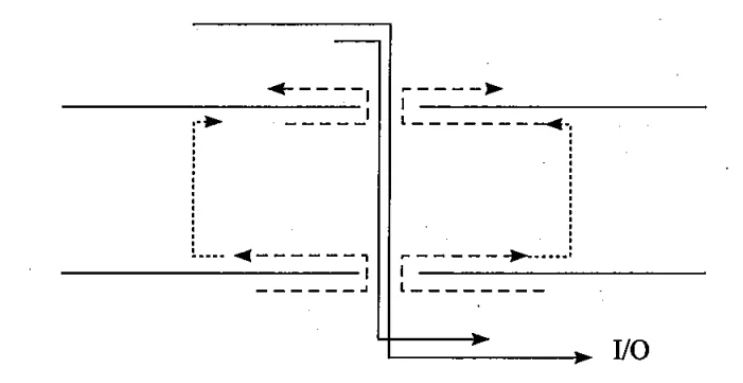

图5 Flip Chip Package图示及电感

![]() 噪声电流或返回电流路径突变均会导致共振现象。如下图信号穿过电源平面和地平面时返回路径在平面间转换,虽然电源、地平面之间存在去耦电容,但是电容只能让返回电流的低频部分通过,而高频部分需由平面间的耦合(即通过换层所在区域)提供回流路径,这个区域会引起局部电源噪声,该噪声会在电源和地平面之间构成的腔体中传播进而影响系统稳定性。

噪声电流或返回电流路径突变均会导致共振现象。如下图信号穿过电源平面和地平面时返回路径在平面间转换,虽然电源、地平面之间存在去耦电容,但是电容只能让返回电流的低频部分通过,而高频部分需由平面间的耦合(即通过换层所在区域)提供回流路径,这个区域会引起局部电源噪声,该噪声会在电源和地平面之间构成的腔体中传播进而影响系统稳定性。

图6 信号换层引起的噪声

电源分配网络(PDN)的优化策略

为了应对PCIe 5.0高性能芯片中的电源完整性挑战,忆芯科技采用了多层次的电源设计优化策略,最终使整个系统的信号完整性和稳定性达到最佳状态。

中频电容谐振峰的优化

中频陶瓷电容在板级去耦中起到非常大的作用。在系统中一般采用并联多种不同容值电容的方式,在这种情况下必须注意不同容值电容器中的并联谐振(称为反谐振),为了使整个PDN系统的阻抗小于目标阻抗,在设计时需要根据电容阻抗特性选择合适的电容组合、摆放位置,并且最小化电容的安装电感来尽量控制谐振峰的大小。

如果去耦网络设计不理想,并联谐振峰使PDN系统阻抗在谐振点附近的一段频率范围内超过目标阻抗,最终会产生潜在的设计风险。如果负载芯片的电流需求又刚好集中在这个频段内,则电压波动就可能超标。

图7 电容器并联谐振峰

平面电容与层叠设计的优化

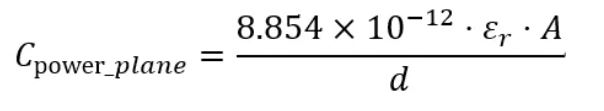

电源平面和地平面能形成一个平板电容(假设电源平面和接地平面相邻),当频率远超过PCB去耦电容作用频段的情况下,平板电容能发挥积极的作用,但唯一的缺点是平板电容很小,因为平面面积很小(典型电路板的典型平面电容 = 322pf/每平方英寸电源平面电容面积),而且连接平面和封装球的电源和接地通孔的环路电感会限制其高频去耦效果,设计时需要注意采用多过孔并联结构以及尽量缩短电源回路。PCB 电源平面电容的计算公式如下:

其中![]() 是平面之间介质的相对介电常数,A是平面的面积(平方米),d是平面之间的距离(米)。使电容最大化的几种方法:保持较小的电源平面和接地平面之间的距离d(使用较薄的电介质),在电源平面和接地平面之间使用较高的

是平面之间介质的相对介电常数,A是平面的面积(平方米),d是平面之间的距离(米)。使电容最大化的几种方法:保持较小的电源平面和接地平面之间的距离d(使用较薄的电介质),在电源平面和接地平面之间使用较高的![]() 电介质材料,以及增大平面面积。其中最大化平面面积的方法之一是在相邻布线层上的未使用平面区域填充电源和地平面,并用缝合通孔连接起来。

电介质材料,以及增大平面面积。其中最大化平面面积的方法之一是在相邻布线层上的未使用平面区域填充电源和地平面,并用缝合通孔连接起来。

图8 电源、地平面电容示意图

芯片封装谐振点

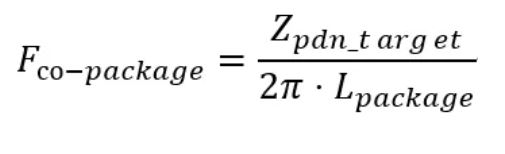

芯片封装电感将产生一个截止频率,超过这个频率PCB安装的电容器的影响可以忽略不计。可以根据电源的目标阻抗来确定截止频率(Fco):

除此之外,还需要考虑封装电感和片上去耦电容的并联谐振,这个谐振尖峰会有比较高的阻抗,在很多情况下,需要通过封装中的去耦电容尽量去抑制这个谐振峰。

图9 芯片封装上去耦电容对谐振峰的改善

高频片上电容优化

随着集成电路工艺的进步,高频片上去耦电容(On-Chip Decoupling Capacitors)成为了电源完整性设计的关键,片上去耦电容决定了最高频率时的PDN的阻抗。片上电容的成因有:(1)电源和地轨道金属层之间的电容;(2)所有的P管和N管的栅极电容;(3)各种寄生电容。片上去耦电容直接集成在芯片内部,离负载非常近且寄生电感和电阻极小,因此它可以在极短的时间内为负载提供充足的电流,快速响应瞬态电流需求,降低电源电压的波动,极大地提高电源系统的瞬态响应能力。

虽然片上去耦电容在高频下效果显著,但其容量通常较小,难以应对中低频段的大容量需求,且片上去耦电容是以牺牲芯片面积为代价的。因此在整个PDN设计中,片上去耦电容的设计要进行全方位的评估,确保die上可以提供的最小电容,并且仍然能够满足系统的目标阻抗。

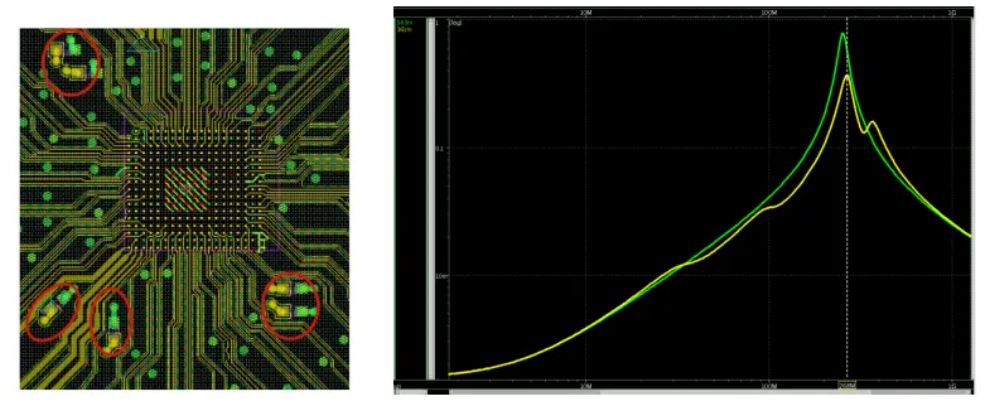

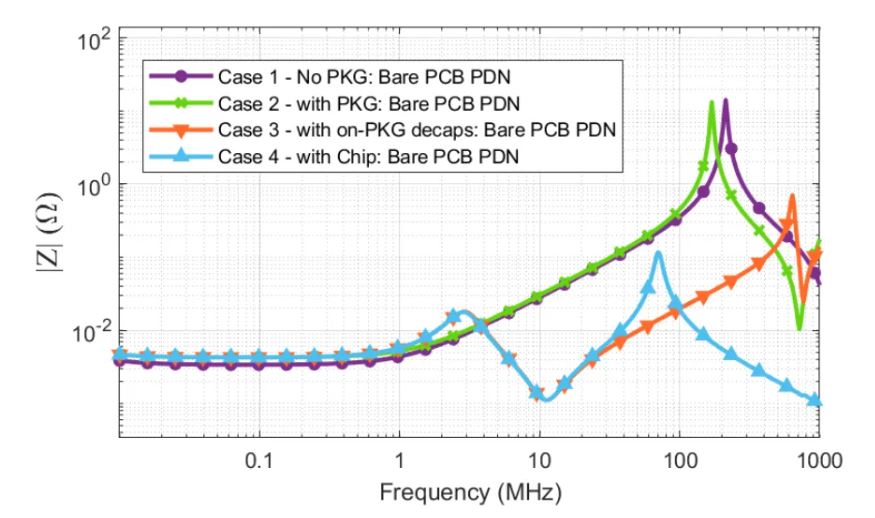

全通路PDN的频域分析优化

除了上述各点细节的优化,最终需要对全通路PDN进行频域分析,评估不同频率下的电源阻抗特性,提前识别出电源系统中可能出现的共振点和高阻抗点来进行优化。

图10 PDN的阻抗特性曲线

Coner case的CPM时域分析优化

芯片在实际工作中会有很多种场景,在不同场景切换过程中,可能会激发各种抽电状态,包括激活阶段、上升阶段和负载释放阶段。其中重载到ideal或ideal到重载状态的快速切换中,会激发陡峭的上升沿或者下降沿,对PDN造成极大的冲击。这种coner case可以从芯片后仿VCD波形中获取,再进行CPM(chip power model)的提取,以进行全通路的时域分析,联合验证优化全通路PDN的设计。

图11 Coner case的电源变化图示

多通道噪声电流的共振分析

SSD的主控芯片会有较多的ONFI通道,常见的为8CH/16CH,不同的容量会涉及到挂载的NAND颗粒数量不同。在产品设计过程中,会将SSD主控的IO 电源和NAND颗粒的IO电源合并设计,这样可以节省器件成本,且整个电源的平面也会更加完整,但是各个CH间的噪声电流会在整个腔体中形成共振,需要在设计的时候考虑这种共振情况。

共振情况的分析需要考虑整个PDN的频域特性,如前文提到的一些比较高的谐振峰,对于ONFI多CH的接口设计中,如果系统在工作中正好激发前文所提到的谐振峰相应频点的噪声电流,多通道的噪声电流共振会对整个PDN带来严重的冲击。在分析过程中需要创建一个尽可能接近该阻抗谐振峰的激励造成worst case以测试PDN的鲁棒性。

电源完整性对系统性能的影响

对于忆芯科技PCIe 5.0 SSD主控芯片STAR1500来说,传输速率相比PCIe 4.0翻倍达到32GT/s,数据的吞吐量更大,面临的场景也更复杂,内核电源、IO电源对其PDN性能的要求也更高,保证电源完整性对系统整体性能和稳定性起到至关重要的作用:

更低的误码率

由于噪声和电压波动的抑制,芯片能够以更低的误码率传输数据,确保了数据传输的完整性。

更高的能效比

优化后的低阻抗电源分配网络减少了不必要的电能损耗,提升了系统的整体能效,降低了功耗。

更高的稳定性

在极端工作条件下,优化电源完整性的设计保障了系统的稳定性,避免因电源不稳定导致的系统崩溃和性能下降。

参考文档:

【1】 A Novel System-Level Power Integrity Transient Analysis Methodology using Simplified CPM Model, Physics-based Equivalent Circuit PDN Model and Small Signal VRM Model

【2】Power Integrity Modeling and Design for Semiconductors and Systems

【3】信号完整性与电源完整性分析

本文转载自:忆芯科技

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读:

从富士通到RAMXEED,以全新一代FeRAM迎接边缘智能高可靠性无延迟数据存储需求

凭借超低功耗图像传感器系列,安森美荣获AspenCore全球电子成就奖