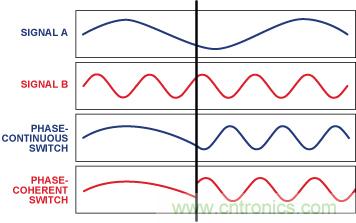

【导读】常见的单通道直接数字频率合成器(DDS)可产生如图1所示的相位连续频率转换。但在相干脉冲多普勒雷达和用于医疗和材料分析的NMR/MRI波谱等应用中,相位相干转换是首选。本文说明如何配置AD9958/AD9959多通道DDS,通过叠加DDS输出实现稳定的相位相干频移键控(FSK)调制器。

多通道DDS几乎完全消除了同步多个单通道器件时遇到的通道间温度和时序问题。多通道DDS输出尽管相互独立,但可共用同一系统时钟,因此对温度和电源偏差的追踪性能优于多个单通道器件的输出。所以,多通道DDS更适合在叠加输出端产生相位相干频率转换。

图1. 相位连续和相位相干频率转换。

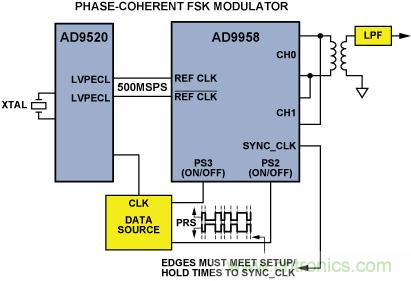

电路描述

AD9520 时钟分配器件通过高性能基准时钟驱动AD9958 DDS,同时为FSK数据流源提供相同时钟。AD9520提供多种输出逻辑选择和可调延迟,以满足FSK数据流与多通道DDS SYNC_CLK间的建立和保持时间。

AD9958的两个独立通道采用预编程频率F1和F2工作。将输出端连接在一起进行叠加。模式(Profile)引脚驱动各DAC输入的乘法器以控制输出幅度,这些引脚可开启或关闭通道输出以选择理想频率。为此,每个乘法器预编程两个模式可选设置:零电平和满量程。模式引脚上的逻辑低电平将关闭正弦波,而逻辑高电平将其传递至输出端。该操作需要两个互补输入数据流以在频率间交替。请注意,两个DDS通道持续产生频率 F1和F2。关闭功能将消除相应的DDS输出,从而产生相位相干FSK信号。

图2. 相位相干FSK调制器设置。

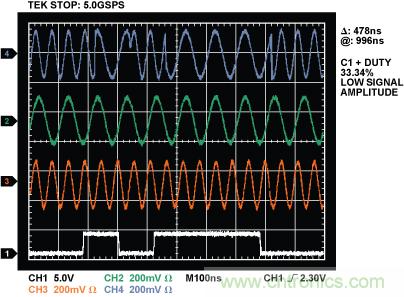

AD9959 4通道DDS产生如图3所示的结果。两个额外通道可用作叠加输出端两个开关频率的相位基准,以便于说明相位相干开关。上面的波形显示的叠加输出表示相位相干开关。中间两条波形显示的是基准信号F1和F2。下面的波形显示的是在两个频率间交替的伪随机序列(PRS)数据流。请注意,由于器件内的流水线延迟,PRS数据流边沿与叠加输出的频率转换并未完全对准。

图3. 实测的相位相干FSK转换。

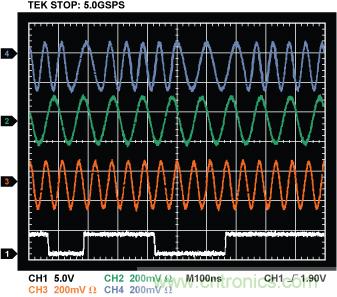

图4显示了同样由AD9959产生的相位连续FSK开关的一个范例。这种操作需要的带宽较少,但转换之间无相位存储。

图4. 实测的相位连续FSK转换。

ADI公司提供各种直接数字频率合成器、时钟分配芯片和时钟缓冲器,用来构建基于DDS的时钟发生器。如需了解更多信息,请访问www.analog.com/dds 和 www.analog.com/clock.

多通道、10位、500 MSPS直接数字频率合成器

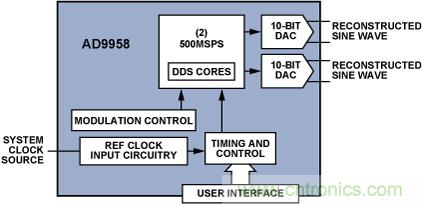

2通道AD9958 (图5)和4通道AD9959直接数字频率合成器(DDS)内置两个/四个10位、500 MSPS电流输出DAC。所有通道共用同一系统时钟,因此本身就具有同步功能;将多个器件互连可提供更高通道数。各通道的频率、相位和幅度可独立控制,使器件可校正系统相关失配。所有参数可线性扫描;或者可为FSK、PSK或ASK调制选择16个电平。输出正弦波调谐具有32位频率分辨率、14位相位分辨率和10位幅度分辨率。AD9958/AD9959采用1.8 V内核电源供电,与3.3 V I/O电源逻辑兼容,功耗为315 mW/540 mW(所有通道开启和 13 mW 掉电模式。额定温度范围为–40°C至+85°C,采用56引脚LFCSP封装,千片订量报价为20.48/37.59美元/片。

图5. AD9958功能框图。

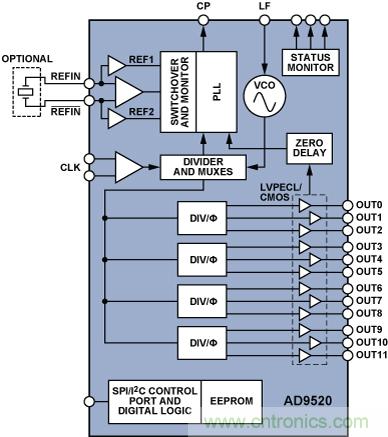

12 LVPECL/24 CMOS输出时钟发生器

AD9520-x 时钟发生器(图6)可从单一基准频率获得多达12个LVPECL或24个CMOS时钟。由于集成了内置VCO的完整PLL、可编程分频器和可配置的输出缓冲器,该器件实现了亚皮秒抖动性能。四个选项为片内VCO提供了1.45 GHz至2.95 GHz的中心频率;第五个选项采用外部VCO工作,频率可高达2.4 GHz。该器件接受高达250 MHz的一路差分或两路单端基准时钟,提供四组频率可达1.6 GHz的LVPECL时钟(每组三个)。可编程分频器的分频比为1比32,可为每一组时钟设置输出频率和粗调延迟。各LVPECL输出可重新配置以提供两个250 MHz CMOS输出。AD9520-x采用3.3 V单电源供电,最大功耗为1.5 W;单独的输出驱动器和电荷泵电源可用于逻辑兼容并支持具有扩展调谐范围的VCO。器件采用64引脚LFCSP封装,额定温度范围为–40°C至+85°C,千片订量报价为12.65美元/片。

图6. AD9520功能框图

参考电路

1. AN-837 Application Note, DDS-Based Clock Jitter Performance vs. DAC Reconstruction Filter Performance.

2. Kester, Walt. The Data Conversion Handbook. Analog Devices. Chapters 6 and 7. 2005.

3. Kester, Walt. High Speed System Applications. Analog Devices. Chapters 2 and 3. 2006.

4. MT-101 Tutorial, Decoupling Techniques.

5. MT-031 Tutorial, Grounding Data Converters and Solving the Mystery of AGND and DGND.

推荐阅读: