【导读】随着数据转换器的速度和分辨率不断提升,对具有更低相位噪声的更高频率采样时钟源的需求也在不断增长。时钟输入面临的积分相位噪声(抖动)是设计师在设计蜂窝基站、军用雷达系统和要求高速和高性能时钟信号的其他设计时面临的众多性能瓶颈之一。普通系统有多个低频噪声信号,PLL 可将其上变频至更高频率,以便为这些器件提供时钟。单个高频PLL可以解决频率转换问题,但很难设计出环路带宽足够低,从而能够滤除高噪声参考影响的PLL。搭载低频高性能VCO/VCXO和低环路带宽的PLL可以清除高噪声参考,但无法提供高频 输出。高速和噪声过滤可以通过结合两个PLL同时实现:先是一个低频窄环路带宽器件(用于清除抖动),其后是一个环路带宽较宽的高频器件。

有些现代双环路模拟 PLL 集成于单个芯片之上,允许设计师 减少低频参考抖动,同时还能提供高频、低相位噪声输出。这 就节省了宝贵的 PCB 电路板面积,而且允许要求不同频率的 多个器件以同一相位对齐源为时钟源。

AD9523, AD9523-1和 AD9524 时钟发生器(如图 1 所示)由 两个串联模拟PLL构成。第一个PLL (PLL1)清除参考抖动, 第二个PLL (PLL2)生成高频相位对齐输出。 PLL2 也可生成高 基频,再以此为基础衍生出各种低频。PLL1 使用一个外部低 频VCXO和一个部分嵌入式三阶环路滤波器来构成一个PLL, 其环路带宽范围为 30 Hz至 100 Hz。该环路的带宽直接影响 将传播至输出的参考输入相位噪声量。 PLL2 使用一个内部高 速VCO(中心频率为 3.8 GHz,AD9523-1 为 3 GHz)和一个 部分嵌入式三阶环路滤波器,其额定环路带宽约为 500 kHz。 该内部VCO的带宽和相位噪声会直接影响整体输出的宽带相 位噪声。

图 1 AD9523-1 的功能框图

许多工程师把双环路 PLL 当作频率转换器,可减少固定量的 参考输入抖动,但更加准确的做法是将其视为低相位噪声频率 转换器,其性能受到各个 PLL 的环路带宽以及 VCO/VCXO 的 相位噪声曲线的影响。

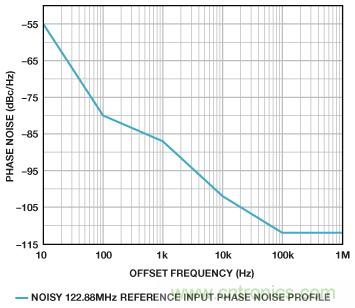

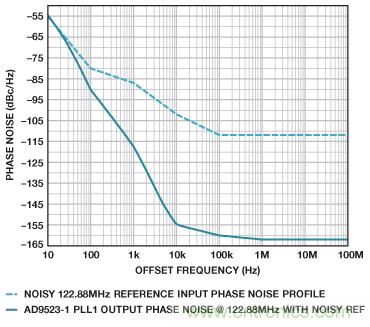

ADIsimCLK™ 仿真工具为确定参考相位噪声对双环路PLL输出 相位噪声的影响提供了一种简便的方法。本例使用ADIsimCLK 来模拟高噪声参考对AD9523-1 整体相位噪声的影响。图 2 所 示为一个仿真 122.88 MHz参考输入的典型相位噪声曲线。

图 2 122.88 MHz 时的参考相位噪声曲线

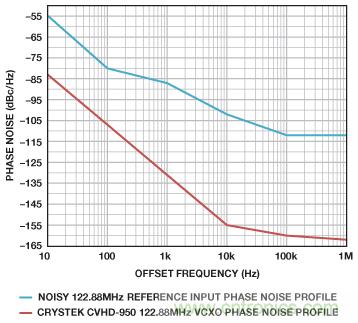

PLL1 依赖高性能 VCXO 和低环路带宽来衰减参考相位噪声, 从而允许 VCXO 的相位噪声占据主导地位。本例采用一个 Crystek CVHD-950 VCXO来生成与参考输入相同的输出频率。 这幅图直接比较了 PLL1 输出端出现的参考相位噪声量。图 3 对 Crystek CVHD-950 VCXO 的相位噪声曲线与参考输入相位 噪声进行了比较。

图 3 122.88 MHz 时的 Crystek CVHD-950 相位噪声曲线

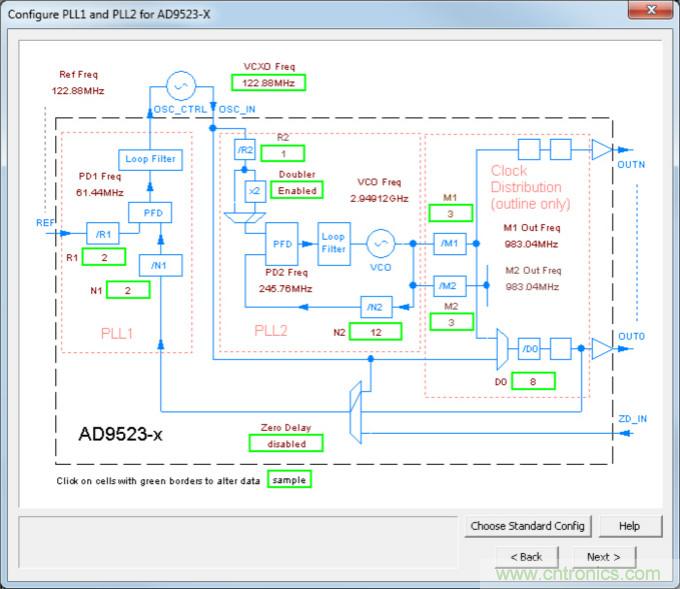

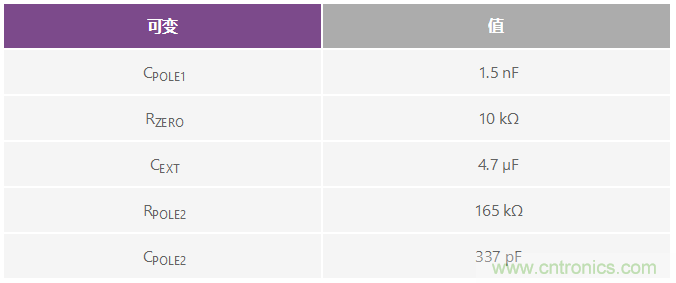

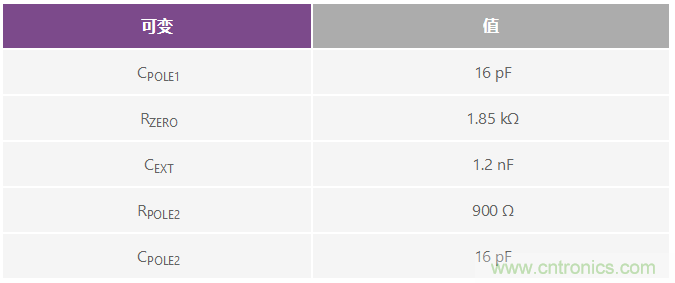

图 4 和表 1 所示为 ADIsimCLK 配置参数,这些参数用来仿真 针对图 3 所示参考输入和 PLL1 VCXO 相位噪声曲线, AD9523-1 的 PLL1 输出相位噪声响应情况。表 2 所示为 ADIsimCLK 在这些设置下生成的 PLL1 环路滤波器值。

图 4 ADIsimCLK v1.5 中的 AD9523-1 配置

表 1 PLL1配置参数

表 2 ADIsimCLK产生的 PLL1环路滤波器元件值

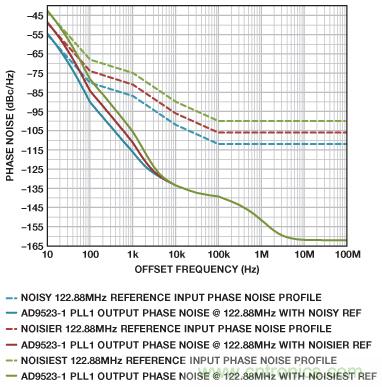

图5展示的是通过ADIsimCLK生成的PLL1在122.88 MHz条 件下的仿真输出(实线),以及高噪声 122.88 MHz 参考频率 的原始相位噪声曲线(虚线)。请注意,PLL1 的输出相位噪 声远远低于原始参考输入相位噪声。PLL1 的环路带宽会显著 衰减参考频率的相位噪声,使 VCXO 的低相位噪声曲线可以 在 30 Hz 环路滤波器截止频率之后占据主导地位。如果参考相 位噪声在全部偏移频率上都在增加,则输出相位噪声将只会随 PLL1 环路带宽而增加。

图 5 采用高抖动参考频率的 PLL1 输出相位噪声

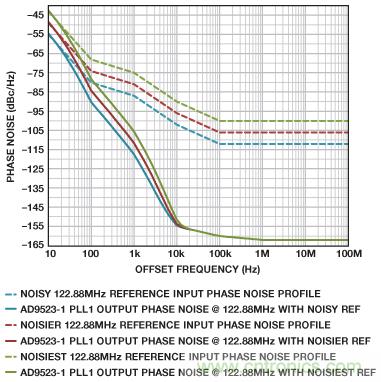

图 6 和图 7 展示的是 AD9523-1 PLL1 输出,其相位噪声比 图 2 中的高噪声参考频率分别高出 6 dB 和 12 dB。 在频偏约 20 kHz 以外,PLL1 的输出相位噪声由其环路设置和 VCXO 的性能所主导。因此,由于积分范围始于 20 kHz 失调,抖 动性能只会略微变化,尽管参考输入相位噪声会增加 12 dB。 这是在设计时使 PLL1 具备低环路带宽并使用低相位噪声 VCXO 带来的直接结果。必须使用具有低 KVCO 的低频、高 性能 VCXO 来形成足够低的 PLL1 环路带宽,以便实现抖动 的清除。

图 6 采用各种参考频率的 PLL1 输出相位噪声

图 7 采用各种参考频率的 PLL1 输出相位噪声

PLL1 的低相位噪声输出充当 PLL2 的参考频率,以形成相位 对齐、频率更高的输出。

PLL2含有一个内部VCO (其中心频率为3 GHz), 最高支持1 GHz 的输出频率。为了比较高噪声输入参考频率和AD9523系列器件 的整体相位噪声,需要在 122.88 MHz 下考察所得到的相位噪声 (FVCO 除以 24)。注意,PLL2 的输出一般用于频率转换或高频 输出。表 3 所示为输入 ADIsimCLK 的 PLL2 配置参数。表 4 所 示为ADIsimCLK在这些设置下生成的PLL2环路滤波器值。

表 3 PLL2配置参数

表 4 来自 ADIsimCLK的 PLL2环路滤波器元件值

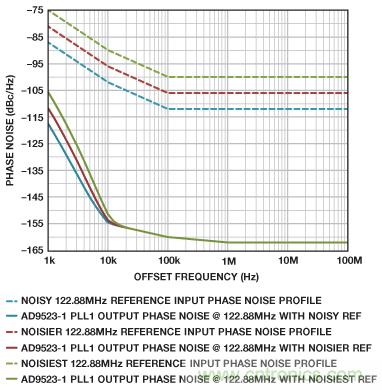

图 8 和图 9 对各参考输入相位噪声与通过 ADIsimCLK 仿真得 到的 AD9523-1 输出相位噪声结果进行了比较。请注意 10 kHz 和 1 MHz 之间增加的相位噪声基底。这是因为 PLL2 的内部 VCO 相位噪声的关系。

图 8 采用各种参考频率的 PLL2 输出相位噪声

图 9 采用各种参考频率的 PLL2 输出相位噪声(放大图)

PLL2 中的内部 VCO 相位噪声在大约频偏为 5 kHz 之后足够 高,会开始主导器件的总输出相位噪声。在频偏 5 kHz 区域之 后,增加的参考相位噪声对输出相位噪声的影响很小。

结论

PLL1 的抖动清除功能可以防止多数参考输入相位噪声到达 PLL2。高噪声参考输入确实会影响近载波相位噪声(频偏 10kHz 以下),但器件的总输出抖动是由器件的性能而非参考频率的性能所主导的。对于积分抖动计算值处于 12 kHz 至 20 MHz 之间的情况,输出抖动很可能相同,不受输入抖动的影 响。真正的性能指标不是声称双环路模拟 PLL 可以衰减多少 抖动,而是它会产生多少抖动。

推荐阅读: