【导读】一直以来,设计人员都将最小化功耗的工作留给实现/物理工具来完成。但到了这个时候,有关设计的所有重要架构和微架构决策都已确定。物理工具对功耗的影响非常有限。这些工具无法对设计架构进行彻底的更改,从而实现节能。物理工具所用的方法,例如单元尺寸调整、管脚交换和 Vth 选择,只能将稍稍降低功耗而已。

UPF 主要用于增强漏泄功耗的功率门控,其主要用途是定义电压域。指定不同电压域的其中一个原因是为了协商功耗与性能之间的折衷方案。较高的电压可获得更快的速度,但需要更高的动态功耗 (1/2 C V2 f)。

功耗与电压的平方成正比。因此,降低动态功耗要从针对设计中的不同模块规划合适的电压电平开始。动态功耗主要受活动影响。设计中运行的工作越多,最终需要的能量就越多。随着在设计中完成工作的速度提高,所需功耗也会增加。要节省动态功耗,可以降低设计的工作速度(降低时钟速度),尝试降低电压,或尝试削减设计活动。减小设计中的电容是节能的另一个重要方面,这通常可借助高效的实施或通过调整工艺来实现。

一般而言,设计架构师比较擅长确定电压和时钟速度。但目前为止,还未找到减少活动(尤其是不必要的活动)的有效做法。此类缩减往往需要微架构更改(例如 FSM 重新编码、模块级时钟门控、存储器门控、存储器分块和旁路存储器访问),而这类更改要求深入了解设计功能。这类更改适合由编写 RTL 的设计人员来执行。

在许多公司,降低功耗的工作交给功耗专家完成。这些专家具备多年积累的反复应用于所在业务组设计的知识和方法。但这种方法非常狭隘,无法在公司内多个业务组之间拓展。

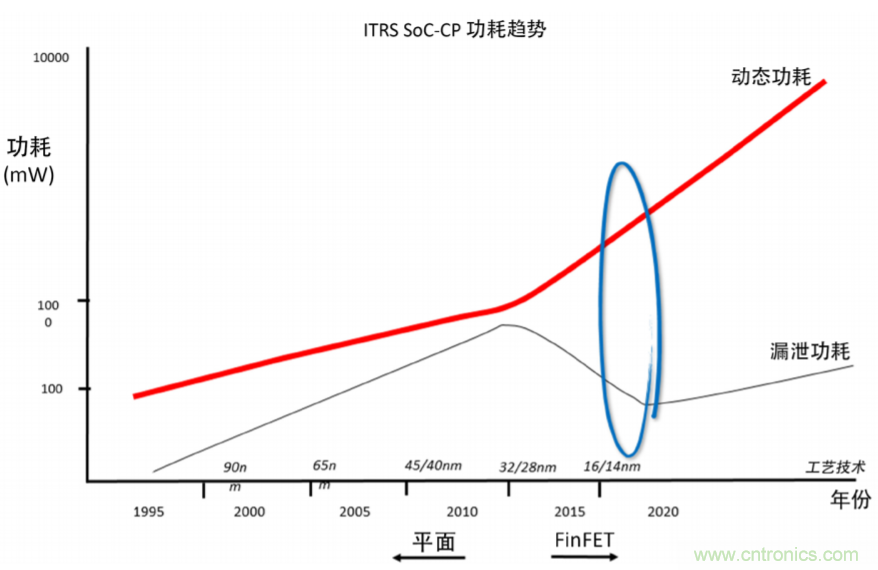

公司开始认识到这一方法的局限性。于是越来越多的 RTL 设计人员从一开始便承担了解决功耗问题的任务。理想情况下原本就应如此。了解设计的人员是进行功耗优化的最佳人选。而且,在设计转向 FinFET 技术的过程中,动态功耗已成为功耗的主导因素(图 1)。

图 1:功耗趋势。

降低 RTL 动态功耗的常用方法

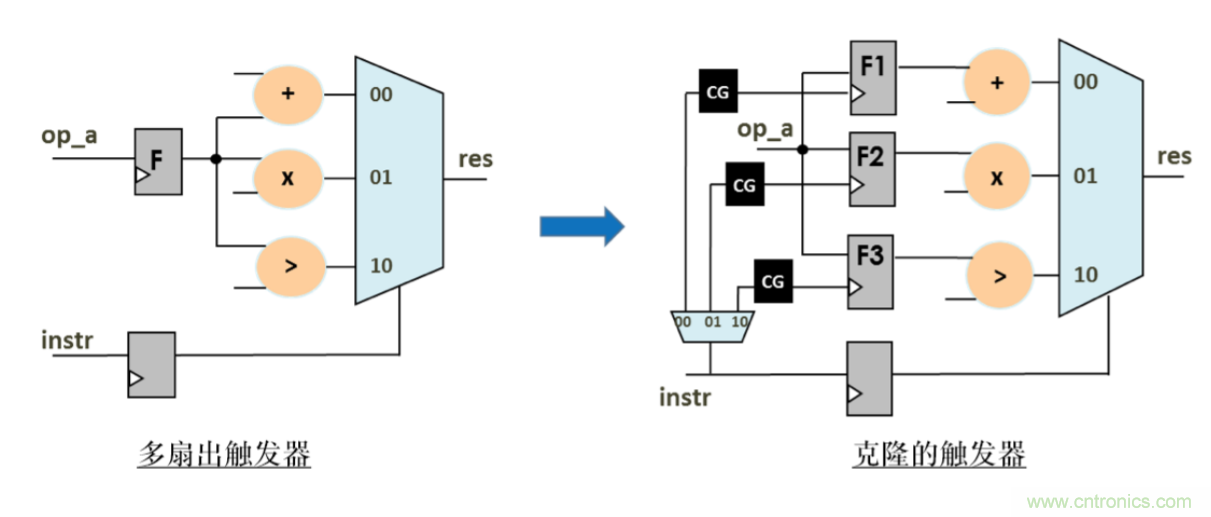

在 RTL 做出的决定对设计功耗的影响远大于在设计流程后期做出的决定。RTL 设计人员严重依赖时钟门控来削减时钟翻转。这是目前占绝对优势的降低动态功耗的最常用方法。RTL 设计人员使用的一些其他方法包括数据门控和触发器克隆/共享(图 2)。

图 2:克隆触发器方法。

图 2 显示:

• 触发器 F 提供了用于 3 种算术运算的运算符。

• 触发器 F 无法进行门控,因为至少一种算术运算需要它的值。

• 即便执行一种运算,另外两种运算中的逻辑也会发生不必要的翻转并产生功耗。

• 通过将触发器 F 克隆到三个触发器(F1、F2 和 F3)中,可在对两种运算进行门控的同时计算第三种运算。

通过这一更改,设计人员需要确认额外触发器的功耗要远小于它们所控制的下游算术运算功耗。

要对功耗产生更深刻的影响,RTL 设计人员需要在设计中进行越来越多的粗粒度(微架构)更改。例如,通过以下方法可显著削减动态功耗:

• 模块级的时钟门控

• 将寄存器链转换为环形缓冲器

• 关断存储器

• 旁路存储器访问

• 执行重定时

• 使用运算符屏蔽。

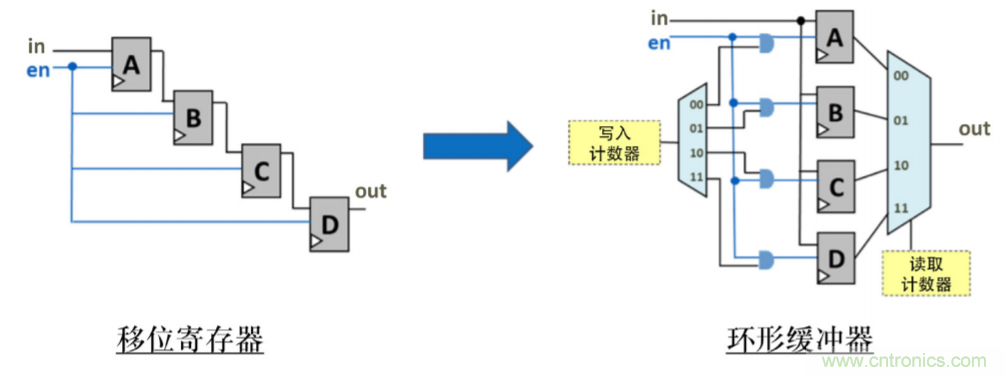

将移位寄存器替换为环形缓冲器是一种常见的微架构设计更改。移位寄存器中的活动量很大,因为沿着接收新值的触发器链,数据一直都在进行移位。这一移位操作导致触发器(以及这些触发器所驱动的逻辑中)发生多次不必要的翻转并造成功耗。因此,设计人员考虑将移位寄存器替换为环形缓冲器(图 3),因为这些缓冲器在读取或使用新值时不需要移动。

图 3:将移位寄存器替换为环形缓冲器。

进行这一更改后,设计人员需要确认在环形缓冲器内添加读/写指针逻辑产生的功耗不会超过通过使用环形缓冲器节省的功耗。

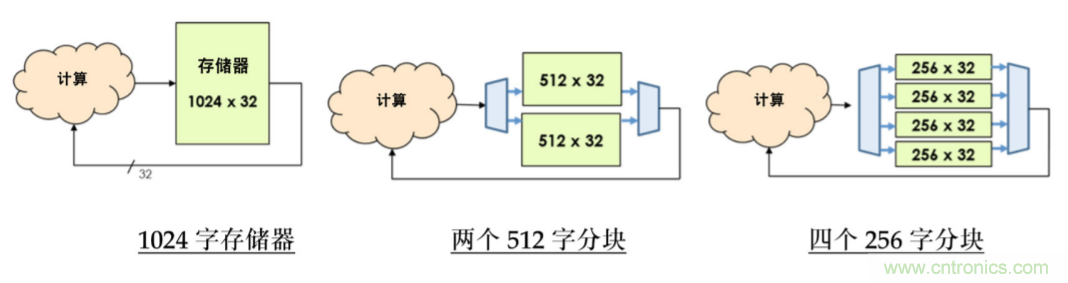

由于在任意给定的时间间隔,仅仅访问总计地址中的少数几个地址,因此存储器会浪费功率。为解决此问题,设计人员可使用较小的“分块”实施总体存储器,这些分块在未被访问时可予以关断(图 4)。

图 4:存储器分块示例。

图 4 显示了对一个 1024 字存储器进行分块的两种方法:

1. 两个 512 字的分块:仅其中一个分块处于主动被访问状态,另一个分块则通过门控关断以节省功耗。

2. 四个 256 字的分块:任意时刻有三个分块可处于门控关断状态。

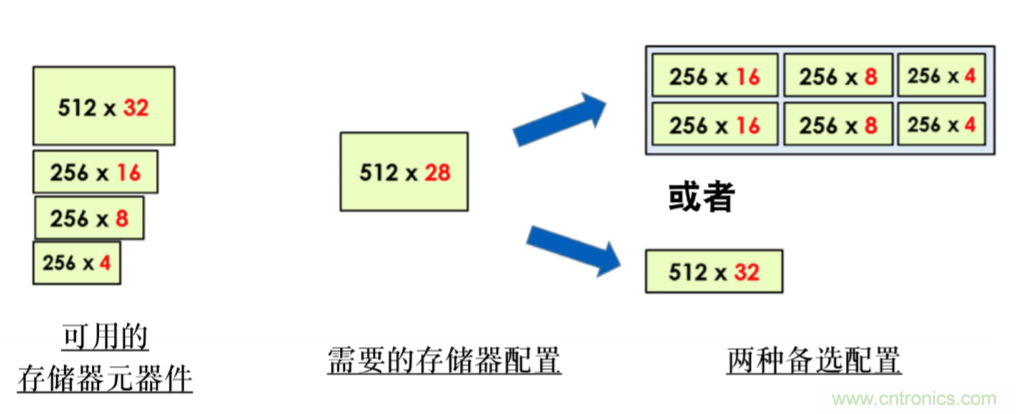

另一种设计存储器以节省功耗的方法是通过一组固定宽度的存储块来配置所需的存储器字大小。在图 5 所示的示例中,有多种实现 512 字 X 28 位存储器的方法,图中提供了两种:

1. 刚好使用 28 位字大小 (16 + 8 + 4) 并插入额外的编码逻辑,用于在两个分块之间做出选择(图 5 右上角)。

2. 使用单个 32 位存储器元器件(图 5 右下角)。尽管此解决方案不需要任何编码逻辑,但有 4 位存储器被浪费。

图 5:可能的存储器配置。

不论设计人员采用哪种方法来降低存储器功耗,都必须非常小心,确保额外解码逻辑的功耗仍小于较大的原始存储块功耗。

遗憾的是,前述方法的接受度远不如预期。主要有两个原因:

• 不容易了解设计中存在这类机会。

• 不容易了解通过做出更改将会降低多少功耗。

通常,设计人员依赖他们的经验或直觉做出设计更改。他们载入仿真波形,并尝试估计其设计中可能出现冗余活动的位置。然后,根据此类活动所在的区域,尝试评估可减少浪费活动的方法。对一般 RTL 设计人员而言,这样未免要求过高。因此,很多功耗节省未能付诸实施。使用 PowerPro® 提供了一种解决方案。

使用 POWERPRO 降低动态功耗

很显然,传统的降低功耗方法已经不再行得通。迁移到 FinFET 给动态功耗带来了与日俱增的严峻挑战。为保持竞争优势,单纯依赖功耗专家来降低功耗已经远远不够了。公司将会在功耗方面落后于竞争对手。

简单地报告设计的功耗数字已不再适宜。功耗分析是一个重要的步骤,但它本身并不能节省任何功耗。最终要取决于设计人员个人的专业知识,以及他们如何解读工具报告从而优化功耗设计。

RTL 设计人员需要关于设计中哪些位置可以节省功耗的指导。他们需要关于其设计中存在的优化范围(例如模块级时钟门控、移位寄存器到环形缓冲器、存储器缓存和复位移除)及相关功耗节省的确凿证据。PowerPro 在设计中提供了进行许多微架构和细粒度优化的可能性,并且呈现了与每项更改相关的实际功耗节省。与手动方法相比,其可最大限度减少了花费在做出设计决策上的时间。基于 PowerPro 的建议,设计人员可根据其设计进度做出更改。如果依据进度还有足够的时间,他们可以实施所有建议。如果时间有限,设计人员可以选取最佳建议加以实施。在设计流程中采用 PowerPro 时,这一灵活性至关重要。

功耗优化的另一个关键部分是探索各种更改(例如工作模式、时钟频率、工作电压和工艺技术)对应的功耗的能力,对于 IP 开发人员而言尤其如此。建议的优化应适用于上述所有参数。利用 PowerPro,设计人员可以探索仿真配置文件、电压、时钟速度和设计自身的更改。在 PowerPro 内可以并行评估以上多种更改(图 6)。因此,过去需要几周才能完成的探索任务,现在只要几个小时就能完成。这种生产率提升让 PowerPro 成为极具吸引力的设计流程补充。

图 6:PowerPro 功耗探索。

检测功率冗余的基础技术是形式化分析。PowerPro 对设计执行深入的时序分析,以找出存储器访问、寄存器载入和数据路径计算中存在的冗余。由于 PowerPro 能够基于时序探索建议修改,因此远优于市场中的同类竞争技术。PowerPro 可针对设计流程的所有方面提供支持,包括写出优化的 RTL、ECO 和验证。设计人员确信,他们可以接受源自 PowerPro 的所有建议,并且不会对其交付进度产生任何不利影响。

推荐阅读: