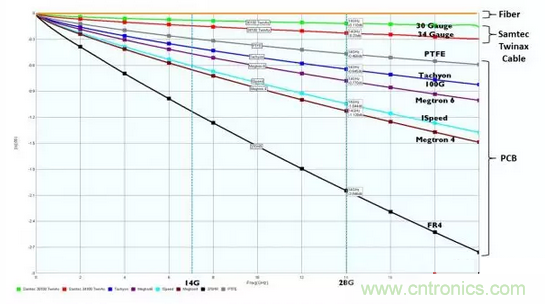

随着对带宽需求的不断增加,对系统内更高数据速率的需求也在不断增加。曾经1到3Gbps,接着转向到4到8 Gbps,现在我们接近28 Gbps,并预计进入56 G。这一趋势最近被推动到DesignCon 2018,许多参展商展示了以112 Gbps运行的互连 PAM 4。

虽然数据通信和电信行业正在努力推动这些前沿的数据速率,但要实现这一性能远比说起来困难得多。设计挑战包括PCB上的路由复杂性,以及对更高层数的潜在需求。对于更长的走线长度,可以采用具有较低介电常数和重新定时器的更具奇特性的PCB材料,以减轻降级信号损失。所有这些因素都会增加系统成本。

除了材料和成本之外,设计师还经常面临成品尺寸减小的挑战。移动和手持设备的激增推动了这一趋势,以及电信、高功率计算机、医疗设备、航空航天和国防,甚至工业应用等行业的新要求。

此外,新的高数据速率芯片组(当然设计为产生尽可能少的热量)仍然产生热量。这些通常需要更多更大的散热器,这进一步使设计困境复杂化。

显然,对更小、更高带宽PCB的不断增长的需求推动了互连行业的研发。微间距和高速互连系统的销售稳步增长。有趣的提醒是大多数高速互连也是微间距。但是,互连的间距越小,实现更高带宽就越困难。

更小更紧的间距互连系统带来了一系列新的电气挑战,例如串扰和插入损耗。这主要是由于一个差分对与下一个太接近,从而减少了布线空间,减少了接地引脚。

与许多设计挑战一样,有几种方法可以解决这个问题:

PCB布局

设计师可以通过对其电路板布局进行战略性考虑来缓解这些问题。精心规划的走线设计和布线、接地位置、过孔等可提高PCB数据速率。PCB设计策略超出了本文的范围,但存在大量工具、资源和人员来协助这项工作。例如,Samtec拥有Signal Integrity Group和Teraspeed Consulting来协助解决这些问题。

高速微间距互连设计

尽管小型化和更高数据速率的目标存在冲突,但连接器制造商可以在性能和占用空间尺寸方面取得平衡。

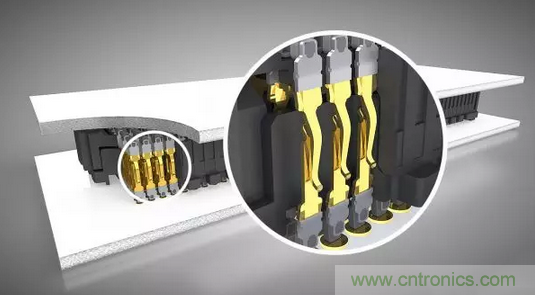

这些连接器设计策略的一个例子是名为EdgeRate®的接触。该接触设计用于更高周期的应用,同时适应更高的带宽。例如,0.8mm间距边缘速率互连的额定值为56 Gbps PAM4。在带宽和间距之间实现这种平衡的方法之一是在塑料体中设计和放置销。具体而言,Edge Rage接触的薄而窄的切割边缘并排放置。这使平行表面积最小化,这减少了宽边耦合和串扰。

提高连接器性能

用于实现高带宽微间距互连的其他连接器设计策略包括但不限于:

· 在设计的早期阶段执行多个模拟循环,以便在开始昂贵的加工过程之前准确地量化产品性能。

· 连接器配对时,最小化接触区域中的过孔stub。从机械角度来说,过孔stub越长,可靠性越好,但是过孔stub是一种像天线一样的电气负荷。

· 简化接触几何形状,以提高信号路径性能。

· 缩短引脚长度以最小化信号必须传播的距离。

· 尽可能包括不对称的占位和接触;交替设计减少了引脚行之间和行之间的成对对的串扰。换句话说,占位应该驱动连接器性能。

· 优化连接器分支区域(BOR)。将连接器视为链路中的关键节点;不仅关注节点,还关注链接。

· 在空间允许的情况下,将共同的地平面插入连接器。

塑料成型的产品显然会影响连接器的性能。在其他问题中,我们仔细考虑以下属性:

· 适用于RoHS的高温塑料

· 匹配Dk以获得所需的阻抗控制

· 温度和时间的尺寸稳定性

最重要的是,信号路径(和连接器接触)越短越直,信号完整性能越好。但平衡作用是连接器必须具有足够的正向力和拔出力,以及具有一定程度的坚固性。后面的考虑通常会降低信号完整性性能。