【导读】汽车是近两年被高频提及的产业,2022年至2029年,预计电动汽车(EV)占比将增长近一倍,同时L2级别及以上的自动驾驶汽车占比也在逐渐增加。中国则处于“弯道超车”的市场地位,到去年为止,电动汽车占比已经超过了一半。

汽车是近两年被高频提及的产业,2022年至2029年,预计电动汽车(EV)占比将增长近一倍,同时L2级别及以上的自动驾驶汽车占比也在逐渐增加。中国则处于“弯道超车”的市场地位,到去年为止,电动汽车占比已经超过了一半。

对汽车来说,电动汽车的功率转换需要大功率分立半导体,电池管理IC负责电池平衡和监控,ADAS(以及最终的无人驾驶)需要RF、激光雷达、超声波和图像传感器以及高端处理能力,MCU/SoC则负责控制车内功能,在车辆安全方面发挥着关键作用。

这将不断驱动半导体在汽车中的数量和金额占比增加。据测算,2023年芯片在整车中的占比在800~1000美元,5年后可能会达到1500美元。反观过去一年半导体产业发展,消费类产品相对疲软,且到现在仍未有明显复苏迹象,因此汽车会是过去一年芯片产业最大驱动力之一。

增长之下,满是挑战。汽车产品的质量与人的生命财产安全有着直接的关系,一旦出现问题,可能会带来毁灭性的打击。因此,车规级产品对整体质量的把控相对更为严格,加之ADAS级别提升,芯片测试的复杂程度也呈指数级增长。

此外,对汽车芯片来说,越早能够发现问题,就越能将成本前移,从而获得更好的市场竞争力。泰瑞达(Teradyne)作为自动测试设备行业(ATE)关键领导者,最近分享了先进节点下,汽车芯片所面临的挑战与良策,同时分享了如何助力国产芯片解决测试难题。

策略、流程、工具,实现零质量缺陷的三大要点

“无论是AEC-Q100还是ISO26262,其本质目标都是零质量缺陷(0 DPPM,即每百万分之零的缺陷),要完成零缺陷,任何一个环节都不能掉链子,因为环节太多,哪怕任一环节出现千分之一、万分之一的问题,叠加起来都会是非常大的质量缺陷。”泰瑞达中国区总经理Felix Huang这样解释道。

对泰瑞达来说,零缺陷是永远的目标,目前国内顶尖的ADAS公司已在泰瑞达平台上做到10 DPPM,但同时也付出了很高的成本。正常来说,一颗芯片测试成本占芯片售价5%~10%,最多不超过15%,而该公司的产品则接近30%,超过大芯片封装的成本。

因此,想要更好地实现零质量缺陷的目标,有三个关键点。一是策略,关键点是在设计阶段就考虑到如何做好测试;二是流程,关键点做好协作和自动化;三是工具,关键点是实时、预测和智能。

1. 策略:用灵活的测试方案实现成本优化

首先,在测试策略方面,在芯片设计开始时,就要考虑到如何达到零质量缺陷的效果,这需要在初期考虑测试方案的设计和策略,以平衡成本。

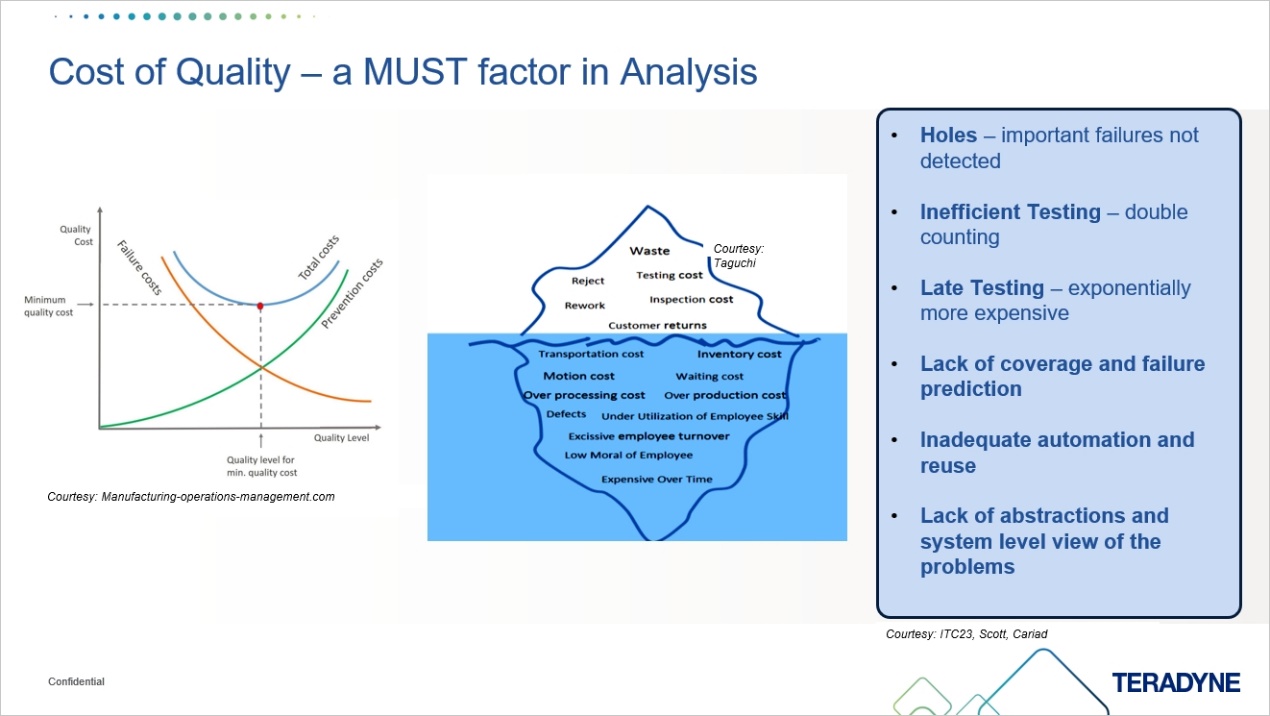

虽然用在汽车中的芯片都叫车规芯片,但其实每种芯片要求标准和成本不同。实际上,质量与成本相关联,质量等级越高,失效成本就会降低,但相应的就要做一些预防性的提前检测,从而拉高前期成本。此外,因质量问题而带来的客退、测试成本等显性成本之外,库存成本、运输成本、人员变动成本等隐性成本的影响要比显性成本大得多。

最终,整体成本会呈现“浴盆曲线”,其最低点就是两种成本的交界点,不同芯片的权衡都有所不同。比如说,自动驾驶芯片与汽车行驶直接相关,一旦出问题,就是人员安全问题,所以要求质量等级更高。再比如,座舱芯片可以通过后装市场来增级,质量要求也没有那么高。

芯片测试主要分为Wafer Sort(WS,晶圆测试)、Partial Assembly(PA,部分封装)、Final Test(FT,成品测试)、System Level Test(SLT,系统级测试)四个阶段,当然晶圆测试、成品测试完成后并不代表结束,测试是贯穿汽车电子全产业链的重要环节。

对芯片来说,如果很多问题在晶圆测试阶段就能检测出来,到了成品测试时就不需要再去检测,这种测试前移和后移就指的就是“FLEX Test”。

对汽车芯片来说,一颗芯片售价中,测试成本始终与封装、工艺成本相比占比较小,发现问题越早,就能把测试项从最终测试前置,省掉封装成本。“因此,从成本角度来说,能不能前移多一点,这就要求机台本身有非常好的稳定性和可重复性,同时测试能力和覆盖率能够达到这样的要求,才有可能实现FLEX Test。”Felix Huang如是说。

当然,测试本身也没有那么简单,整个流程需要不断测量和分析数据才能知道哪些项目能够前移,FLEX Test背后拥有不同的逻辑,从来没有固定的答案,必须考虑哪个阶段测量什么测试项才能形成最优解,针对不同公司、不同芯片做不同分析。

但实际,多数情况IC设计人员与ATE测试人员隔行如隔山,沟通过程或许存在不可避免的代沟。泰瑞达的专用软件工具PortBridge就是解决这种问题,为双方搭建起沟通桥梁,一面是测试机,另一面是EDA工具;IC设计人员操作EDA工具,即可直接控制测试机进行晶圆测试或者成品测试,根据结果实时在线调优,同时也可以藉由PortBridge工具通过ATE直接访问每个IP并进行调试,加速IP与整个芯片融合。

2. 流程:用自动化、智能化的工具减少人为问题

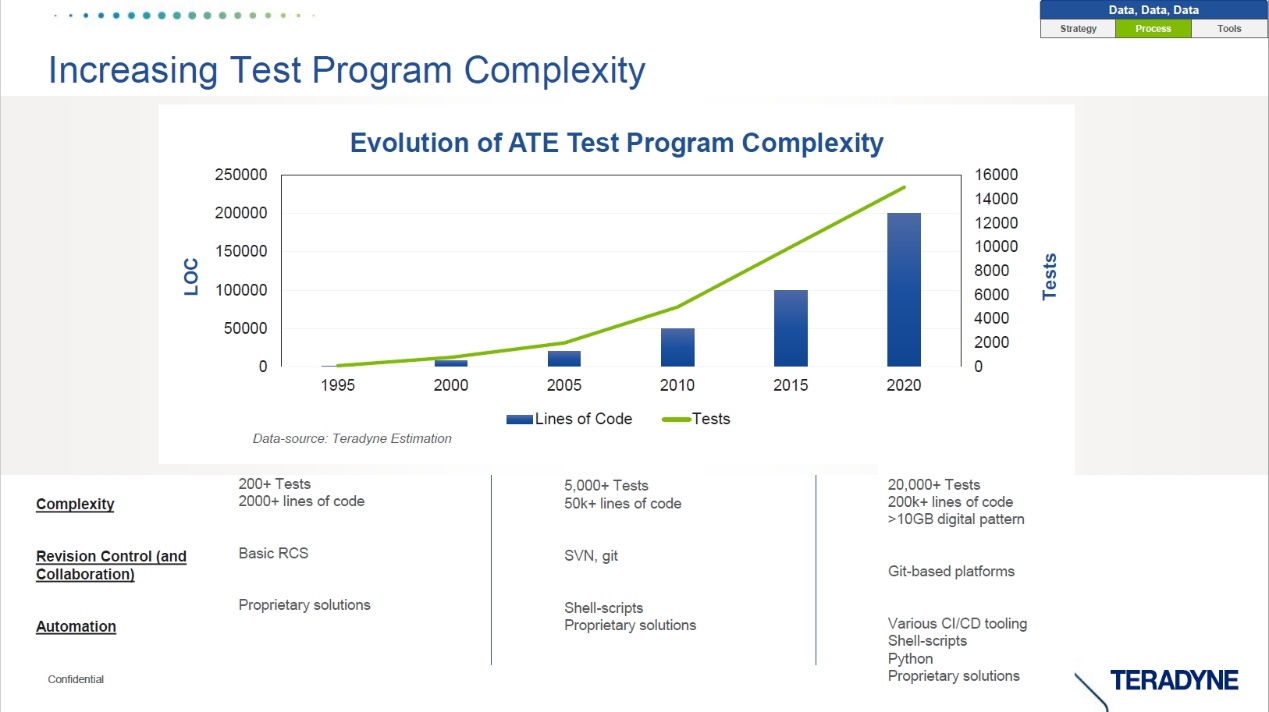

从1995年到2020年,芯片功能愈加复杂,测试程序复杂度随之增大,早期一颗SoC芯片可能拥有200个测试项,代码量约一两千行,一个或几个测试工程师就能完成测试工作。而现在则至少拥有2万行代码,代码量达到几个到几十个Giga的水平,开发测试程序基本都是由团队协作开发,最后整合调试。

因此,在这样的进化过程中,为了减少开开发周期,加速产品上市,就需要整个流程拥有自动化、智能化的工具,减少因为人为因素带来的问题。

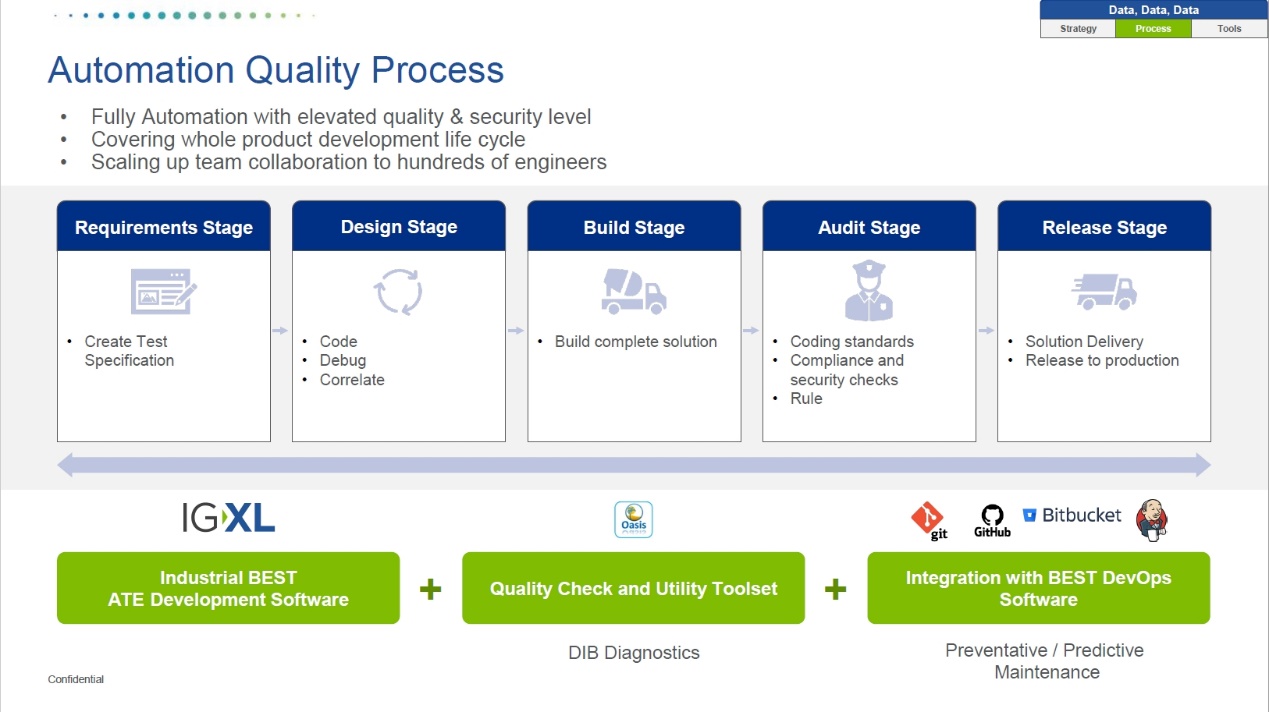

泰瑞达则有不同的软件支持,其中IG-XL软件则是ATE行业中口碑最好的开发软件之一,该软件兼具实用性、易用性和稳定性。

基于IG-XL软件,泰瑞达还拥有一款辅助工具Oasis,可以帮助检测开发代码质量,比如在Offline阶段运行Oasis工具,可以自动检测不同工程师的代码有没有写错,有没有冗余。

多人开发方面,泰瑞达内部拥有全流程管理系统DevOps(Development Operation),该系统自2020年开始引入,这是一个完全自动化的系统,比如说,工程师开始开发一个测试程序时,从Offline阶段就会自动调用Oasis中的Offline检测工具,生成报告,将问题发到相关工程师邮箱,直到把报告中问题全部修复以后,才会进入到下一个阶段。

3. 工具:实时、可预测、智能的分析

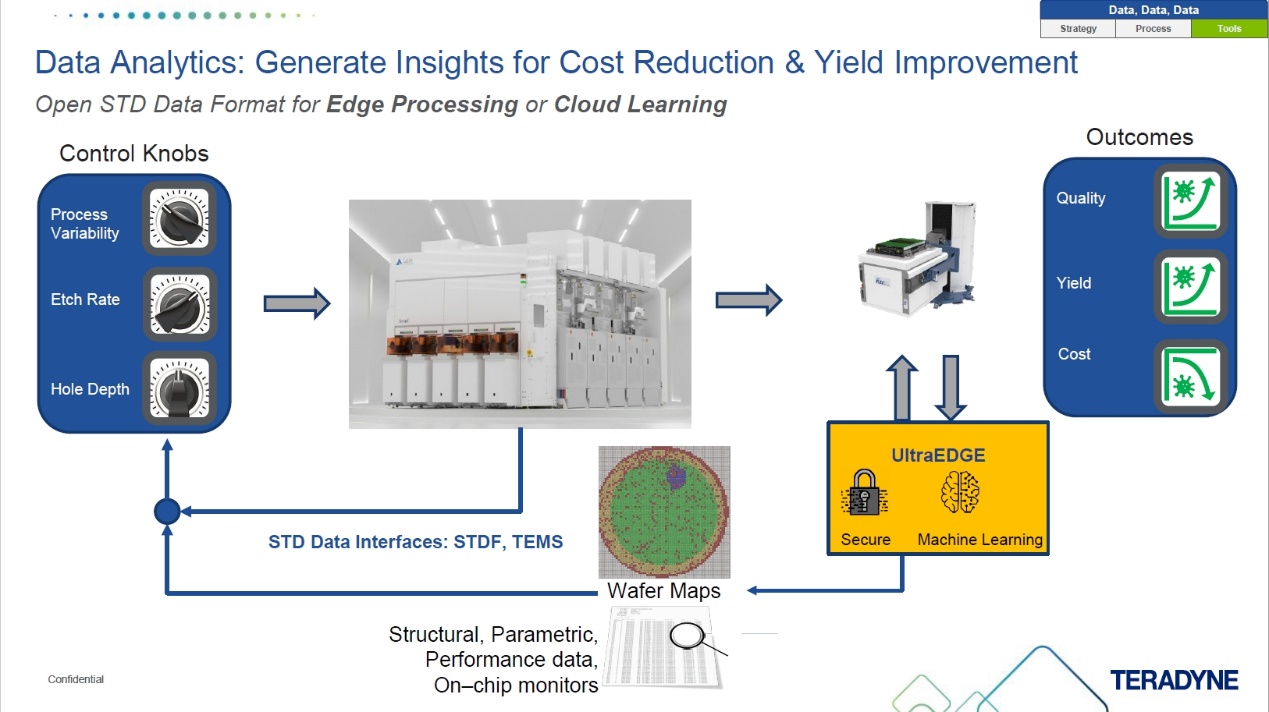

对测试整个流程来说,流动在其中的“血液”便是数据,不同工艺中,不同的控制按钮、不同的变量和不同的参数都会流向ATE测试机,除了标准数据(一般来说有两种格式STDF和TEMS),Fab可以根据实际反馈的数据,来调整工艺参数,优化工艺流程。

归根结底,零质量缺陷的支撑点就是海量数据,要想让这些数据真正产生作用,就要做到实时性、可预测性、智能性的分析。尤其对车规芯片来说,数据则更为重要。

泰瑞达的UltraEDGE便是配套的服务器,它内部既包含自建的FDE(故障检测引擎,Fault Detect Engine)工具,也可安装第三方数据分析软件,如OptimalPlus、PDF数据管理软件,在其中进行加密和机器学习,对抓到的原始数据进行分析,把潜在缺陷反馈给Foundry,最终提升良率,降低成本。

FDE是泰瑞达已经推出的一款大数据分析软件,它可以将前面测试结果进行统计分析,并比较原有测试结果。早期,它采用的是Static PAT(SPAT),现在车规更多采用的是Dynamic PAT(DPAT),即动态分析。

值得一提的是,泰瑞达在3年前就成立了专门的研究团队,研究AI怎样加速测试结果分析,同时在Ultra EDGE Server、FD Engine、Oasis辅助工具中都使用了AI技术。

解决车规芯片的测试难题

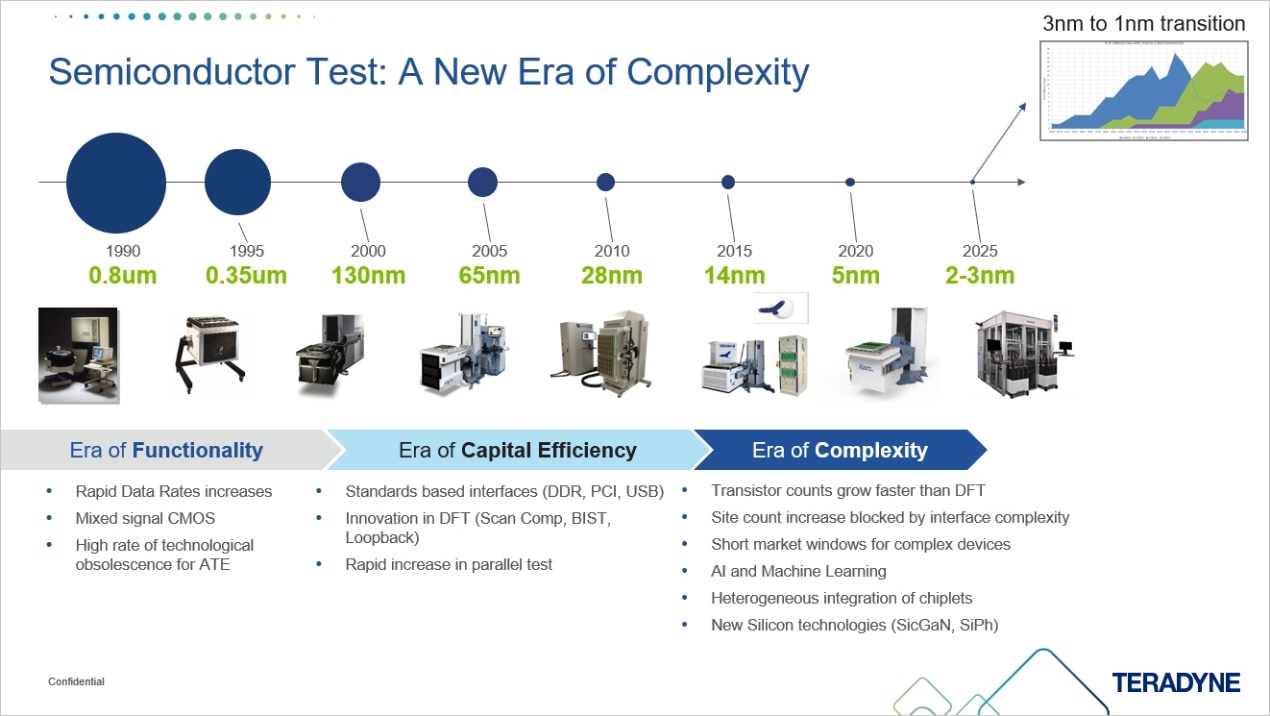

如今芯片密度在跟随摩尔定律不断膨胀,极速的制程演进也会为汽车芯片测试带来更多挑战。根据泰瑞达亚太区销售副总裁Richard Hsieh的分享,过去半导体测试设备发展,可以分为三个阶段。

1990年~2000年,是功能时代,制程工艺集中在0.8μm~0.13μm,芯片搭载功能越来越多,传统测试平台逐渐被淘汰;2000年~2015年,是效率时代,随着工艺从0.13μm发展到14nm,并行测试需求扩大,4工位、8工位测试成为标配;2015年至今,是新兴时代,制程工艺步入3nm,此时单纯的芯片测试只是基础性功能,trim(微调)等更多复杂性功能成为标配,这些功能可以有效减少设计时间、提高产品良率。

现在,行业正向1nm演进,也在探索如何在CMOS的制程里制造出数字或“数字+混合信号+RF”,相对应的,也向测试端提出更快的测试速度、更低的测试成本和更快的上市时间等要求。

“测试产业是一个重资本投资的产业,怎样在投资上获得很好的回报是关键问题。”Richard Hsieh表示,多数人在做资本采购时,都会算固定折旧,当直接成本被折旧抵消,其中大部分就是间接成本。所以对机台来说,怎样设计让它能够提高它的产品生命周期,以及利用率都是重要的课题。

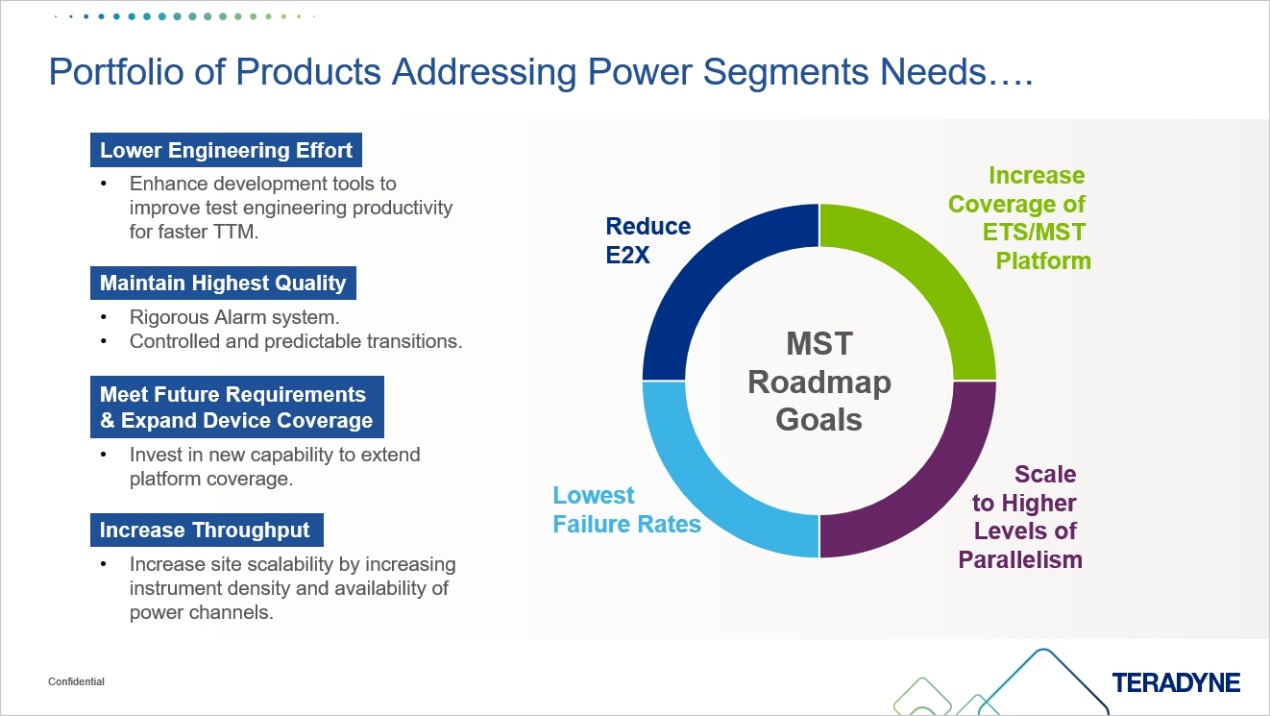

泰瑞达针对汽车电子市场进行了多元化布局。公司旗下的J750、UltraFLEX、EAGLE等产品可以帮助客户降低工程成本,提升系统鲁棒性,同时用更少的测试单元提供更高产出,并加大良率把控,为客户提供质量保障和成本有优势。

泰瑞达从1990年到2025年都推出了不同的平台,令人惊喜的是,一些客户现在都还在用在90年代推出的机台,尤其1995年推出的J750,现在还有很多客户都在使用量产。

当然,这也并非说明J750一成不变,20年以来,它已经经过了三代升级,每一代板卡密度都在翻番,与此同时,电源模块也在不断跟进,随着需求不同增长,升级速度也开始逐渐缩短。为什么J750如此经久耐用,实际上,它自推出设计指标覆盖就非常广泛,稳定性指标MTBF(Mean Time Between Failure)也非常好,可以做到运行一年一块板卡也不坏。按照利用率来推算时间,可以达到8760个小时。

UltraFLEXplus平台于2019年推出,其设计生命周期是20年,中间小版本升级是5年,当然其大框架方向是不变的,泰瑞达在设计平台之初,就按照一个开放、可升级、可进化的框架进行。

对于测试来说,实质上无论车载芯片、工业芯片,对于测试机供应商的厂商来说,测试本质并没有发生变化,那么车规芯片测试究竟有有什么不同?

Felix Huang表示,对泰瑞达来说,车规芯片和工业芯片测试设备都类似,唯一不一样是后面的数据处理,比如UltraEDGE、FD Engine统计分析,芯片测试要求提高了,不只是看性能规格测试,而是要看它的统计分布、每个晶圆上的物理分布、最低良率要求、每个温度下的要求,这些都需要大数据分析进行支持。

目前为止,泰瑞达已经利用FD Engine帮助国内几家国产芯片设计公司,包括细分领域龙头,实时监控测试过程变化。泰瑞达已扎根中国20多年,未来,除了持续在国内大方向上发展,汽车也是重要方向。

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读:

国际电子电路(深圳)展览会HKPCA Show下周三开幕,会议大咖云集,精彩议题抢先揭晓