【导读】在高速数字电路与高频模拟系统主宰电子设计的今天,PCB叠层设计早已超越简单的“线路承载”功能,成为决定产品性能、可靠性与成本的核心环节。合理的叠层结构如同摩天大楼的地基,为信号完整性(SI)、电源完整性(PI)和电磁兼容性(EMC)提供坚实保障;而失败的叠层方案则可能引发信号畸变、电源噪声、辐射超标等一系列棘手问题。本文将深入剖析PCB叠层设计的关键性,揭示常见设计“深坑”,并提供不同应用场景下的优选方案与实用避坑策略。

在高速数字电路与高频模拟系统主宰电子设计的今天,PCB叠层设计早已超越简单的“线路承载”功能,成为决定产品性能、可靠性与成本的核心环节。合理的叠层结构如同摩天大楼的地基,为信号完整性(SI)、电源完整性(PI)和电磁兼容性(EMC)提供坚实保障;而失败的叠层方案则可能引发信号畸变、电源噪声、辐射超标等一系列棘手问题。本文将深入剖析PCB叠层设计的关键性,揭示常见设计“深坑”,并提供不同应用场景下的优选方案与实用避坑策略。

一、 为什么PCB叠层设计如此关键?

PCB叠层设计绝非简单的层数堆砌,其核心价值在于通过精密控制以下要素,满足复杂电路的物理与电气需求:

1. 信号完整性(SI)的守护者:

●可控阻抗: 高速信号(如DDR, PCIe, USB3+)要求精确的传输线阻抗(如50Ω, 90Ω差分)。叠层决定了信号层与参考平面(电源或地)的距离、介质厚度及材料特性(Dk值),直接影响特征阻抗计算与实现精度。阻抗失配会导致信号反射、过冲/下冲、时序抖动。

●减少串扰: 相邻信号层或同层走线过近会引发电磁耦合(串扰)。合理的叠层通过增加层间距、在关键信号层间插入参考平面(屏蔽层)、采用正交走线策略等,有效隔离敏感信号。

●提供低损耗回路: 高频信号的返回电流倾向于在参考平面上紧贴信号走线下方流动(最小回路电感)。叠层需确保每个信号层都有完整、邻近的参考平面,为返回电流提供低阻抗路径,减少电磁辐射和环路电感。

2. 电源完整性(PI)的基石:

●低阻抗电源分配网络(PDN): 叠层通过设置专门的电源层(Power Plane)和地层(Ground Plane),并尽量靠近(形成平板电容),为芯片提供低阻抗、低感抗的电源通路。核心电压(如Vcore)通常需要紧邻地平面。

●去耦电容有效性: 叠层结构影响电源平面与地平面之间的固有电容以及去耦电容的安装位置环路电感,决定高频噪声的滤波效果。不当的层间距或平面分割会削弱去耦效果。

3. 电磁兼容性(EMC)的屏障:

●屏蔽与抑制辐射: 完整的地平面和电源平面是最有效的屏蔽层。合理的叠层(如“地-信号-信号-地”的对称结构)能将高速信号产生的电磁场约束在板内,减少向外的辐射(RE)。同时也能降低外部干扰(如ESD、射频)对内层敏感电路的影响(抗扰度RI)。

●控制共模电流: 良好的参考平面设计有助于控制共模电流路径,减少共模辐射。

4. 热管理与结构可靠性:

●散热路径: 大功率器件产生的热量可通过过孔(Thermal Via)传导至内层平面或外层散热铜箔。叠层设计需考虑这些热通道的布局。

●抑制翘曲: 对称的叠层结构(如芯板与PP半固化片材料、铜厚分布对称)能有效平衡应力,减少PCB在制造和焊接过程中的翘曲变形风险。

5. 成本与制造可行性的平衡: 层数增加直接带来成本上升。叠层设计需在满足电气性能的前提下,选择最经济的层数和材料组合。同时需考虑工厂的加工能力(如最小线宽/线距、层间对准精度、压合能力)。

二、 PCB叠层结构基础与关键要素

1. 核心组成部分:

●芯板(Core): 刚性基材(通常是FR-4玻璃纤维环氧树脂),双面覆铜。是叠层的骨架。

●半固化片(Prepreg, PP): 未完全固化的树脂浸渍玻璃布。在压合过程中熔化流动,填充空隙并粘合相邻层。其树脂含量影响最终介电常数(Dk)和厚度。

●铜箔(Copper Foil): 形成导线、焊盘和平面层。厚度常用盎司(oz)表示(1oz ≈ 35μm)。

●阻焊层(Solder Mask): 覆盖在表层铜箔上,绝缘防护,开窗处露出焊盘。

●丝印层(Silkscreen): 标识元件位置、方向等信息。

2. 叠层描述关键参数:

●层序(Layer Stackup Sequence): 各层(信号层S、电源层P、地层G)的排列顺序。是设计的核心。

●层厚(Thickness): 包括各层间介质(PP)厚度、芯板厚度、铜层厚度。决定阻抗和层间电容。

●介电常数(Dk, εr): 基材(芯板、PP)的电气特性,影响信号传播速度和阻抗计算。FR-4典型值约4.2-4.5(频率不同有差异)。

●损耗角正切(Df, tanδ): 基材的损耗特性,影响信号衰减(插入损耗)。高频高速应用需选择低Df材料(如M7NE, Megtron 6)。

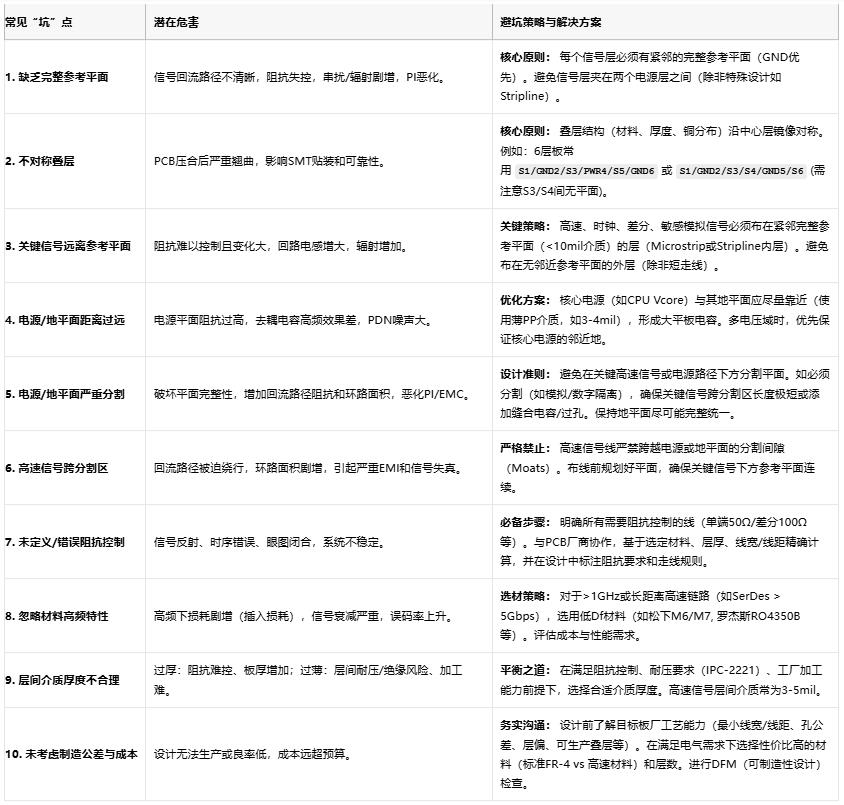

三、 PCB叠层设计避坑指南:十大常见“深坑”与对策

四、 不同应用场景的PCB叠层方案选择(含典型示例)

结语:叠层设计 – 没有最好,只有最合适

PCB叠层设计是一门融合电气工程、材料科学和制造工艺的精密艺术。不存在一种“放之四海而皆准”的完美叠层模板。成功的核心在于深刻理解电路的核心需求(速度、功耗、信号类型、EMC等级、成本),并据此做出精准权衡:

● 成本敏感型项目:4层板通常是性价比最优解,牢记对称叠层和参考平面完整性原则。

● 性能导向的高速系统:6层及以上是起点,优先选择Stripline布线,确保关键电源邻近完整地平面,必要时采用低损耗材料。

● 混合信号挑战:物理隔离(独立地平面)和单点接地是基石,层数需满足隔离和布线需求。

● 微型化诉求:拥抱HDI技术,叠层设计需与微孔工艺紧密结合。

避坑的关键在于预见性: 在设计初期就投入精力进行叠层规划,利用仿真工具(SI/PI/EMC)评估关键方案,并与可靠的PCB制造商紧密沟通其工艺能力和材料库。记住,一个经过深思熟虑、量身定制的叠层方案,是避免后期昂贵返工、确保产品一次成功并满足所有性能指标的“地基密码”。它将无形的电气规则转化为有形的物理结构,最终铸就稳定、可靠、高效的电子设备基石。

推荐阅读:

选型不再纠结!一文读懂力芯微、TI、ADI升压转换器核心差异

离座秒锁屏!意法半导体新推人体存在检测技术守护PC智能设备隐私安全