【导读】串扰是信号完整性中最基本的现象之一,在板上走线密度很高时串扰的影响尤其严重。我们知道,线性无缘系统满足叠加定理,如果受害线上有信号的传输,串扰引起的噪声会叠加在受害线上的信号,从而使其信号产生畸变。

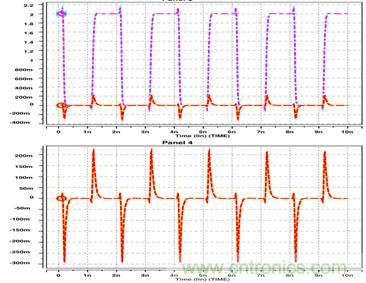

图1.串扰使得信号产生畸变

当串扰噪声叠加在受害信号的高低电平上时,会产生幅度噪声或影响眼图高度。当串扰噪声叠加在受害信号的跳变边沿位置时会产生边沿的抖动,进而影响时序或者是眼图宽度。从统计的角度来说,由于干扰源的不确定性,串扰噪声一般会同时影响信号的边沿和幅度。因此,对于串扰来说两个方面的影响都应该考虑。

串扰形成的根源在于耦合。在多导体系统中,导体间通过电场和磁场发生耦合。这种耦合会把信号的一部分能量传递到邻近的导体上,从而形成噪声。耦合的方式主要有两种:1、容性耦合。2、感性耦合。

容性耦合

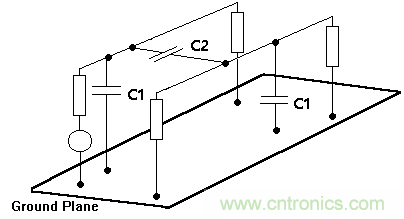

回忆一下我们所熟悉的平行板电容,两个规则平行板导体,周围充满介质就形成了一个电容器。对于PCB板上的情况,两条走线之间和参考平面之间也会形成电容器,图3中C1表示走线和参考平面之间形成的电容,C2表示两走线之间形成的电容。从电容的角度来看,当一条走线上电压变化时,相当于电容C2两端电压变化,电容C2充电邻近的导体(电容的另一端)上必然也会有电流,串扰随之产生。走线之间的电容与走线之间的间距密切相关,当间距增大时,耦合电容迅速减小,耦合作用急剧减弱。如果在两条走线之间放入另一根走线,这两跳走线之间耦合电容会进一步减小,这种现象正是使用隔离底线抑制串扰的出发点之一。

图2.容性耦合(Capacitive coupling)

感性耦合

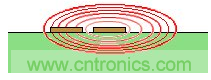

如果一条走线上有数字信号传输,在信号电平跳变过程中,即信号处于跳变边沿时,走线上电压不断变化,走线上的电流也不断变化,这样在走线周围产生变化的磁场,而变化的磁场在邻近走线上产生感应电流。这就是感性耦合。同样的拉开PCB板上走线的间距,能明显减小两天线之间的互感耦合。感性耦合机理如图3

图3.感性耦合(Inductive coupling)

推荐阅读: