【导读】可编程逻辑器件在数字系统的发展史中可以说是最亮的一笔。PLD能够完成任何数字器件的功能,用PLD来开发数字电路能够减少PCB面积,提高系统的可靠性,而且还大大减少了设计时间。由PLD延伸出的FPGA和CPLD都是可编程逻辑器件。

1 PLD发展过程

早期的可编程逻辑器件只有可编程只读存贮器(PROM)、紫外线可擦除只读存贮器(EPROM)和电可擦除只读存贮器(E2PROM)三种。由于结构的限制,他们只能完成简单的数字逻辑功能。

稍后,出现了一类结构上稍复杂的可编程芯片,即可编程逻辑器件(PLD),他能够完成各种数字逻辑功能。这一阶段(大约20世纪70年代中期)的产品主要有可编程阵列逻辑(ProgrammableArrayLogic,PAL),PAL由一个可编程的“与”平面和一个固定的“或”平面构成,或门的输出可以通过触发器有选择地被置为寄存状态。PAL器件是现场可编程的,他的实现工艺有反熔丝技术、EPROM技术和E2PROM技术。

20世纪80年代初期,在PAL的基础上,又发展了一种通用阵列逻辑(GenericArrayLogic,GAL),他采用E2PROM工艺,实现了电可按除、电可改写,其输出结构是可编程的逻辑宏单元,因而他的设计具有很强的灵活性,至今仍有许多人使用。

20世纪80年代中期,为了弥补上述缺陷,又先后推出了可擦除、可编程的逻辑器件(ErasableProgrammableLogicDevice,EPLD)。CPLD和FPGA,EPLD的集成度更高,设计更灵活,但内部连线功能较弱。

2 结构比较

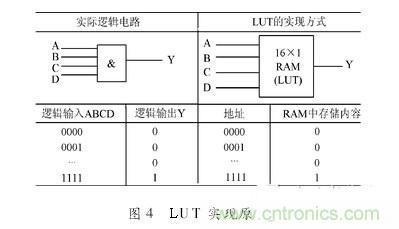

不同厂家对PLD的叫法不尽相同,但一般来说,把基于乘积项技术,FLASH(类似E2PROM工艺)工艺的PLD叫CPLD;把基于查找表技术,SRAM工艺,要外挂配置E2PROM的PLD叫FPGA。下面从内部结构对2者进行比较。

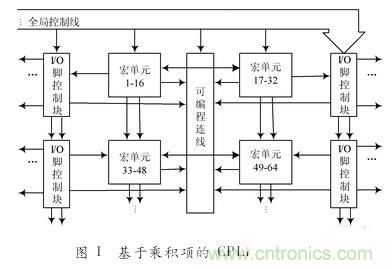

以altera的MAX7000为例,其他型号的结构与此都非常相似,这种PLD结构可分为3块:宏单元(marocell),可编程连线阵列(ProgrammableInterconnectArray,PIA)和输入输出I/O控制块。宏单元是CPLD的基本结构,由他来实现基本的逻辑功能。

2.2 基于查找表的FPGA结构

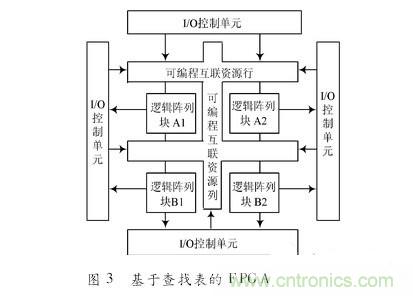

以Altera的FLEX/ACEX为例,这种PLD结构主要包括逻辑阵列块(LogicArrayBlock,LAB),输入输出块(InputOutputElement,I/OE),随机存储器块(RandomAccessMemory,RAM未表示出)和可编程行/列连线。其中一个LAB包括8个逻辑单元(LogicElement,LE),每个LE包括一个LUT一个触发器和相关的相关逻辑。LE是FLEX/ACEX芯片实现逻辑的最基本结构。如图3所示。

3 功能比较

尽管CPLD和FPGA都是PLD器件,有很多共同特点,但由于上节对CPLD和FPGA进行结构上比较的不同,在使用过程中仍然具有很大的差异。

一般认为CPLD是“逻辑丰富”型的,更适合完成各种算法和组合逻辑,FPGA是“时序丰富”型的,更适合于完成时序逻辑。换句话说,CPLD更适合于触发器有限而乘积项丰富的结构,而FPGA更适合于触发器丰富的结构。

(2)运行速度

一般认为CPLD是“逻辑丰富”型的,更适合完成各种算法和组合逻辑,FPGA是“时序丰富”型的,更适合于完成时序逻辑。换句话说,CPLD更适合于触发器有限而乘积项丰富的结构,而FPGA更适合于触发器丰富的结构。

(3)编程方式

目前的CPLD主要是基于E2PROM或FLASH存储器编程, 编程次数达1万次;FPGA大部分是基于SRAM编程其优点是可进行任意次数的编程,并可在工作中快速编程,实现板级和系统级的动态配置,因此可称为可重配置硬件。

4 CPLD/FPGA发展趋势

PLD在近20年的时间里已经得到了巨大的发展,在未来的发展中,将呈现以下几个方面的趋势:

(1) 向大规模、高集成度方向进一步发展

当前,PLD的规模已经达到了百万门级,在工艺上,芯片的最小线宽达到了0.13um,并且还会向着大规模、高集成度方向进一步发展。

(2) 向低电压、低功耗的方向发展

PLD的内核电压在不断的降低,经历5V→3.3V→.5V→1.8V的演变,未来将会更低。工作电压的降低使得芯片的功耗也大大减少,这样就适应了一些低功耗场合的应用,比如移动通信设备、个人数字助理等。

(3) 向高速可预测延时方向发展

由于在一些高速处理的系统中,数据处理量的激增要求数字系统有大的数据吞吐速率,比如对图像信号的处理,这样就对PLD的速度指标提出了更高的要求;另外,为了保证高速系统的稳定性,延时也是十分重要的。用户在进行系统重构的同时,担心的是延时特性会不会因重新布线的改变而改变,如果改变,将会导致系统性能的不稳定性,这对庞大而高速的系统而言将是不可想象的,带来的损失也是巨大的。因此,为了适应未来复杂高速电子系统的要求,PLD的高速可预测延时也是一个发展趋势。

(4) 向数摸混合可编程方向发展

迄今为止,PLD的开发与应用的大部分工作都集中在数字逻辑电路上,在未来几年里,这一局面将会有所改变,模拟电路和数摸混合电路的可编程技术得到发展。目前的技术ISPPAC可实现3种功能:信号调整、信号处理和信号转换。信号调整主要是对信号进行放大、衰减和滤波;信号处理是对信号进行求和、求差和积分运算;信号转换则是指把数字信号转换成模拟信号。EPAC芯片集中了各种模拟功能电路,如可编程增益放大器、可编程比较器、多路复用器、可编程A/D转换器、滤波器和跟踪保持放大器等。

(5) 向多功能、嵌入式模块方向发展

现在,PLD内已经广泛嵌入RAM/ROM,FIFO等存储器模块,这些嵌入式模块可以实现更快的无延时的运算与操作。特别是美国Altrea公司于2000年对可编程片上系统(SystemOnProgrammableChip,SOPC)的提出,使得以FPGA为物理载体、在单一的FPGA中实现包括嵌入式处理器系统、接口系统、硬件协处理器或加速器系统、DSP系统、数字通信系统、存储电路以及普通数字系统更是成为目前电子技术中的研究热点。

相关阅读:

如何实现高效并行的实时上采样?FPGA献计

菜鸟升级必备:通透了解FPGA设计流程

工程师入门首选:FPGA学习中必须注意的要点