【导读】IEEE 1588标准诞生于2002 年,主要定义网络分布式时钟的同步协议。测试与测量、电信和多媒体流处理等许多不同应用,都开始首选这种时钟同步方法。这种标准化时钟同步法成本效益高,支持异构系统,并可提供纳秒级同步精度。

本文介绍原版 IEEE 1588-2002 标准以及更新版本 IEEE 1588-2008 中的改进内容。由于IEEE 1588 在一些目标应用中越来越重要,因此 ADSP-BF5181 Blackfin® 嵌入式处理器中也集成专用硬件来支持IEEE 1588。本文将概要介绍其功能,并通过一个示例来展示利用ADSP-BF518 处理器解决方案获得的时钟同步性能结果。

现在几点了?

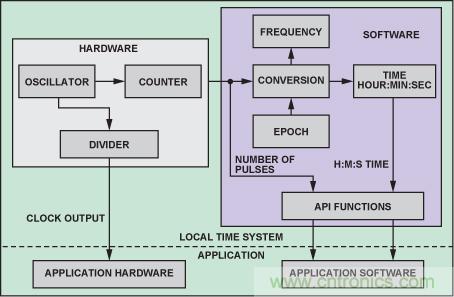

大多数系统都需要利用本振来维护自己的时间概念。图1显示硬件和软件如何组合,在系统内产生时间信息

图1. 本地计时

系统内的硬件和软件资源均可使用此时间信息。对于硬件,振 荡器时钟会产生一个或多个物理时钟信号(时钟输出),并可 利用这些时钟信号驱动或触发系统的其它部分。软件中维护的 时间通常称为"系统时间"。系统时间可以用时钟脉冲数或秒 / 纳秒的形式表示。系统软件利用振荡器时钟脉冲数及其频率 信息得出时间,并提供"应用程序编程接口" (API) 函数,软 件的其它部分可以使用这些函数检索并设置时间。如果需要绝 对时间,则所提供的时间将与预定义时间点,即基准时间点相 关联.

时钟同步

许多应用要求两台独立的设备以同步方式工作。如果每台设备 仅依靠自己的振荡器,则各振荡器的特性与工作条件差异将会 限制时钟同步工作的能力。一些简单可行的解决方案可以克服 这些限制,包括:

● 所有设备共用一个物理振荡器.这种方法仅对距离很近的分

● 所有设备均使用特性几乎完全相同的振荡器.由 于很难获得 几乎完全一样的振荡器,并确保性能不随时间飘移,因此这 种方法不可行。更重要的是,各振荡器的工作条件并不相

● 如果所有设备均通过一个通信网络(例如以太网)互连,则这些设备可以通过网络交换时间消息,根据单个"主"时钟 动态调整各自的时钟。利用传统的时间同步协议—— "网络 时间协议"(NTP),统中的每台设备根据它从 NTP时间服 务器获取的时间信息调整其时钟。然而,该协议只能实现毫 秒级同步精度。

IEEE 1588 定义了一个新协议,能够实现纳秒级同步精度。下 面讨论该标准如何实现这种水平的时钟同步。

IEEE 1588 有何作用

IEEE 1588 标准定义了一种时间同步协议,适用于地理位置分 散但通过某种通信技术(例如以太网)互连的设备。设备之间 通过交换时序消息,从而保持相同的绝对系统时间(用秒和纳 秒表示)。

要实现此目标,一个直观的方法是将一台具有"最佳"(最精 确)时钟的设备指定为"主时钟"设 备,让它向其它设备广播 其时间。其它设备将会调整各自的时间,与主时钟所发送的时 间保持一致。不过,这种解决方案也有几点不足:

1. 主时钟设备无法以极短的间隔广播时间,因此"从"时钟设备必须使用自己独立的"低劣"振荡器,在主时钟设备

2. 广播路径难免存在延迟,延迟幅度取决于通信技术,例如物理信号沿导线从一台设备传输至另一台设备所需的时 间。这种延迟会进一步扩大主时钟与各从时钟之间的失

3. 主时钟设备与各从时钟设备之间的广播路径存在差异,这会进一步降低各从时钟设备之间的同步精度。

IEEE 1588 要求通过测量路径延迟,解决第二个和第三个问 题。它还要求待调整的从时钟与主时钟保持步调一致,从而减 轻第一个问题。如果可能,使用更小的广播间隔和更高质量的 振荡器,可以进一步减轻第一个问题

IEEE 1588 如何测量通信延迟

IEEE 1588-20022 定义了四种消息 Sync、 Followup、 DelayReq和 DelayResp,用来测量前向(主时钟至从时钟)和后向(从 时钟至主时钟)路径的通信延迟。更新版本IEEE 1588-2008,3 还提供其它机制,新增三种消息 PdelayReq、PdelayResp和PdelayRespFollowup,来测量"点对点延迟"。

这些消息中,Sync、DelayReq、PdelayReq 和PdelayResp 是所谓"事件"消息,在离开和到达一台设备时必须加上"时间 戳"(记录本地时间)。给分组加上时间戳的方法有两种

1. 消息由软件处理时出现软件时间戳。通常出现在消息的接收/发送"中断服务程序"(ISR)中,该时间戳为系统时间的当前值。

2. 消息实际到达或离开设备时出现硬件时间戳。该时间戳操作由硬件执行,硬件会维护自己的连续时间信息。

两种时间戳方法均为IEEE 1588 所接受,但硬件时间戳的精度明显更高,如下文所述。

主时钟设备到从时钟设备的延迟

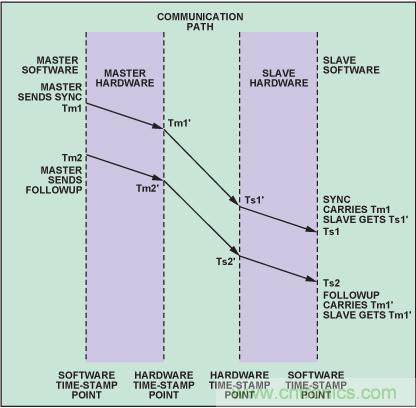

消息Sync 和Followup 由主时钟设备发送,从时钟设备负责接 收这些消息,并计算主时钟设备到从时钟设备的通信路径延迟.

图2 中,在时间点 Tm1,主时钟设备软件读取当前本地系统 时间(Tm1,软件时间戳),将其插入 Sync 消息中,并送出 该消息。该消息在稍 后的时间点 Tm1'''' 离开主时钟设备,该时 间点为硬件时间戳。该消息在时间点 Ts1'''' (从时钟设备本地时间)到达从时钟硬件,从时钟设备软件在稍后的时间点 Ts1 收到该消息。该软件将读取硬件时间戳以获得 Ts1''''。如果没有通 信延迟,Ts1'''' 应等于(Tm1'''' + Tms),其中 Tms 为主时钟与从时 钟之间的时间差。该协议的最终目标是补偿此时间差.

图 2. 测量主时钟设备与从时钟设备之间的通信延迟

发送 Sync 消息之后,主时钟设备软件通过时间戳单元读取 Sync 消息的离开时间 Tm1'''' ,将其插入 Followup 消息中,然后 在时间点 Tm2 发送该消息。从时钟设备软件在时间点 Ts2 收 到此消息。此时,从时钟设备软件有两个时间: Ts1'''' ( Sync 到 达时间)和 Tm1'''' ( Sync 离开时间)。主从路径延迟 Tmsd 由 公式 1 确定。

从时钟设备到主时钟设备的延迟ce

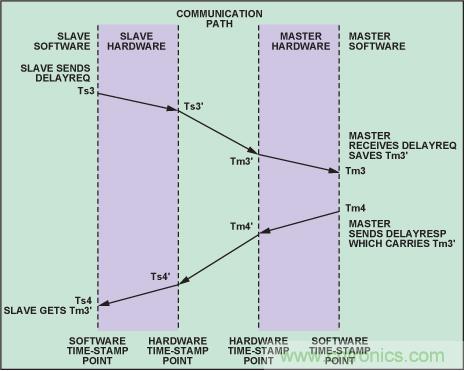

从时钟设备发送 DelayReq 消息,主时钟设备予以响应发送 DelayResp 消息。利用这些消息,从时钟设备可以计算从时钟 设备到主时钟设备的通信路径延迟.

在时间点 Ts3 (图 3 ),从时钟设备软件读取当前本地系统时 间 (T s3) ,将其插入 DelayReq 消息中,并送出该消息。发送该 消息之后,从时钟设备软件读取时间戳以获取消息离开时间 Ts3'''' ,并等待主时钟设备的响应。

图 3. 测量从主通信延迟

DelayReq 消息在稍后的时间点 Tm3'''' 到达主时钟设备,由主时 钟设备软件在时间点 Tm3 处理。然后,该软件读取时间戳以 获取到达时间 Tm3'''' ,将其插入 DelayResp 消息中,并在时间 点 Tm4 发送至从时钟设备。当从时钟设备软件在时间点 Ts4 收到 DelayResp 消息时,它可以提取时间 Tm3'''' ,并通过公式 2 计算从主通信延迟 Tsmd 。

公式 1 和公式 2 中均有一个未知变量,即主从时间差 Tms ,因 此无法单独求得 Tmsd 或 Tsmd 。但是,如果我们合理地假设 通信路径是对称的,即

——这是IEEE 1588 成立的关键假设——那么,将公式1 与公式 2 相加可以得出

由于从时钟设备寻求与主时钟设备同步,因此所有这些计算 均由这些设备执行。从时钟设备从主时钟设备的 Followup 消 息获得 Tm1'''' ,从其 Rx (接收)时间戳获得 Ts1'''' ,从其 Tx (发 送)时间戳获得 Ts3'''' ,并通过主时钟设备的 DelayResp 消息获 得 Tm3''''.

如何计算从时钟与主时钟的时间差

一旦获得通信路径延迟 Td ,便可利用公式 1 或公式 2 轻松计 算从时钟与主时钟的时间差,如公式 5 和公式 6 所示

如何调整从时钟设备的时间

知道与主时钟的时间差之后,各从时钟需要调整自己的本地时 间,与主时钟保持一致。该任务包括两方面。第一,从时钟设 备需要加上时间差以调整绝对时间,使其时间在此刻与主时钟 时间完全一致。第二,从时钟设备需要调整各自的时钟频率, 与主时钟的频率保持一致。我们不能单靠绝对时间,因为时间 差仅在一定期间内应用,可能是正值,也可能是负值;调整的 结果是从时钟时间向前跳跃或向后倒退。因此,在实际操作 中,调整分两步执行:

1. 如果时间差过大,例如

2. 如果时间差较小,则使从时钟的频率改变某一百分比.

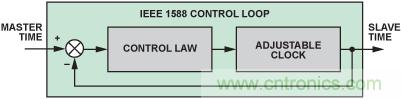

一般而言,该系统会变成一个控制环路,其中主时钟时间是参 考命令,而从时钟时间是跟踪主时钟时间的输出,二者之差驱 动可调整时钟。可以使用 PID 控制来实现特定跟踪性能,这 是许多 IEEE 1588 实施方案常用的方法。图 4 显示了这种控制环路.

图 4. IEEE 1588 控制环路.

点对点延迟

修订版 IEEE 1588-2008 引入了新的机制来测量路径延迟,称 为"点对点" (P2P) 延迟。与之相比,上文讨论的主从机制则 是"端对端" (E2E) 延迟。在支持 IEEE 1588-2008 的网络中, 主时钟设备可以与从时钟设备直接相连,或者隔几个中继站 (级)相连。 E2E 延迟实际上是主时钟设备到从时钟设备的 "总"延迟,包括其间的所有中继站在内。但是, P2P 延迟则 仅限于两个直接相连的设备。通信路径的总延迟等于所有中继 站的 P2P 延迟之和。从确保路径对称性的角度看, P2P 机制可 提供更高的精度.

如上文所述, IEEE 1588-2008 新增了 PdelayReq 、 PdelayResp 和 PdelayRespFollowup 三种消息来测量 P2P 延迟。这些消息 的工作方式与上文所述方式相似,详情请看参考文献3。

影响同步性能的因素

精心 设计的 IEEE 1588 设备能够实现高度精确的时钟同步,但 也必须了解直接影响同步性能的主要因素,其中包括:

1. 路径延迟: 如上文所述, IEEE 1588 的路径延迟测量假设通 信路径延迟是对称的,即前向路径的传输延迟与后向传输 延迟相同。此外,在延迟测量期间,延迟不应变化。测量 期间延迟变化会导致不对称和延迟抖动,这将直接影响同 步精度。虽然无法在 IEEE 1588 设备的边界之外控制延迟对 称性和抖动,但如果测量基于硬件时间戳,则可在设备内 改善路径对称性和抖动。由于中断延时、环境切换和线程 调度,软件时间戳会导致明显的抖动,而硬件时间戳则不

2. 时钟的漂移和抖动特性:: 主时钟的频率和相位代表跟踪控 制系统的输入,从时钟则是控制对象。主时钟的任何时变 行为都会扰动该控制系统,导致稳态和瞬态两种误差。因

3. 控制法则: 从时钟调整如何校正从时钟设备的时间误 差取 决于控制方法。控制法则参数包括建立时间、过冲和稳态

4. 时钟分辨率: 如图 1 所示,本地时间的分辨率由时钟频率 决定;最小时间增量为时钟信号的一个周期。 IEEE 1588- 2002 支持 1 ns 的时间分辨率, IEEE 1588-2008 则支持 2 -16 ns 的时间分辨率。 2 16 (!) GHz (甚至 1 GHz )的时钟是不 现实的。本地时钟的量化会影响本地时间测量和控制的精

5. Sync 消息的发送周期: 从时钟的更新频率最终会影响同步 精度。因为时间误差是从时钟频率误差的整体累积值,所 以发送周期越长,下一个 Sync 所观察到的时间误差一般会

6. 延迟测量的频率: 以预期相邻采样点之间延迟没有明显变 化的间隔时间,定期执行延迟测量。如果 IEEE 1588 网络 的延迟变化较大,则增加延迟测量频率可以改善时钟同步 性能。

哪个是主时钟?

在考虑如何精确确 定主时钟设备与从时钟设备之间的时间差之 后,下一个相关问题是:在成百上千台互连设备中,如何确定 哪一台设备充当主时钟。

IEEE 1588 定义了一种称为"最佳主时钟" (BMC) 算法的方 法,用于选择主时钟设备。这种方法要求 IEEE 1588 网络的每 台设备均提供一个数据集,描述其本地时钟的性质、质量、稳 定性、唯一识别符和首选设置。当一台设备加入 IEEE 1588 网 络时,它会广播其时钟的数据集,并接收所有其它设备的数据 集。利用所有参与设备的数据集,每台设备均运行同一 BMC 算法,以确定主时钟及其自己的未来状态(主时钟或从时 钟)。由于所有设备均采用同样的数据独立执行同一算法,因 此结论将会相同,设备之间不需要进行任何协商。有关 BMC 算法的更多详细信息,请看参考文献 2 和 3 。

ADSP -BF51 8 处理器支持 IEEE 1588

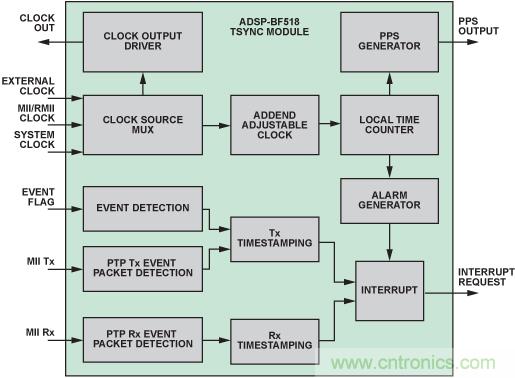

ADI 公司 Black fi n DSP 系列最近新增一款产品: ADSP-BF518 处理器。像前款产品 ADSP-BF537,4 该处理器内置"以 太网媒体访问控制器" (EMAC) 模块。它还具有 TSYNC 模 块,进一步扩展了支持 IEEE 1588 标准 EMAC 功能的能力; 还提供其它额外特性,可支持以太网的各种 IEEE 1588 应用。 图 5 显示了 TSYNC 模块的框图。 ADSP-BF51x Blackfin 处理 器硬件参考提供了更多信息5

图 5. ADSP-BF518 处理器 TSYNC 模块的框图。

分组检测

ADSP-BF518 处理器可以检测 IEEE 1588 的所有事件消息,包 括送入和送出的分组,并为其提供硬件时间戳。因为事件消息 时间戳的精度及其提取位置会影响路径延迟的对称性和稳定 性要求,所以 IEEE 1588 系统的精度在很大程度上取决于这二 者。 ADSP-BF518 的 TSYNC 模块持续监控 MAC 控制器与以 太网"物理接口收发器" (PHY) 之间的硬件接口,即"媒体独 立接口" (MII) ,并且只要检测到事件消息,就会产生硬件时 间戳,这一功能可提高 ADSP-BF518 的同步精度。

事件消息检测功能是可编程的,基本配置有两种:支持 IEEE 1588-2002 (默认状态)或支持 IEEE 1588-2008 。此外,这种 可编程能力还支持将来版本的 IEEE 1588 ,以及其它要求时间 戳的一般协议,包括配置为给进出处 理器的每个以太网分组加 上时间戳。

灵活的时钟源

本地时钟的属性对于 IEEE 1588 系统的性能很重要。为了满足 各种不同应用的要求, ADSP-BF518 处理器可提供三种本地时 钟源选项:系统时钟、外部时钟或以太网时钟。如果应用具有 特定时钟要求,则可以选择"外部时钟",并提供定制时钟 源。如果主时钟设备与从时钟设备"背靠背"连接,由于"以 太网时钟"来自以太网线路,而且两台设备采用同一时钟工 作,因此该时钟选项可以提供良好的精度。一般应用可以选择 处理器的"系统时钟"作为时钟源。

所选源时钟也由 TSYNC 模块驱动,通过特定引脚 Clockout 作 为处理器输出,系统的其它部分可利用该输出提供本地时间信息。

PPS 输出

"每秒脉冲" (PPS) 信号是时间信息的物理表示。它名义上是 一个 1-Hz 信号,在每个 1 秒转换时间发出一个脉冲。它可用 来控制本地设备,或者在发生网络故障时提供辅助时间通道。 它也可以 用于测试。两台设备的 PPS 信号之间的相位差是二 者时间偏移的物理量度

ADSP-BF518 处理器提供灵活的 PPS 输出。它利用可编程"开 始时间" (PPS_ST) 和周期 (PPS_P) 产生一个在时间 (PPS_ST + n × PPS_P) 发出脉冲的信号,其中 n = 1, 2, 3 ...。基本用法是 将 PPS_P 设置为 1 秒,并将 PPS_ST 设置为用秒数表示的将来 任一时刻,从而产生 PPS 信号。参考基本用法,可以利用这 种 PPS 输出功能产生具有可编程频率和开始时间的周期性信号。

辅助快照

一些应用可能需要按照标志信号切换指示,给某一事件加上时 间戳。 ADSP-BF518 的 TSYNC 模块通过辅助"快照" 功能, 使用一个专用引脚来接收外部标志,以便实现这种请求。切换 标志将触发该模块捕捉时间戳寄存器中的当前本地时间,供软 件访问。.

报警

如果应用需在特定时间执行一项任务,则可以用 TSYNC 模块 的"报警"功能。这项功能可以设置本地绝对时间,到达该时 间时,就会触发处理器中断。然后,软件便可利用中断执行任 务。

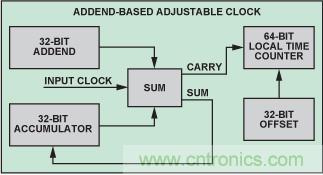

可调时钟

TSYNC 模块的可调时钟是一种"基于加数"的时钟。如图 6 所示,它获得一个固定输入时钟信号,并输出该输入的"盗取 脉冲"版本信号:对于每个输入时钟,"加数"的值增加到累 加器中,并且每次累加器溢出时,进位位就会驱动"本地时间计数器",从而产生以脉冲计数值表示的本地时间。更改加数 可以调整本地时钟的频率,因为加数决定累加器溢出的频率, 从而决定本地时间计数器递增的频率。如果输入时钟的频率为 Fin,且加数的值为A,则本地时钟频率为:

图 6. 基于加数的可调时钟

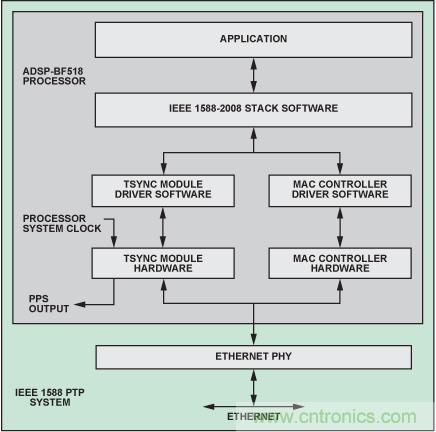

采用ADSP-BF518 处理器的 IEEE 1588 实施方案

ADSP-BF518 处理器上构建了一个完整的 IEEE 1588-2008 兼容系统,如图 7 所示。

图7. 采用ADSP-BF518 的 IEEE 1588 实施方案

处理器的 TSYNC 模块检测送入和送出的 IEEE 1588 消息, 并通过硬件给事件消息加上时间戳。由 I X X AT ( I X X AT Automation GmbH) 提供的 IEEE 1588 协议栈软件可实现标准 所要求的消息交换协议。它利用 TSYNC 驱动程序读取、写 入并调整 TSYNC 时钟,并使用 MAC 控制器驱动程序在以太 网 MAC 层(开放系统互连模型的第二层)发送和接收消息。它还可实现 P2P 延迟测量的控制法则和过滤。以太网 PHY 选择具有低抖动延迟特性的 National Semiconductor DP838486。为简明起见,TSYNC 模块时钟源选择处理器的系统时钟 (80 MHz)。

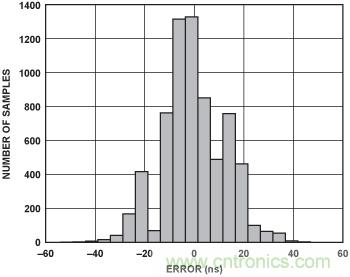

图 8. ADSP-BF518 上 IEEE 1588 系统的从时钟误差直方图

图 8 是两个完全相同的 ADSP-BF518 IEEE 1588 系统之间的 测量误差直方图,由此可看出该器件的时钟同步性能。在 约 1700 秒的时间内共进行了 6938 次测量。最终平均误差为0.015 ns,标准差为 12.96 ns。该测试所用的 Sync 消息间隔为0.25 秒。

结论

IEEE 1588 标准提供了一种高精度、低成本的分布式时钟同步 方法。虽然 IEEE 1588 并未明文要求硬件支持,但硬件辅助 消息检测和时间戳对于实现极高同步精度至关重要。 ADSP- BF518 为 IEEE 1588-2002 和 IEEE 1588-2008 提供硬件支 持,包括各种应用的支持功能。利用 ADSP-BF518 处理器和 IXXAT IEEE 1588-2008 协议软件实施 IEEE 1588 技术,已证 明可以实现高精度时钟同步。

参考电路

1 ADSP-BF518 数据手册。 http://www.analog.com/en/products/processors-dsp/blackfin/adsp-bf518.html.

2IEEE Std. 1588-2002. 网络测量和控制系统的精密时钟同步协 议 IEEE 标准。 http://ieeexplore.ieee.org/stamp/stamp.jsp?arnumber=1048550.

3IEEE Std. 1588-2008. 网络测量和控制系统的精密时钟同步协 议 IEEE 标准。http://ieeexplore.ieee.org/stamp/stamp.jsp?arnumber=4579760.

4ADSP-BF537 数据手册。 http://www.analog.com/en/products/processors-dsp/blackfin/adsp-bf537.html.

5ADSP-BF51x Blackfin 处理器硬件参考,0.1 版(初始版)。 2009 年 1 月。 Analog Devices, Inc.http://www.analog.com/media/en/dsp-documentation/processor-manuals/ADSP-BF51x_hwr_rev1.2.pdf.

6AN-1507 :DP83848 和 DP83849 100Mb 数据延时。 2006. National Semiconductor Corporation. http://www.ti.com/lit/an/snla084b/snla084b.pdf.

推荐阅读: