【导读】小编又为各位新手送福利啦!本次为大家带来的是关于DSP入门的初级指导,内容大多来自于新手们在初学时期比较关心的问题和最常见的疑问,详细到介绍初学需要看的文档哦!涵盖面十分之广。如果你也对学习DSP抱有兴趣,不妨来看看本篇文章来打下坚实的基础吧。

开发入门需要看的文档

讲述DSP的CPU,memory、program memory addressing、data memory addressing的资料都需要看、外设资源的资料可以只看自己用到的部分。

C和汇编的编程指南需要看。

汇编指令和C语言的运行时间支持库、DSPLIB、程序员向导、优化手册等资料。

如何开始软件开发

看CCS的使用指南;

明白CMD文件的编写;

明白中断向量表文件的编写,并定位在正确的地方;

运行一个纯simulator的程序,了解CCS的各个操作;

到TI网站下相关的源码,参考源码的结构进行编程;

取得一块评估板进行实际系统的软件调试;

DSP的C语言同主机C语言的主要区别

DSP的C语言是标准的ANSIC,它不包括同外设联系的扩展部分,如屏幕绘图等。但在CCS中,为了方便调试,可以将数据通过printf命令虚拟输出到主机的屏幕上。

DSP的C语言的编译过程为:C编译为ASM,再由ASM编译为OBJ。因此C和ASM的对应关系非常明确,非常便于人工优化。

DSP的代码需要绝对定位;主机的C的代码由操作系统定位。

DSP的C的效率较高,非常适合于嵌入系统。

如何能够相对较快地掌握DSP的硬件和软件的设计

建议选择合适的EVM,提供客户完整的原理图。

什么是DSP/BIOS

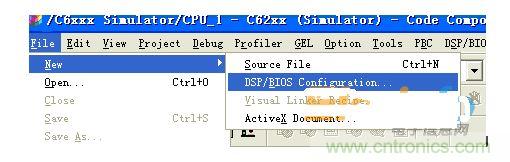

作为CCS强大开发工具的一个集成,DSP/BIOS是一个简易的嵌入式操作系统,它能大大方便用户编写多任务应用程序同时还能增强对代码执行效率的监控。DSP/BIOS工具已经具有实时操作系统的很多功能,如任务调度管理、任务间的同步和通信、内存管理、实时时钟管理、中断服务管理、外设驱动程序的管理等。使用DSP/BIOS开发DSP有2个重要的特点:1.所有与硬件相关的操作都必须借助DSP/BIOS本身提供的函数完成,开发者应避免直接控制硬件。2.带有DSP/BIOS功能的程序在运行时与传统开发的程序有所不同。在传统开发中程序是顺序执行,基于DSP/BIOS开发的程序由BIOS来调度,不再按照编写的顺序来执行。File-NEW-DSP/BIOSConfiguration。

图1

建立新的配置文件,根据开发的DSP不同芯片,对BIOS进行配置,如图1所示。

[page]

PCI同ISA的区别?

PCI是同步总线;ISA是异步总线。PCI的传输率较高。PCI可以即插即用。PCI的成本较高。

何为USB?

USB是通用串行总线的简称。它具有以下特点:传输速度快;连接方便;成本低。接口简单;兼容性好;可以适应于不同的计算机平台;开发容易;

CPLD同FPGA的区别?

CPLD的逻辑单元较大。

CPLD的容量较小。

CPLD的时序确定,延时可预测。

CPLD适合于组合逻辑和计算器设计。

USB的有哪些种类?

按种类分有:接口型:只提供接口。较便宜;使用复杂。芯片型:本身是一个单片机。使用简单。

按用途分有:Hub型:为了构成USBHub。设备型:设备端接口。主机型:主机端接口。

按速度分有:低速型:1.5M。用于鼠标、键盘等慢速计算机外设。全速型:12M。用于数据传输。高速型:480M。

5V/3.3V如何混接?

TIDSP的发展同集成电路的发展一样,新的DSP都是3.3V的,但目前还有许多外围电路是5V的,因此在DSP系统中,经常有5V和3.3V的DSP混接问题。在这些系统中,应注意:

DSP输出给5V的电路(如D/A),无需加任何缓冲电路,可以直接连接。DSP输入5V的信号(如A/D),由于输入信号的电压>4V,超过了DSP的电源电压,DSP的外部信号没有保护电路,需要加缓冲,如74LVC245等,将5V信号变换成3.3V的信号。

仿真器的JTAG口的信号也必须为3.3V,否则有可能损坏DSP。

为什么要片内RAM大的DSP效率高?

目前DSP发展的片内存储器RAM越来越大,要设计高效的DSP系统,就应该选择片内RAM较大的DSP。片内RAM同片外存储器相比,有以下优点:

片内RAM的速度较快,可以保证DSP无等待运行。

对于C2000/C3x/C5000系列,部分片内存储器可以在一个指令周期内访问两次,使得指令可以更加高效。

片内RAM运行稳定,不受外部的干扰影响,也不会干扰外部。

DSP片内多总线,在访问片内RAM时,不会影响其它总线的访问,效率较高。

[page]

为什么DSP从5V发展成3.3V?

超大规模集成电路的发展从1um,发展到目前的0.1um,芯片的电源电压也随之降低,功耗也随之降低。DSP也同样从5V发展到目前的3.3V,核心电压发展到1V。目前主流的DSP的外围均已发展为3.3V,5V的DSP的价格和功耗都价格,以逐渐被3.3V的DSP取代。

如何选择DSP的电源芯片?

TMS320LF24xx:TPS7333QD,5V变3.3V,最大500mA。TMS320VC33:TPS73HD318PWP,5V变3.3V和1.8V,最大750mA。TMS320VC54xx:TPS73HD318PWP,5V变3.3V和1.8V,最大750mA;TPS73HD301PWP,5V变3.3V和可调,最大750mA。TMS320VC55xx:TPS73HD301PWP,5V变3.3V和可调,最大750mA。TMS320C6000:PT6405B,PT6407E,最大3A。

如何选择外部时钟?

DSP的内部指令周期较高,外部晶振的主频不够,因此DSP大多数片内均有PLL。但每个系列不尽相同。

TMS320C2000系列:TMS320C20x:PLL可以÷2,×1,×2和×4,因此外部时钟可以为5MHz-40MHz。TMS320F240:PLL可以÷2,×1,×1.5,×2,×2.5,×3,×4,×4.5,×5和×9,因此外部时钟可以为2.22MHz-40MHz。TMS320F241/C242/F243:PLL可以×4,因此外部时钟为5MHz。TMS320LF24xx:PLL可以由RC调节,因此外部时钟为4MHz-20MHz。TMS320LF24xxA:PLL可以由RC调节,因此外部时钟为4MHz-20MHz。

TMS320C3x系列:TMS320C3x:没有PLL,因此外部主频为工作频率的2倍。TMS320VC33:PLL可以÷2,×1,×5,因此外部主频可以为12MHz-100MHz。

TMS320C5000系列:TMS320C54x:PLL可以÷2,×1-32,因此外部主频可以为0.25MHz-200MHz。TMS320VC54xx:PLL可以÷4,÷2,×1-32,因此外部主频可以为0.625MHz-50MHz。TMS320VC55xx:PLL可以÷4,÷2,×1-32,因此外部主频可以为6.25MHz-200MHz。

TMS320C6000系列:TMS320C62xx:PLL可以×1,×4,×6,×7,×8,×9,×10和×11,因此外部主频可以为11.8MHz-75MHz。TMS320C67xx:PLL可以×1和×4,因此外部主频可以为12.5MHz-41.7MHz。TMS320C64xx:PLL可以×1,×6和×12,因此外部主频可以为30MHz-75MHz。

如何选择DSP的外部存储器?

DSP的速度较快,为了保证DSP的运行速度,外部存储器需要具有一定的速度,否则DSP访问外部存储器时需要加入等待周期。

对于C2000系列:C2000系列只能同异步的存储器直接相接。C2000系列的DSP目前的最高速度为30MHz,为保证DSP无等待运行,需要外部存储器的速度<30ns。建议可以用的存储器有:CY7C199-15:32K×8,15ns,5V;CY7C1021-15:64K×16,15ns,5V;CY7C1021V33-15:64K×16,15ns,3.3V。

对于C3x系列:C3x系列只能同异步的存储器直接相接。C3x系列的DSP的最高速度,5V的为40MHz,3.3V的为75MHz,为保证DSP无等待运行,分别需要外部存储器的速度<25ns和<12ns。

建议可以用的存储器有:ROM:AM29F400-70:256K×16,70ns,5V,加入一个等待;AM29LV400-55:256K×16,55ns,3.3V,加入两个等待(目前没有更快的Flash)。SRAM:CY7C199-15:32K×8,15ns,5V;CY7C1021-15:64K×16,15ns,5V;CY7C1009-15:128K×8,15ns,5V;CY7C1049-15:512K×8,15ns,5V;CY7C1021V33-15:64K×16,15ns,3.3V;CY7C1009V33-15:128K×8,15ns,3.3V。

对于C54x系列:C54x系列只能同异步的存储器直接相接。C54x系列的DSP的速度为100MHz或160MHz,为保证DSP无等待运行,需要外部存储器的速度<10ns或<6ns。

建议可以用的存储器有:ROM:AM29LV400-55:256K×16,55ns,3.3V,加入5或9个等待(目前没有更快的Flash)。SRAM:CY7C1021V33-12:64K×16,12ns,3.3V,加入一个等待;CY7C1009V33-12:128K×8,12ns,3.3V,加入一个等待。

对于C55x和C6000系列:TI的DSP中只有C55x和C6000可以同同步的存储器相连,同步存储器可以保证系统的数据交换效率更高。ROM:AM29LV400-55:256K×16,55ns,3.3V。SDRAM:HY57V651620BTC-10S:64M,10ns。SBSRAM:CY7C1329-133AC,64k×32;CY7C1339-133AC,128k×32。FIFO:CY7C42x5V-10ASC,32k/64k×18。

在看过本篇文章之后,各位是不是更坚定了自己学习DSP的信心呢?小编将继续收集整理关于DSP初学阶段的一些疑问,帮助大家加快学习的步伐,并且走更少的弯路。