- 使用功率MOSFET封装技术解决计算应用的高功耗问题

- DrMOS方案采用四方扁平无引脚(QFN)封装

- 将MOSFET和驱动器封装在一起

对于主板设计师来说,要设计处理器电压调节模块(VRM)来满足计算机处理器永无止境的功率需求实在是个大挑战。Pentium 4处理器要求VRM提供的电流提高了约3倍。英特尔将其VRM指标从8.4版本升级到9.0版本,涵盖了新的功率要求,以继续追随摩尔(Moore)定律。

在过去的10年间,VRM电流要求一直在增加,正如英特尔所公布的,IccMAX从VRM9.0中的60A发展成驱动高端4核处理器的VRM11.0所要求的150A。与此同时,电流切换速率要求也有相当大的提高;芯片插座处的dI/dT从450A/μs增加到1200A/μs。这给电路设计带来了许多热性能和电气性能方而的挑战。

处理器功耗的增加自然也刺激了那些专注为客户提供增值服务的半导体厂商,推动他们开发各种创新的解决方案。VRM使用的功率MOSFET必须有尽可能低的导通电阻(Rds(on))、尽可能小的电感以及尽可能少的栅极电荷(Qg);这可从如下的功耗方程看出:

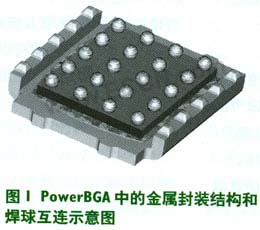

当工作频率增加到1MHz或者更高时,这些电气参数尤其重要。当然,功率MOSFET必须具有很好的热性能。随着MOSFET硅片技术的进步,封装技术逐渐成为性能提升的主要障碍。具体讲,人们发现传统的引线键合封装(如DPAK和SO-8)使用的细线会使部件的寄生电阻显著增加。在极端情况下,封装增加的寄生电阻大小会与硅片本身的相当。为此,MOSFET厂商开发出各种改良的封装,如飞兆半导体的PowerBGA(见图1)。这种封装完全不用引线键合技术,而是利用锡球和布有凸起的引线框,直接将硅片粘贴在印刷线路板(PWB)上。由于PowerBGA的铜帽有一小块散热片并利用空气对流,结点到环境的热阻较DPAK封装降低50%以上,这是因为PowerBGA为强制对流冷却提供了非常高效的散热途径。

VRM设计师喜欢相对较小的5mm×6mm SO-8封装。但由于这种封装是针对低功耗芯片设计的,因此不具备DPAK的热性能。量产的MOSFET多是SO-8大小的部件,并带有可焊接到PWB上的散热片。这类组件在全球的使用会越来越多,这些封装的热性能通常接近DPAK,而且在采用某些互连技术时,其寄生电阻和电感还可能更小,同时,PWB面积也减小一半。这也是许多电子设计师喜欢采用这种封装的原因。这是一个值得注意的进步;因为,典型的4相VRM 10产品具有一个高压侧MOSFET和两个低压侧MOSFET,总计12个。随着主板功能越来越多(如纳入音视频、无线网络等功能),可供VRM设计师使用的PWB空间越来越少,封装尺寸就成为设计师考虑的一个非常重要的因素。

虽然,出于成本或第二供货源考虑,许多设计最初都坚持采用传统的IPAK和DPAK封装,但为了满足高功率要求,这些新型的封装技术已经越来越多地成为必要的选择。现在已有许多5mm×6mm模塑引脚封装的供应商,这就解决了第二供货源的问题。

[page]

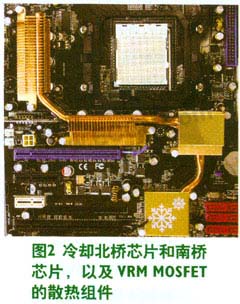

为了应对未来的需求,出现了双面封装技术,可让主板设计师对高性能应用的MOSFET进行散热处理,迫使MOSFET厂商成为总体解决方案的供应商。过去,台式电脑在处理器及北桥芯片和南桥芯片上使用散热片。虽然这在先前的主板设计中不常见(主要是成本原因),但对MOSFET进行散热已越来越常见。高级主板市场已经开始出现将北桥芯片和南桥芯片上的导热管连接到VRM的MOSFET散热片上的散热组件(见图2)。

在这些散热处理方案中,有些直接将散热片贴在DPAK的顶部。这种方案的效果非常差,因为塑料模件的热导率一般只有1 W/m-K,而铜在典型消费电子温度环境下的热导率接近400W/m-K。我们相信封装技术会响应这一发展趋势,而且MOSFET厂商在改进传统封装技术的同时,将会提供品种及功能更多(如双面冷却功能)的封装产品。

随着MOSFET越来越多地集成到主板的热系统中,主板设计师和MOSFET厂商必须更密切地合作。新的封装产品(可能是专有的或设有工业标准的)为PWB设计师开辟出新的设计天地,同时也要求MOSFET厂商协助客户使用新的产品,以确保客户充分发挥封装的性能。设计师挑选的MOSFET厂商必须了解针对应用的系统层面,清楚MOSFET周围组件的各种相关效应,了解组件上一块散热片能产生哪些效果和性能提升,了解表面贴装工艺及其在应用中的可靠性。

PWB面积的减小,以及节省成本的呼声越来越高,使得VRM设计师转而使用更高的开关频率。增加同步降压转换器的开关速度可允许使用更小的电感和电容。小电感和小电容的成本低,并且PWB占位面积更小。当然,天下没有免费的午餐。提高开关频率会因开关损耗增加而降低转换器的效率。MOSFET、控制器和驱动电路的需求均有所改变,需要提供这些组件的厂家提出新的解决方案。

英特尔已推出DrMOS技术规范,作为建立整体(即集成同步降压转换器的高压侧MOSFET、低压侧MOSFET及驱动器)封装解决方案标准的一种手段,该标准包括实现各种DrMOS兼容模块和控制器间互用性的各种电气和物理标准。

DrMOS方案采用8 mm×8mm和6mm×6mm四方扁平无引脚(QFN)封装。将MOSFET和驱动器封装在一起,使得供应商能够利用其对器件和封装技术的经验来匹配MOSFET和驱动器,消除PWB的一些外部影响,如走线宽度和长度。由于MOSFET厂商能指定使用何种控制器,从而针对驱动器和封装来优化MOSFET,提供效率比分立元件更高的组件。而效率高意味着在相同电流下产生的热量更少,有助于设计师解决散热问题。随着开关频率高达1MHz的应用越来越普遍,消除板上的走线及离散信号路径引起的寄生效应,就显得愈加重要。将分立元件的信号路径(即从驱动器封装中出来,经过一个焊点,在板上走一段距离,再通过另一个焊点进入MOSFET封装件)缩减为两块硅片间单一的一组线键合有很多好处。同步降压转换器设计师之所以将这种封装技术作为解决其设计难题的方案来研究,就是因为驱动器和MOSFET之间只有一个封装电阻需要考虑。

虽然处理器设计师已经大大提升了处理器效率,但这种提升并未降低处理器的功耗。为了应对这一挑战,人们一直对MOSFET封装技术进行创新改进。随着以英特尔DrMOS规范为首的多芯片封装技术越来越普及,封装技术涉及的困难将会越来越多,厂商必须与最终客户协同配合,创造出整体解决方案。