【导读】DRAM(Dynamic Random Access Memory),即动态随机存取存储器,最为常见的系统内存。DRAM 只能将数据保持很短的时间。为了保持数据,DRAM使用电容存储,所以必须隔一段时间刷新(refresh)一次,如果存储单元没有被刷新,存储的信息就会丢失。(关机就会丢失数据)

工作原理

动态RAM的工作原理,动态RAM也是由许多基本存储元按照行和列地址引脚复用来组成的。

DRAM数据线

3管动态RAM的基本存储电路如图所示。在这个电路中,读选择线和写选择线是分开的,读数据线和写数据线也是分开的。

写操作时,写选择线为“1”,所以Q1导通,要写入的数据通过Q1送到Q2的栅极,并通过栅极电容在一定时间内保持信息。

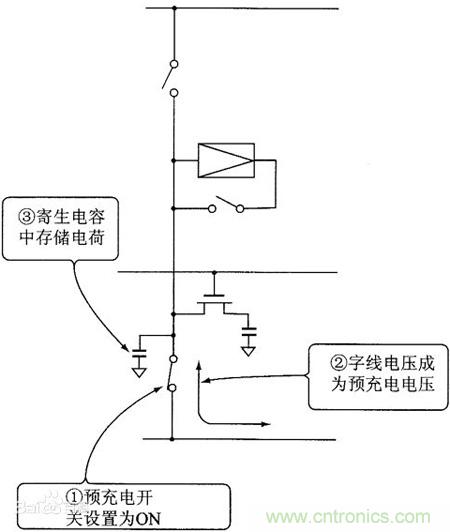

读操作时,先通过公用的预充电管Q4使读数据线上的分布电容CD充电,当读选择线为高电平有效时,Q3处于可导通的状态。若原来存有“1”,则Q2导通,读数据线的分布电容CD通过Q3、Q2放电,此时读得的信息为“0”,正好和原存信息相反;若原存信息为“0”,则Q3尽管具备导通条件,但因为Q2截止,所以,CD上的电压保持不变,因而,读得的信息为“1”。可见,对这样的存储电路,读得的信息和原来存入的信息正好相反,所以要通过读出放大器进行反相再送往数据总线。

什么是NAND?

NAND闪存是一种比硬盘驱动器更好的存储设备,在不超过4GB的低容量应用中表现得犹为明显。随着人们持续追求功耗更低、重量更轻和性能更佳的产品,NAND被证明极具吸引力。NAND闪存是一种非易失性存储技术,即断电后仍能保存数据。它的发展目标就是降低每比特存储成本、提高存储容量。

工作原理

闪存结合了EPROM的高密度和EEPROM结构的变通性的优点。

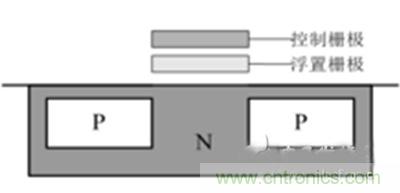

EPROM是指其中的内容可以通过特殊手段擦去,然后重新写入。其基本单元电路如下图所示。常采用浮空栅雪崩注入式MOS电路,简称为FAMOS。它与MOS电路相似,是在N型基片上生长出两个高浓度的P型区,通过欧姆接触分别引出源极S和漏极D。在源极和漏极之间有一个多晶硅栅极浮空在绝缘层中,与四周无直接电气联接。这种电路以浮空栅极是否带电来表示存1或者0,浮空栅极带电后(例如负电荷),就在其下面,源极和漏极之间感应出正的导电沟道,使MOS管导通,即表示存入0.若浮空栅极不带电,则不能形成导电沟道,MOS管不导通,即存入1。

EPROM基本单元结构

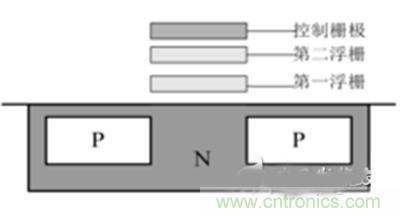

EEPROM基本存储单元电路的工作原理如图所示。与EPROM相似,它是在EPROM基本单元电路的浮空栅极的上面再生成一个浮空栅,前者称为第一级浮空栅,后者称为第二级浮空栅。可给第二级浮空栅引出一个电极,使第二级浮空栅极接某一电压VG。若VG为正电压,第一浮空栅极与漏极之间产生隧道效应,使电子注入第一浮空栅极,即编程写入。若使VG为负电压,强使第一浮空栅极的电子散失,即擦除。擦除后可重新写入。

EEPROM单元结构

闪存的基本单元电路与EEPROM类似,也是由双层浮空栅MOS管组成。但是第一层栅介质很薄,作为隧道氧化层。写入方法与EEPROM相同,在第二级浮空栅加正电压,使电子进入第一级浮空栅。读出方法与EPROM相同。擦除方法是在源极加正电压利用第一级浮空栅与漏极之间的隧道效应,将注入到浮空栅的负电荷吸引到源极。由于利用源极加正电压擦除,因此各单元的源极联在一起,这样,擦除不能按字节擦除,而是全片或者分块擦除。随着半导体技术的改进,闪存也实现了单晶体管设计,主要就是在原有的晶体管上加入浮空栅和选择栅,

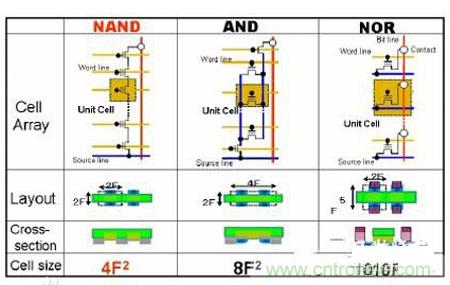

NAND闪存单元结构

NAND闪存阵列分为一系列128kB的区块(block),这些区块是NAND器件中最小的可擦除实体。擦除一个区块就是把所有的位(bit)设置为“1”(而所有字节(byte)设置为FFh)。有必要通过编程,将已擦除的位从“1”变为“0”。最小的编程实体是字节(byte)。一些NOR闪存能同时执行读写操作。虽然NAND不能同时执行读写操作,它可以采用称为“映射(shadowing)”的方法,在系统级实现这一点。这种方法在个人电脑上已经沿用多年,即将BIOS从速率较低的ROM加载到速率较高的RAM上。