【导读】本文作为电压输入至输出控制(VIOC)应用于低压差稳压器(LDO)系列文章的第二部分,在第一部分基础概念之上,深入剖析VIOC系统设计逻辑,详解新一代LDO凭借恒定输入输出电压差所实现的高电源电压抑制比(PSRR)、优化功耗及可靠故障保护等核心性能优势;同时依托LTspice®仿真、演示硬件等参考设计与评估方法,降低VIOC技术的应用门槛,还进一步探讨其在负电压拓扑中的集成路径,并梳理早期基于分立元件、传统LDO架构的实现方案,揭示VIOC在优化开关稳压器与LDO协同工作、赋能现代电源管理系统多样化方案开发中的关键价值。

VIOC详解

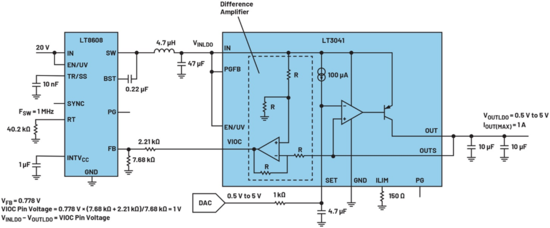

最新一代LDO中的VIOC特性是通过LDO内部增益为1的差分放大器实现的,如图1所示。由差分放大器的示意图可见,它由运算放大器和分立电阻构成。在最基本的配置中,差分放大器的输出直接连接到为LDO供电的开关稳压器的FB引脚。VIOC和FB引脚之间的连接形成一个闭环的反馈回路,在该回路中,开关稳压器输出一个比LDO输出更高的电压,高出幅度等于差分放大器的输出电压,而差分放大器输出电压连接到开关稳压器FB引脚。FB引脚是开关稳压器IC误差放大器反相输入端的外部连接点。

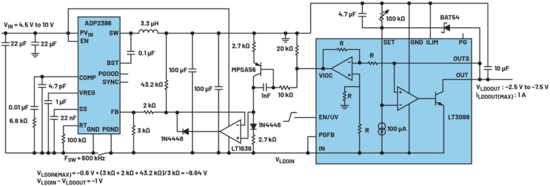

图1.最新一代LDO中的VIOC特性通过LDO内部增益为1的差分放大器实现

误差放大器是一种电子元件,通常采用运算放大器实现,其作用是放大两个输入信号(通常是基准电压和来自系统输出的反馈信号)之间的差值。此差值(即误差信号)用于调整系统以维持期望的输出。因此,误差放大器是稳压器、电源、伺服机构等反馈控制系统的关键组成部分。

实现VIOC的差分放大器还负责处理一些管理任务,例如防止LDO输入过低和关断LDO。有关VIOC行为的完整详情,请参阅LDO数据手册中的VIOC部分。

开关稳压器FB引脚电压在大约0.4 V到1.2 V之间,具体取决于开关稳压器IC。如果开关稳压器反馈引脚的电压低于所需的LDO输入输出电压差,可在开关稳压器的FB引脚和LDO的VIOC引脚之间添加一个电阻。此电阻用于将差分放大器输出端的VIOC信号连接到更高电压点,如图1所示。图1所示LT3041 LDO和类似LDO的VIOC,很难实现比开关稳压器FB引脚电压更低的LDO输入输出电压差。

为了理解差分放大器如何实现VIOC,可将差分放大器的输出视为其输入之一。如果差分放大器的输出电压为某个特定值,则其正输入端的电压必须高于其负输入端的电压,且高出幅度必须等于该差分放大器输出电压。差分放大器的负输入端连接到LDO的输出端,因此差分放大器可调节开关稳压器的输出电压,使其比LDO的输出电压高,高出的量值与差分放大器输出电压(由开关稳压器的FB引脚电压决定)相同。

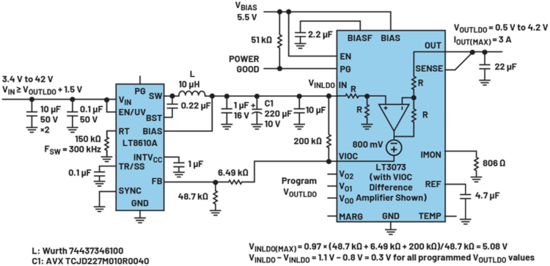

图2.LT3073 LDO具有VIOC电路设计,可使LDO的输入输出电压差低于开关稳压器反馈引脚电压,并限制LT8610A开关稳压器的输出电压

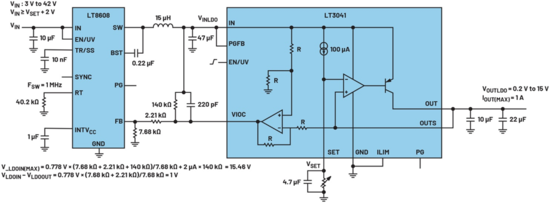

图3.如果LDO未使能,则LT3041 VIOC电路会限制LT8608开关稳压器的输出电压

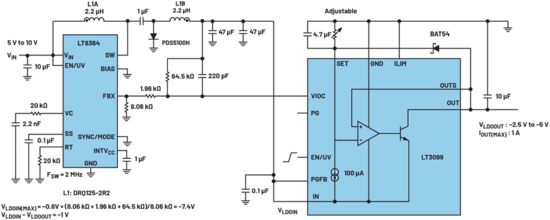

图4.采用Ćuk配置的开关稳压器,用于产生负电压(使用LT8364)

图2显示了具有VIOC电路设计的LT3073 LDO,该设计使得LDO的输入输出电压差可以低于开关稳压器的反馈引脚电压。此VIOC方法提供一个偏置电压,使LDO输入输出电压差比VIOC引脚电压低800 mV。这种类型的VIOC在输入输出电压差较低、电流额定值较高的LDO中很常见。图2电路还能限制开关稳压器的输出电压。开关稳压器的反馈电阻分压器用于防止在LDO未使能或无法闭合VIOC反馈环路的情况下,开关稳压器的输出电压变得过高。如图3所示,图1中的LT3041 VIOC电路会限制开关稳压器LT8608的输出电压。

到目前为止讨论的LDO都是使用正电压工作的正LDO,但VIOC操作也支持使用负电压工作的负LDO。负LDO的VIOC电路可采用产生负电压的开关稳压器来实现,其反馈引脚命名为FBX,而不是FB。图4显示了一个采用Ćuk配置的开关稳压器,用于产生负电压。负LDO LT3099的VIOC用于控制Ćuk输出电压。

图5所示电路反映了一种越来越常见的场景,其中的降压型稳压器通常产生正电压,但通过配置为反相降压-升压型稳压器,它可用来产生负电压。由于标准降压型稳压器没有用于配合负电压使用的FBX引脚或FB引脚,因此该VIOC电路需要一个电平转换器。在该电路中,电平转换器是电路的一部分,电路中包含LT1636运算放大器和连接到运算放大器正输入端的网络。

VIOC很容易实现,只需在已有的开关稳压器到LDO连接的基础上,增加一根导线即可。VIOC可与任何带有FB引脚的开关稳压器配合使用。请注意,Silent Switcher® 3 (SS3)稳压器IC没有FB引脚,因此VIOC通常不与这些IC一起使用。如果开关稳压器FB引脚连接到内部分压电阻,而该电阻也连接到输出端,则VIOC会有一些局限性。某些µModule®稳压器就属于这种情况。

µModule稳压器是一种高度集成的系统级封装(SiP)解决方案,它在一个紧凑的封装中集成了多个电子元器件,例如DC-DC控制器、功率晶体管、输入输出电容、补偿元件和电感。2

图5.如果开关稳压器采用的是反相降压-升压配置(使用ADP2386),则负LDO的VIOC电路需要电平转换器

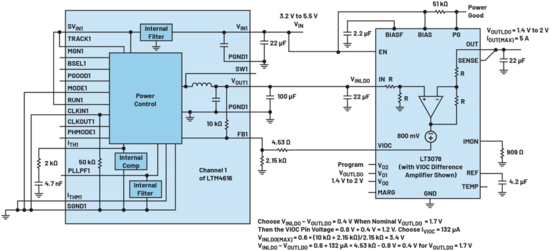

图6.此VIOC电路将LTM4616 µModule稳压器的一个通道与LT3078 LDO配合使用

图6所示VIOC电路将LTM4616 µModule稳压器的一个通道与LT3078 LDO配合使用。µModule的FB引脚与开关稳压器的输出端之间有一个内部10 kΩ电阻。VIOC引脚电流(及相应的VIOC引脚电压)与10 kΩ电阻的电流相关;当LDO和开关稳压器的输出电压提高或降低时,电阻电流会按比例变化。VIOC引脚电压对LDO输出电压的这种依赖关系,会限制图6所示电路的LDO输出电压调节范围。

评估VIOC系统工作情况的便捷方法

LTspice®可用于快速仿真和评估受限环境下的VIOC工作情况,从而无需物理硬件便能测试不同的场景和参数。因此,它是在实现电路之前验证电路行为和优化设计的有效工具。

使用硬件评估VIOC功能的最有效方法,是将开关稳压器演示电路连接到LDO演示电路,并进行极少量的改动。图7显示了两个配置用于快速测试VIOC的此类电路。对于VIOC电路的最终设计,通常需要在实际硬件上进行负载瞬态测试,以检查电路稳定性。为了提高稳定性,通常会在开关稳压器输出端增加电容。如需相关指导,请参阅数据手册中的VIOC参考设计。

图7.两个演示电路,只需极少量改动即可快速测试VIOC工作情况(使用DC3158A和DC2458A)

图8.VIOC的一个早期版本(采用LTC3415)

早期版本VIOC和非内置VIOC

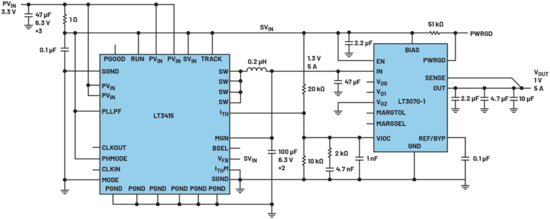

到目前为止,大部分讨论都集中在采用最新一代VIOC的LDO上。除此之外,还有一种采用分立元件实现VIOC的方法,使用早期一代带有VIOC特性的LDO。图8显示了一个采用早期版本VIOC的LDO电路。LDO的VIOC引脚连接到开关稳压器的ITH或VC引脚,LDO的VIOC电路自动将LDO的输入输出电压差控制在300 mV左右。ITH或VC引脚是开关稳压器IC误差放大器输出端的外部连接点。早期5V、5A LDO,例如LT3070-1、LT3071和LT3072,就是采用这种VIOC方法。

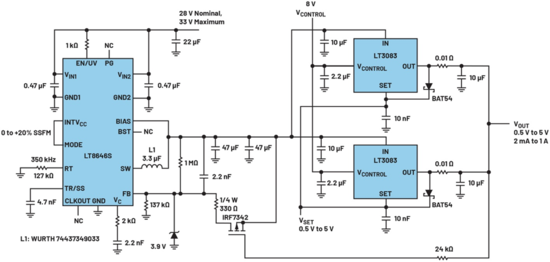

我们要讨论的最后一类VIOC是利用分立元件实现的VIOC。借助分立元件,几乎任何LDO都可以添加VIOC功能。这种方法在早期的电流源基准LDO(从LT3080开始)中特别流行,因为通过外部电压信号或数字电位器改变带电流源基准的LDO输出电压相对容易。电流源基准LDO是一种不使用基准电压源,而使用电流源驱动电阻来确定输出电压的稳压器。图9显示了一个使用分立器件实现VIOC的电路。IRF7342 PMOS的源栅电压决定LDO的输入输出电压差。有关采用此类VIOC的更多参考设计,请参阅LT308x数据手册。

图9.使用分立器件LT8646S和LT3083实现VIOC的电路

总结

电压输入至输出控制(VIOC)作为新一代LDO的核心特性,通过内部增益为1的差分放大器及闭环反馈机制,显著提升了电源管理系统的性能与灵活性。它能使LDO维持恒定输入输出电压差,实现高PSRR、优化功耗及可靠故障保护,还可适配正/负电压拓扑,兼容多种稳压器以拓展应用场景。从早期分立元件方案到如今内置化低压差设计,VIOC技术始终以简化集成、降低门槛为核心演进方向,LTspice®仿真与演示硬件则为快速验证设计、保障稳定性提供了支撑。未来,VIOC将持续优化开关稳压器与LDO的协同性能,为现代电子系统提供精准电源解决方案,助力精密设备性能升级。