【导读】当ADC的模拟输入被驱动至额定满量程输入电压时,ADC提供最佳性能。但在许多应用中,最大可用信号与额定电压不同,可能需要调整。用于满足这一要求的器件之一是可变增益放大器(VGA)。了解VGA如何影响ADC的性能,将有助于优化整个信号链的性能。

本文分析一个采用双通道16位、125/105/80 MSPS、流水线ADC AD9268和超低失真中频VGA AD8375的电路中的噪声。信号链包括一个VGA(在+6 dB增益设置下使用)、一个五阶巴特沃兹低通滤波器(–3 dB滚降频率为100 MHz)和ADC。本文将给出放大器和滤波器的噪声计算,因为这些噪声决定ADC在目标频段内的动态性能。

问题

许多采用高速ADC的实际应用都需要某种驱动器、放大器或增益模块,用以将输入信号缩放到满量程模拟输入范围1,确保获得最佳信噪比 (SNR)和无杂散动态范围(SFDR)。此外,差分放大器也可以将单端信号转换为差分信号来驱动ADC。这些器件都是有源器件,因而会增加ADC前端的噪声。此噪声在工作带宽内的积分会降低转换性能。

针对具体应用,适当ADC的选择取决于许多因素,包括:

● 模拟输入范围

● 输入频率/带宽

● 所需分辨率/SNR

● 所需SFDR

某些应用同时要求高动态范围和高分辨率。AD9268在70 MHz中频提供78.2 dBFS(dB相对于满量程)的SNR和88 dBc的SFDR,非常适合此类应用。

AD9268

● 信噪比(SNR):78.2 dBFS (70 MHz)

● 无杂散动态范围(SFDR):88 dBc (70 MHz)

● 低功耗:750 mW (125 MSPS)

● 1.8 V模拟电源供电

● 1.8 V CMOS或LVDS输出电源

● 1至8整数输入时钟分频器

● 中频采样频率达300 MHz

● 小信号输入噪声:−153.6 dBm/Hz(200 Ω输入阻抗、70 MHz、125 MSPS)

● 可选片内抖动

在系统层面,ADC前端可以使用放大器、变压器或巴伦,但使用放大器的实现方案最为常见。使用放大器的原因可以是下面的一条或几条:

● 为输入信号提供增益以提高ADC分辨率

● 缓冲或变换输入源与ADC之间的阻抗

● 将单端输入信号转换为差分输出信号

AD8375

● 24引脚,4 mm × 4 mm LFCSP封装

● 5 V单电源供电

● 关断特性

● 噪声系数:8 dB(最大增益时)

● 增益范围:-4 dB至+20 dB

● 差分输入与输出

● 带宽:630 MHz (−3 dB)

● 并行5位控制接口

● 提供稳定的SFDR与增益变化关系

● 步长:1 dB ± 0.2 dB

● 输出IP3:~50 dBm (200 MHz)

● 输出P1dB:19 dBm (200 MHz)

AD8375 VGA可以用来将单端信号转换为差分信号,同时它能在不同增益设置下保持高线性度和一致的噪声性能。这些特性使它成为在较高中频下驱动ADC的上好选择。糟糕的是,信号链中的有源器件(即放大器),可能会限制ADC的性能。

示例

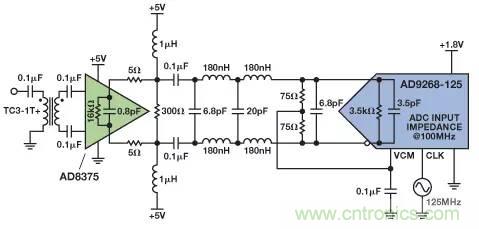

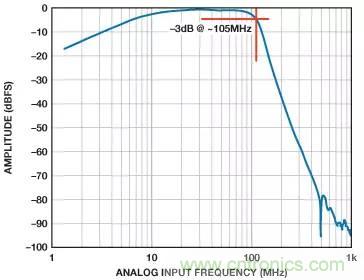

图1给出了噪声计算所用的电路拓扑结构。AD8375具有高阻抗差分输出(16 kΩ||0.8 pF)。放大器通过一个五阶低通抗混叠滤波器(AAF)与ADC接口,该AAF具有100 MHz带宽和150 Ω输入/输出阻抗。图1所示电路的频率响应如图2所示。

图1. AD8375、AAF和AD9268信号链

图2. AD8375、AAF和AD9268信号链的频率响应

性能

系统设计师不会期望驱动ADC输入端的放大器降低系统的总体动态性能,但针对某一应用选择的驱动器和ADC组合,并不意味着它能在另一应用中提供同样出色的性能。利用本文所述技术,系统工程师可以在选择放大器之前估计预期的性能。

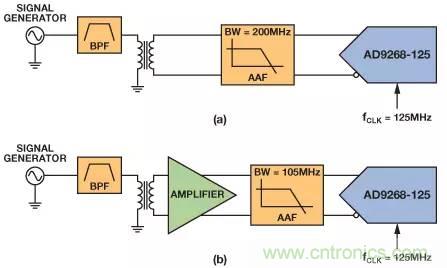

图3显示了两种不同的设置。图3(a)利用无源耦合连接转换器,是客户评估板的默认选项。无源前端网络利用变压器或巴伦,以及一个滚降频率约为200 MHz的无源低通滤波器,将单端信号转换为差分信号。图3(b)显示的可选放大器路径。这两种设置贡献的噪声比较如下。利用低中频(10 MHz)时的单音快速傅里叶变换(FFT)来计算放大器增加的噪声。

图3. 典型ADC前端:(a) 无源;(b) 有源

噪声分析通常使用两种技术,但每种技术都很麻烦。噪声谱密度(NSD)定义单位带宽的噪声功率。对于ADC,其单位为均方dBm/Hz或dBFS/Hz;对于放大器,其单位为均方根nV/√Hz。用放大器驱动ADC时,这种单位的不一致性构成系统噪声计算的障碍。

噪声系数(NF)是输入SNR与输出SNR的对数比,用dB表示。这一特性通常为RF工程师所用,在纯RF环境下很有意义,但在带ADC的信号链中使用NF计算,可能会导致令人误解的结果。

另一种更有效的技术是对噪声密度进行“反归一化”处理,将其表示为均方根噪声电压,而不是均方电压。这种方法直截了当,能够对系统噪声进行清晰的分析,下面将予以说明。

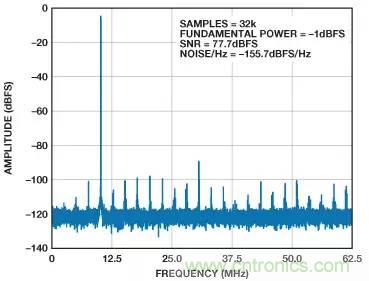

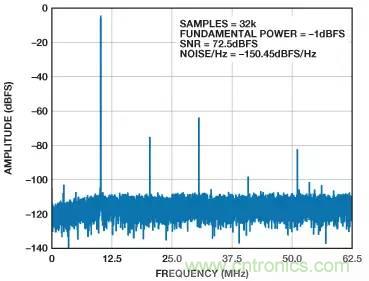

图4和图5分别显示这两个前端的低频单音FFT。注意,无源前端的SNR为77.7-dBFS,而有源前端的SNR为72.5-dBFS,比ADC的预期性能低5.2 dBFS。

图4. 图3a电路10 MHz模拟输入音的FFT

图5. 图3b电路10 MHz模拟输入音的FFT

分析

图3a与图3b所示设置的唯一不同是信号链中增加了放大器,因此可以放心地说,性能降低是由放大器的噪声引起的。下面的计算有助于了解放大器带来的噪声。

首先,按照数据手册的规定,使用转换器的满量程差分输入电压。将峰峰值电压除以2√2得到均方根电压,即0.707 V rms。

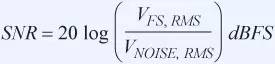

(1)

(1)基于ADC在10 MHz时的典型SNR,转换器的噪声贡献为

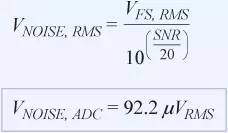

(2)

(2) (3)

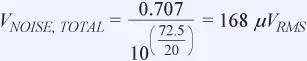

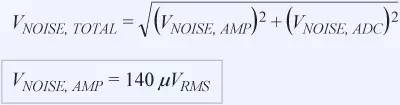

(3)VNOISE, ADC = 92.2 μV rms, 带放大器前端的系统SNR为 = 72.5 dBFS, 利用公式3计算系统噪声得到168 μV rms。

(4)

(4) (5)

(5)从公式4得到的系统噪声是ADC和VGA的合并噪声。放大器噪声可以利用公式5计算,结果为140 μV rms。这表明,放大器噪声至少比ADC噪声大50%,因此它是系统交流性能的限制因素。

注意,必须判断计算得到的VNOISE, AMP值是否与放大器的数据手册一致。在150 Ω差分输出阻抗下,额定噪声谱密度约为20 nV/√Hz。

虽然数据手册声称VGA的噪声基本上不随增益而变化,但此噪声会随负载而变化,因此噪声谱密度应根据放大器输出驱动的总阻抗进行缩放。放大器的差分输出阻抗很大(16 kΩ||0.8 pF),因此放大器看到的阻抗(见图1)可以计算如下:

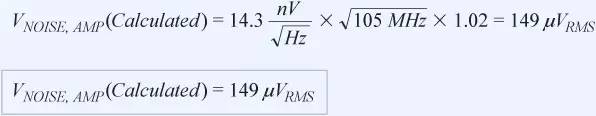

利用此数值,本应用中AD8375的减额噪声谱密度可以通过公式6计算:

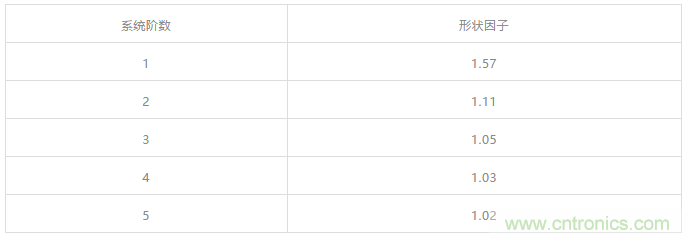

注意,利用实际滤波器计算系统噪声时,噪声带宽的形状与理想滤波器不同。频率响应的这种差别用“形状因子”这一术语来定义,反映滚降区中的噪声。形状因子取决于滤波器的阶数,是噪声带宽与–3 dB带宽的比值。滤波器的极点越多,形状因子越接近1。这一关系可从表1看出。

表1. 系统阶数与形状因子的关系

图1示例的形状因子为1.02。利用公式6计算放大器注入的噪声:

VGA注入系统的这一估计噪声值与利用公式5算得的测量值非常吻合,证明由AD8375和AD9268组成的信号链的性能主要取决于放大器。

结束语

许多情况下,系统信号链需要一个放大器(VGA或增益模块)来将满量程信号驱动到ADC。系统设计师必须了解不同放大器选择导致的ADC性能降低情况。利用所选放大器和ADC进行设计之前,设计师可以利用本文所述的方法计算放大器的噪声分布,估计预定系统实现方案的预期动态性能(通过SNR表示)。

推荐阅读: