【导读】自激振荡像得病一样,重在防御。可从以下方面入手。设计 PCB 时,尽量减小杂散电容,特别是CIN-。同一层的两个相邻节点间。比如某根信号线,和周边的覆铜 GND 之间,以及和周边的焊点之间有杂散电容C1;不同层上下之间。比如元件层的线,和焊接层的大面积 GND 之间。

自激振荡像得病一样,重在防御。可从以下方面入手。

1)设计 PCB 时,尽量减小杂散电容,特别是CIN-。下图进行说明:

同一层的两个相邻节点间。比如某根信号线,和周边的覆铜 GND 之间,以及和周边的焊点之间有杂散电容C1;

不同层上下之间。比如元件层的线,和焊接层的大面积 GND 之间,如图中 C2;

一般的,杂散电容可以达到 pF 数量级。这是不可忽视的。这些杂散电容和电路中的电阻,很容易形成低通网络,有可能引起电路稳定性下降。

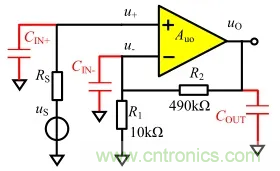

电路举例,如下图:

设计一个同相比例器,做成实际电路板后,就出现了三个杂散电容:CIN+、CIN-、COUT

CIN+ 与信号源内阻 R S (或者前级放大电路的输出电阻)组成了一个低通网络,但是这个低通网络不在反馈环内,它只会影响不同频率输入信号到达放大电路输入端的比率,进而影响放大电路的带宽,而不会引起任何稳定性问题。

CIN-与电阻 R 2 和 R 1 的并联,共同组成了一个环路内的低通网络。由于电阻 R 2 和 R 1 的并联远大于运放的输出电阻,这导致非常小的 CIN- ,就可以产生巨大的作用。因此,在电路设计中降低运放负输入端电容,就非常关键。

COUT会在反馈环路中引入一个低通网络,有可能引起环路的稳定性下降。

注意敷铜:

覆铜的本质目的是增大地线面积,进而减小地线电阻和电感。但是覆铜操作也会带来两个问题:

第一,它与同层信号线之间就形成了很长很长的近距离间隙,也就是很大的电容C1。

第二,它与其他层的信号线形成了层间电容C 2 。这些杂散电容,都会引起系统不稳定。

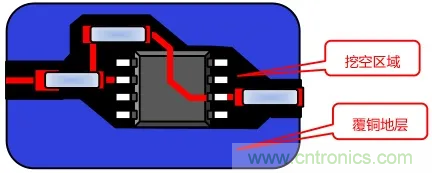

如图:

运放负输入脚及其连接线的下方,绝对不要覆铜,或者覆铜后实施挖空操作。

运放负输入脚、输出脚及其连接线的同层周边,一定要与覆铜保持足够大的间距。建议此间距要大于 20mil。

2)选择合适的增益和合适的增益电阻

对任何一个选定的运放,在它能够实现的最小增益基础上,适当提高闭环增益,可以有效提高系统稳定性。

增益电阻尽量选择小的,以降低 CIN-的作用。

因为CIN-的旁路作用使放大器的高频响应变差,其频带的上限频率约为:fH=1/(2πR2CIN-),若R2的阻值较大,上限频率严重下降,同时引入的滞后相位可能引起振荡。理论上,如果要实现 10 倍同相增益,用10kΩ 对 1kΩ,就没有用 1KΩ 对 100Ω 好。

3)尽量不要驱动大电容负载,必须驱动大电容负载的,使用裕度大的运放。一般可在运放输出端串联一个几十欧姆的小电阻起隔离作用。

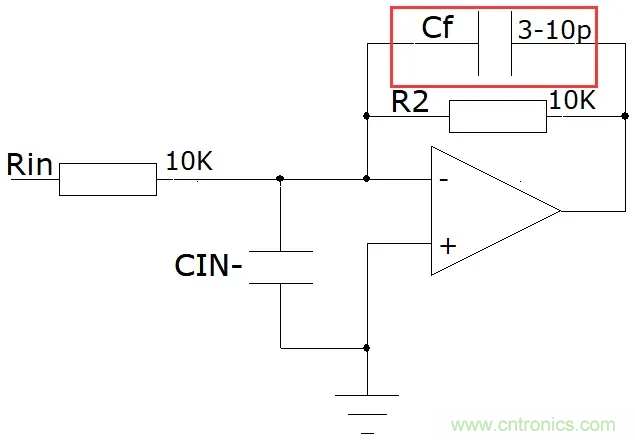

4 ) 最常见的做法是在反馈电阻中并联一个小电容Cf。

Rin、Cf网络与R2、CIN-网络构成相位补偿。Rin、Cf将引起输出电压相位超前,由于不能准确知道CIN-的值,所以相位超前量与滞后量不可能得到完全补偿,一般是采用可变电容Cf,用实验和调整Cf的方法使附加相移最小。若R2=10kΩ,Cf的典型值丝边3~10pF。对于电压跟随器而言,其Cf值可以稍大一些。

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请电话或者邮箱联系小编进行侵删。