【导读】本三部曲系列旨在全面概述锁相环(PLL)在有线和无线通信系统中的应用。第一部分将重点介绍有关PLL的基本概念,同时描述基本PLL 架构和工作原理,另外,我们还将举例说明PLL在通信系统中的用途。最后,我们将展示一种运用ADF4111频率合成器和VCO190-902T电压控制振荡器的实用PLL电路。

在第二部分中,我们将详细考察与PLL相关的关键技术规 格:相位噪声、参考杂散和输出漏电流。导致这些因素的原 因是什么,如何将其影响降至最低?它们对系统性能有何 影响?

最后一部分将详细描述构成PLL频率合成器的各个模块以及 ADI频率合成器的架构。同时还将简要总结目前市场上有售 的频率合成器和VCO,同时列出ADI的现有产品。

PLL基本原理

锁相环是一种反馈系统,其中电压控制振荡器和相位比较器 相互连接,使得振荡器频率(相位)可以准确跟踪施加的频率 或相位调制信号的频率。锁相环可用来从固定的低频信号生 成稳定的输出频率信号。首批锁相环由法国工程师de Bellescize 在20世纪30年代初实现。然而,直到20世纪60年代中期,集 成式PLL成为一种成本相对较低的元件之后,锁相环才得到 市场的广泛认可。

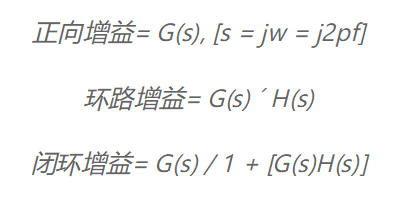

一般而言,可以把锁相环分析为一种带一个正向增益项和一 个反馈项的负反馈系统。

基于电压的负反馈系统的简单框图如图1所示。

图1. 标准负反馈控制系统模型。

在锁相环中,来自相位比较器的误差信号为输入频率或相位 与反馈信号频率或相位之差。稳态下,系统会强制使频率或 相位误差信号归零。其适用负反馈系统的一般公式。

受环路中积分的影响,在低频下,稳态增益G(s)较高且

PLL中会增大环路增益的元件包括:

1. 鉴相器(PD)和电荷泵(CP)。

2. 环路滤波器,其传递函数为Z(s)

3. 电压控制振荡器(VCO),其灵敏度为KV/s

4. 反馈分频器,1/N

图2. 基本锁相环模型。

如果将一个线性元件(如四象限乘法器)用作鉴相器并且环路 滤波器和VCO也为模拟元件,则将其称为模拟或线性PLL (LPLL)。

如果使用的是数字鉴相器(EXOR栅极或J-K触发器)并且所有 其他元件保持不变,则系统称为数字PLL (DPLL)。

如果PLL完全用数字模块构建而成,不带任何无源元件或线 性元件,则称为全数字PLL (ADPLL)。

最后,有了数字化的信息,再加上足够快的处理能力,也可 以在软件域开发PLL。PLL功能由软件执行并在DSP上运行。 这称为软件PLL (SPLL)。

根据图2,当系统使用PLL来生成高于输入的频率时,VCO会 以角频率D振荡。该频率/相位信号的一部分会通过分频器以 1/N的比率回馈到误差检测器。这种经过分频的频率会馈入误 差检测器的一个输入端。本例中,另一路输入为固定参考频 率/相位。误差检测器会比较两个输入端的信号。当这两个信 号输入的相位和频率相等时,误差为零,环路则处于“锁 定”条件下。如果我们只看误差信号,则可得到以下等式。

e(s) = FREF - FO / N

当 e(s) = 0,

FO / N = FREF

因此

FO = N FREF

在商用PLL中,鉴相器和电荷泵共同构成误差检测器模块。 当 FO ¹ N FREF时,误差检测器将向低通环路滤波器输出源/吸电 流脉冲。这会使电流脉冲稳定转换为电压,用以驱动VCO。 然后,VCO频率会根据需要以 KV DV的幅度增减,其中, KV 为VCO灵敏度(单位:MHz/V),V为VCO输入电压的变化。 这一过程会持续进行,直到e(s)变为零为止,届时环路将锁 定。可见,电荷泵和VCO充当一个积分器,用于将其输出频 率增加或减小至所需值,以(从鉴相器)将其输入恢复至零。

图3. VCO传递函数。

简单而言,PLL的总传递函数(CLG或闭环增益)可以用上面给 出的负反馈系统的CLG表达式来表示。

FO / FREF = 正向增益 / [1 + 环路增益]

正向增益, G = KD KV Z(s) / s

环路增益, G H = KD KV Z(s) / Ns

当GH远远大于1时,我们可以说,PLL系统的闭环传递函数 为N,因此,

FOUT = N ´ FREF

环路滤波器属于低通类滤波器,一般有一个极点和一个零 点。环路的瞬态响应取决于:

1. 极点/零点的幅度,

2. 电荷泵幅度,

3. VCO灵敏度,

4. 反馈因子N。

在设计环路滤波器时,必须考虑所有上述因素。此外,设计 滤波器时必须以稳定为第一要务(通常建议使相位裕量达 /4)。响应的3-dB截止频率通常称为环路带宽BW。大环路带 宽会导致超快的瞬态响应。然而,这种结果并非始终都有 利,因为,就如我们将在第二部分看到的那样,快瞬态响应 与参考杂散衰减之间存在权衡问题。

PLL在频率上调中的应用

利用锁相环,可以从低频基准电压源产生稳定的高频。要求 稳定高频调谐的任何系统都可以从PLL技术中受益。这些应 用示例包括无线基站、无线手机、寻呼机、闭路电路系统、 时钟恢复和时钟生成系统。GSM手机或基站就是PLL应用的 一个很好的例子。图4显示了GSM基站的接收部分。

图4. GSM基站接收器的信号链。

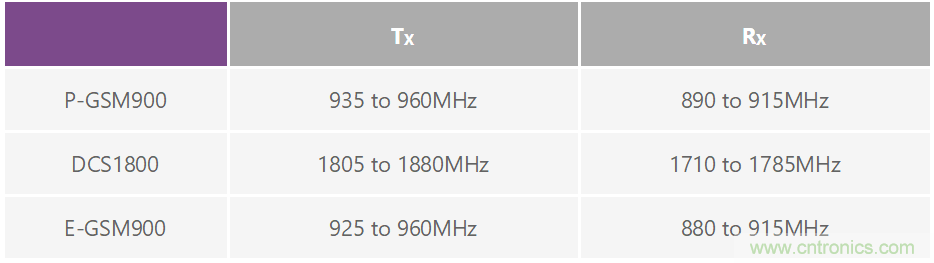

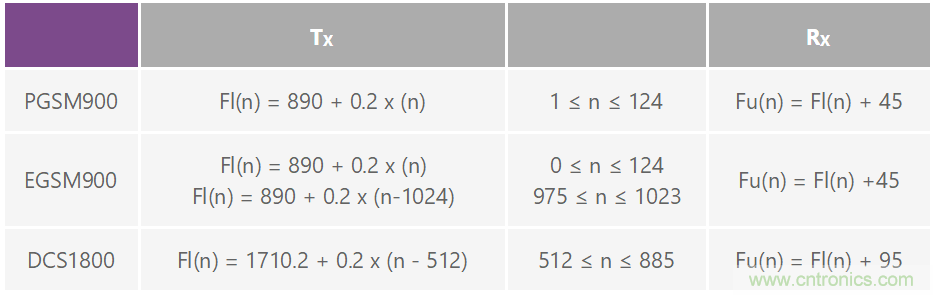

在GSM系统中,有124个宽度为200-kHz的RF频段通道(每个通 道8个用户)。占用的总带宽为24.8 MHz,必须对这些带宽扫描 以检查活动状况。手机的发射(Tx)范围为880 MHz至915 MHz, 接收(Rx)范围为925 MHz至960 MHz。相反,基站的Tx范围为 925 MHz至960 MHz,Rx范围为880 MHz至915 MHz。对于本 例,我们只考虑基站发射和接收部分。GSM900和DCS1800基 站系统的频段如表1所示。表2展示的是表1所列频段范围内的 载波频率的通道编号(RF通道)。Fl(n)为RF通道低频段(Rx)的 中心频率,Fu(n)为高频段(Tx)的对应频率。

表1. GSM900和DCS1800基站系统的频段 表2.

表2. GSM900和DCS1800基站系统的通道编号

对900-MHz RF输入滤波、放大并施加到第一级混频器。另一 个混频器输入端用调谐本振(LO)驱动。本振必须对输入频率 范围扫描,以检查任何通道上的活动状况。实际上,LO是运 用前面已经描述过的PLL技术来实现的。如果第一中频(IF) 级的中心位于240 MHz,则LO的频率范围必须为640 MHz至 675 MHz,才能覆盖RF输入频段。当选择200-kHz的参考频率 时,可以按200 kHz的步长,在整个频率范围内对VCO输出排 序。例如,如果需要650 MHz的输出频率,则N的值为3250。 该650-MHz的LO会有效地检查890-MHz RF通道(FRF - FLO = FIF 或FRF = FLO + FIF)。当N增至3251时,LO频率为650.2 MHz,检 查的RF通道为890.2 MHz。如图5所示。

图5. GSM基站接收器的测试频率。

值得注意的是,除了可调谐RF LO以外,接收器部分也采用了 固定IF(在所示例子中为240 MHz)。尽管该IF并不需要频率调 谐,但仍然采用了PLL技术。其原因在于,运用稳定的系统 参考频率来产生高频IF信号不失为一种经济的方式。多家频 率合成器制造商已经意识到这一事实,推出了双版本器件: 一个版本支持较高RF频率(>800 MHz),另一个版本支持较低IF 频率(500 MHz或以下)。

在GSM系统的发射端也存在类似的要求。然而,更常见的做 法是直接从基带上变频为发射部分的最终RF;这意味着,基 站的典型TX VCO的范围为925 MHz至960 MHz(发射部分的RF 频段)。

电路示例

图6显示了GSM手机发射部分本振的实际实现方式。我们假 设,基带直接上变频为RF。该电路采用了来自ADI的新型 ADF4111 PLL频率合成器,以及来自Vari-L公司的VCO190-902T 电压控制振荡器(http://www.vari-L.com/)。

图6. GSM手机的发射器本振。

参考输入信号施加于电路的FREFIN,其端接电阻为50 。在 GSM系统中,该参考输入频率的典型值为13 MHz。为了使通 道间距为200 kHz(GSM标准),必须运用ADF4111的片内参考分 频器,将参考输入除以65。

ADF4111是一款整数N PLL频率合成器,最高支持1.2 GHz的 RF工作频率。在该整数N型频率合成器中,可以按离散整数 步长,在96至262,000范围内对N编程。对于手机发射器,如 果所需输出范围为880 MHz至915 MHz,并且内部参考频率为 200 kHz,则所需N值的范围为4400至4575。

ADF4111的电荷泵输出(引脚2)驱动环路滤波器。基本而言, 该滤波器(图2中的Z(s))是一款一阶滞后-超前型滤波器。在计 算环路滤波器元件值时,需要考虑多个事项。在本例中,环路滤波器的设计宗旨是使系统的整体相位裕量 为45度。其他PLL系统技术规格如下:

KD = 5 mA

KV = 8.66 MHz/V

环路带宽= 12 kHz

FREF = 200 kHz

N = 4500

额外参考杂散衰减= 10 dB

所有这些技术规格都需要用来计算环路滤波器元件值,如图6 所示。

环路滤波器输出驱动VCO,然后馈入PLL频率合成器的RF输 入端,同时驱动RF输出通道。用一个带18 电阻的T型电路配 置在ADF4111的VCO输出、RF输出和RFIN引脚之间提供50 匹配。

在PLL系统中,知道系统何时锁定十分重要。在图6中,这是 通过利用ADF4111的MUXOUT信号来实现的。可设置 MUXOUT引脚来监控频率合成器中的各种内部信号。其中之 一是LD或锁定检测信号。举例来说,当选用MUXOUT以选 择锁定检测时,就可以在系统中用MUXOUT来触发个输出功 率放大器。

ADF4111用一个简单的4级串行接口来与系统控制器通信。参 考计数器、N计数器和各种其他片内功能都是通过该接口进 行编程的。

结论

在本系列的第一部分中,我们借助一些简单的框图和等式, 介绍了PLL的基本概念。我们还展示了一个典型的例中,说 明了PLL结构的用武之地,并详细描述了一种实际实现方法。

在下一部分中, 我们将进一步探讨对PLL至关重要的技术规 格,并讨论它们对系统的意义。

参考电路

1. Mini-Circuits 公司, "VCO 设计师手册", 1996.

2. L.W. Couch, "数字与模拟通信系统" Macmillan Publishing Company, New York, 1990.

3. P. Vizmuller, "RF设计指南", Artech House, 1995.

4. R.L. Best, "锁相环:设计、仿真与应用",第3版, McGraw Hill, 1997.

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读: