【导读】在上一篇的文章中我们有截取各组信号的大致走线结构,从这个走线上我们到底可以看出什么问题会导致该DDR2系统运行异常呢?下面请看我们一一为您分解。

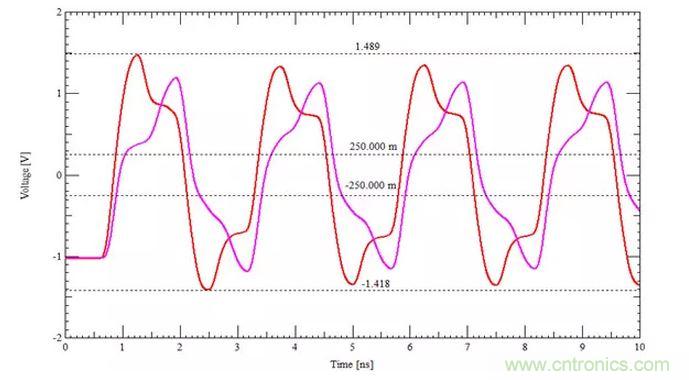

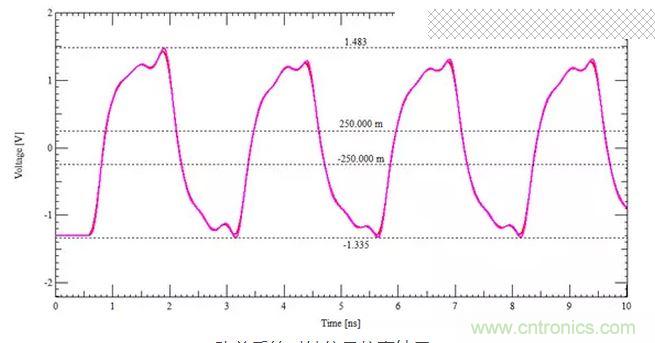

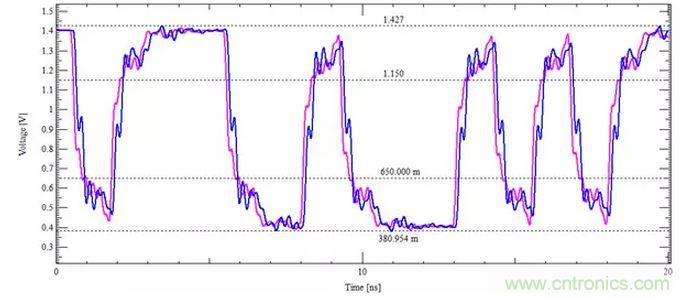

时钟信号一拖二采用T型拓扑结构无可厚非,也说明有一定的设计概念,但是对于T型拓扑的设计要点还不是很清楚。一般我们的DDR2信号的T型结构需要主干线比较长,分支比较短,最好在500mil以内,这是看到的第一个问题,该设计分支和主干线路长度差不多;第二个问题是如果要外部端接,一般这个端接会放到第一个分支处,而该设计虽然在分支处加了端接,但在另一端靠近颗粒处又加了一个多余的端接,这就造成我们T型结构的不平衡。所谓的T型又叫等臂分支结构,需要两个分支长度、结构、端接尽量一致(长度有偏差时,最好控制在20mil内),而该设计却没有做到这一点。我们仿真了原版本设计和改善后的时钟信号,波形对比如下所示。

原始版本时钟信号仿真结果

改善后的时钟信号仿真结果

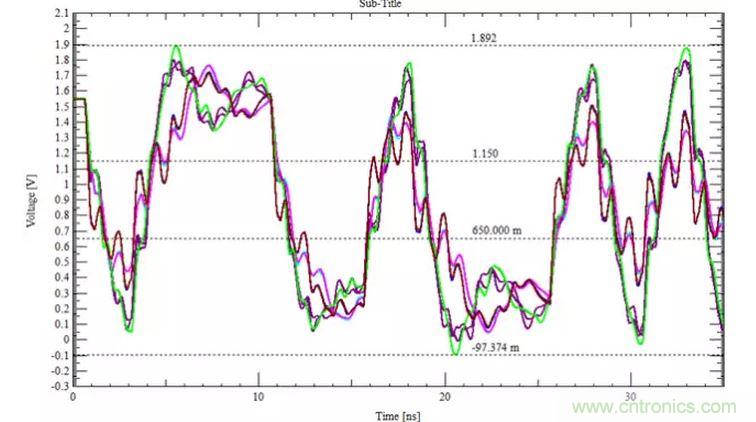

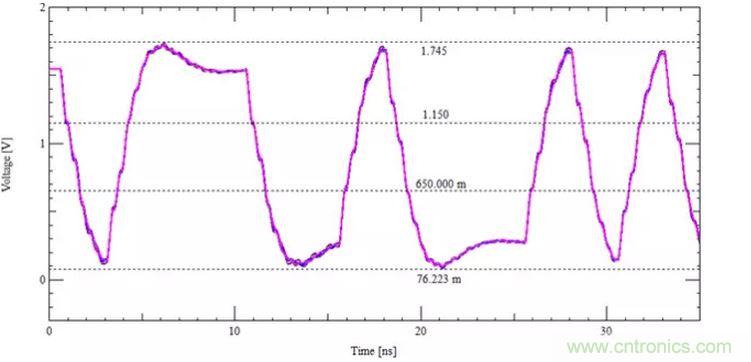

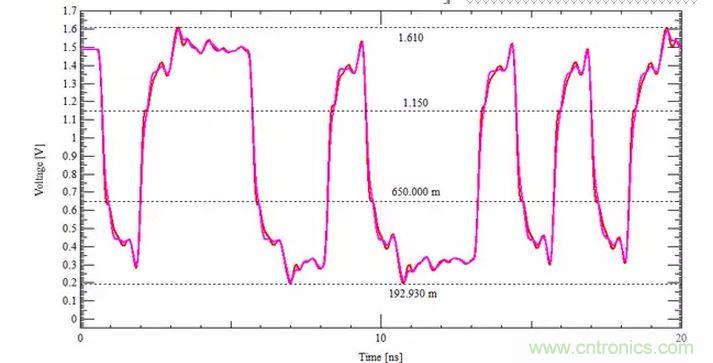

地址信号一拖八也采用T型结构,按照上面对T型结构的说明,主干要长分支尽量短且对称的原则,我们可以看到这个地址信号的走线结构就比较凌乱,可想而知信号肯定会很差。且看原始设计和改善后的仿真结果对比。

原始版本的地址信号仿真结果

[page]

改善后的地址信号仿真结果

DQS信号也大致一样,没有按照T型结构的最好原则来布线,不再赘述。最后来看数据信号,数据信号需要完全参照DQS信号走线,包括等长。好了,现在的数据信号却走成了菊花链结构,且没法和DQS去做严格的等长,另外信号之间的间距也很小,容易引起串扰问题,真的很任性!

原始版本的数据信号写操作仿真结果

改善后的数据信号写操作仿真结果

上面只是每组信号的单独分析,再看看全局的一些考虑吧。

1、总体上加了太多的串阻,占用了布线空间且多打出许多过孔。

2、地址、命令和控制信号需要和对应的时钟信号保持一定的等长(等长范围视具体芯片来定,一般在±200mil)。

3、数据组需要和对应的DQS信号等长(一般在50mil内),尽量同组信号同层布线。

4、数据组与对应的时钟信号也需要有一定的等长,为了给后续调试留出更多的裕量,一般这个等长比时序仿真出来的结果更短,常见的在±500mil内。因为参考的时钟关系,这也意味着数据组与组之间的长度偏差也在±500mil内。当然这些等长范围都是一些经验值,具体的更要看对应的芯片。

好了,以上只是对DDR2的设计做了一部分常规性的总结,那么问题来了~