【导读】本文将描述在SoC设计方法论中追求新流程的目的。该流程包括提取、评估和分析复杂SoC及其封装环境的全电磁耦合模型。分析结果强调了电磁耦合对现代复杂SOC设计性能和功能的影响。

本文将描述在SoC设计方法论中追求新流程的目的。该流程包括提取、评估和分析复杂SoC及其封装环境的全电磁耦合模型。分析结果强调了电磁耦合对现代复杂SOC设计性能和功能的影响。

背景

随着纳米尺度技术的引入,互连线的纵横展弦比提高了。因此,来自邻近攻击者的电容串扰对受害者网络会有这更大的影响,这就需要新改进的SoC设计流。为确保从攻击者处注入(静止)受害者网络的(累积)能量不会导致电路网络故障,我们就需要全新的噪声分析工具和相应的IP表征方法。在静态时序分析流中用于互连延迟计算的算法得到了扩展,它反映了噪声对延迟的影响,这是由于过渡信号在攻击器上的并发转换在输出端可能产生的波形变化造成的。

用于物理实现的EDA工具也包含了新的特性。详细的路由算法得到了扩展,包括对相邻互连的并行运行长度的限制。同时,采用了更复杂的噪声计算/避免方法来辅助布线轨道的选择。

设计人员采用的技术以进一步降低随后电容串扰噪声失效的风险。此外,对关键网的特定非默认绕线规则(NDR)进行了编码,以指导实现工具在层上的金属段之间使用大于最小的间距,或将段引导到与非开关(电源/接地)网络相邻的轨道,以有效地屏蔽节段与耦合转换。

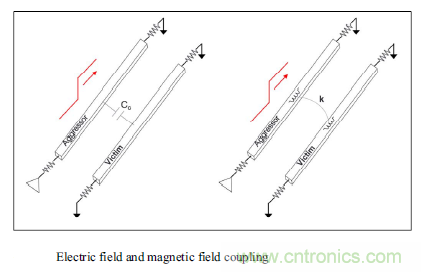

金属节段之间的电容电场线的有限范围相对容易地结合到SoC物理设计和电分析流中,由库单元输出驱动器波形和输入管脚噪声灵敏度模型(标准)支持。

随着SoC时钟频率目标的增加和纳米设计中电源电压的缩放,特定网的(自)电感的影响变得更加明显。通过将提取的RLC模型应用于P/G栅格,将开关电流源注入到栅格位置,对其进行功率/地噪声裕度分析。此外,我们利用电感元件分析时钟网的转换速率,对时钟驱动器转换的(谐波)高频内容呈现附加阻抗。

参考文献的案例描述了一种有代表性的金属节段集合的偏电感提取方法——假设部分电感用于一个节段,以减轻定义“全回路”电流返回路径的困难。但时钟信号分布可能会受到影响。

当今SoC设计的电磁建模要求

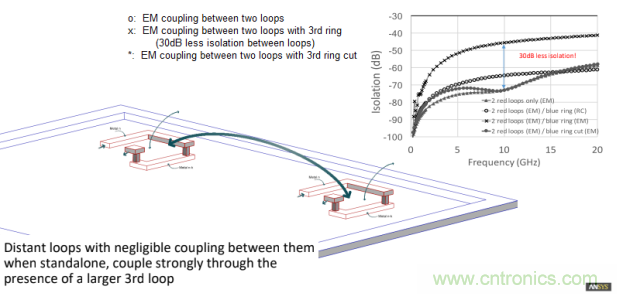

现代SoC设计的复杂性集成了一组极为多样化的高性能IP,并相应地增加了不同物理块之间电磁耦合的潜力。为了表示芯片上电流环之间的互感远距离相互作用,我们将P/G栅极和时钟网的隔离(部分)电感模型进行扩展。

上图说明了对这种物理耦合建模的重要性。设计中两个“隔离”的小环路相距1mm,当完全提取并一起分析时,它们是孤立的,耦合非常弱。设计还包括第三个更大的20毫米x 25毫米的环。当考虑第三大环的RC效应时,对两个线圈之间的隔离影响会很小。然而,在进行全电磁(EM)提取(RLCk)和分析时,从图中可以看出,由于额外的EM耦合,两个小环路之间的隔离在10GHz时降低了30dB。注意,第三环/环路在物理上并不与两个IP环路相邻——全电磁耦合不同于短距离的电场电容性串扰。

(附带说明,为了证明EM耦合来自于第三个循环,对第3个循环“cut”做了额外的分析——隔离返回到2个循环的结果,如上图所示。)

有助于电磁耦合的芯片上的周围结构包括多种可能性,例如P/G栅极(带有去耦盖)、密封环、大块硅衬底、封装上的重分布层金属等。

那么,为什么会出现SoC EM耦合问题呢?

上图说明了IP块之间的隔离主要是在非常高的频率上受到影响。考虑一下当前SoC的设计,其中许多串行收发信路被封装在芯片上——例如,这些SerDes通道可以在7GHz下传输PAM-4 56Gbps的信号。一组通道将共享一个公共VCO/PLL时钟源——多个组将被集成以提供所需的总数据带宽。(每个组也可以有多个内部的VCO,以跨越更大的发射频率范围。) 在多个SerDes通道、它们的P/G网络、密封环和封装结构之间的磁力耦合可能会导致时钟抖动显著增加,从而导致不可接受的误码率。

如前所述,当今高级封装的拓扑是EM耦合模型的关键部分。它需要包含2.5D封装(含插接器)中的再分配和功率传递金属。在3D封装中,多个堆叠、变薄的模具的独特特性也需要EM耦合模型。

EM耦合工具

这就需要SoC团队将EM耦合分析添加到签名方法中(sign-off),这就需要新的工具/流程来帮助设计人员完成EM模型提取和仿真的艰巨任务。

最近,我有机会与ANSYS的工程副总裁Yorgos Koutsoyannopoulos讨论了最新的电磁耦合工具/流的进展。

Yorgos表示:“我们将电磁耦合分析任务分为两部分。最终目标是为设计师提供设计中所有相关结构的RLCk模型,并对电路级模型进行时间、频率、噪声的模拟。”然而,整个芯片封装的数据量将是不可管理的,并且SoC上的大部分IP信号将不会时候到关注。我们开发了一个评估流程,以帮助设计师确定具体的网络,在那里可进行详细的电磁耦合模型仿真。”

“完整的芯片封装模型最初生成的评价是?”

Yorgos解释:“使用ANSYS Pharos工具评估流程的重点是评估SoC金属、vias、电介质和衬底模型,而不是考虑电路级的细节。设计者感兴趣的(顶级)互连层,并构造拓扑模型是在物理断点处自动添加端口。在这个连接处,如果没有底层电路,就没有提取出的RLCk模型的标注——芯片就不需要LVS低速扫描。为了检测更大的循环,分析将跨越SoC IP物理层次结构。我们的目标是找到相互作用的结构,以保证进一步的、详细的模拟。”

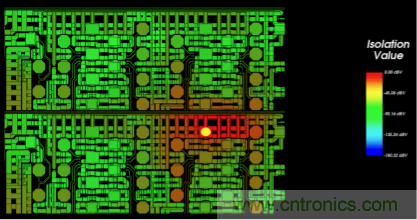

“会给设计师什么反馈?”

Yorgos:“ANSYS Pharos为相关的视觉反馈提供了切除布局数据库上的两种通用热图,并为后续的模拟选择了网格。被切除的模型按照设计师提供的频率范围(和增量)再进行评估。”

“即使是切除SoC模型,这仍然是一个庞大的物理数据量-什么样的IT资源需要这种的早期评估?”

例如,对于选择顶部5个金属层的100mm**2晶圆,在64核1TB内存占用服务器上,每个频率点的热图大约需要1-3个小时。”,Yorgos回答。(还不错,我想。)

Yorgos:“Pharos使用与其他流程相同的互连技术,包括将金属薄片电阻率作为线宽的函数和工艺角的定义。对于带有封装模型的晶圆,我们能够将封装堆栈定义和重分发层包含到一个统一的提取模型中。我们也有一个先进的方法,将模具基板建模成一个非常精确的钢筋混凝土网格网络。”

就像扩展设计方法以支持电容性串扰的影响一样,高性能SoC IP(可能使用高级封装)将越来越需要采用广泛的电磁耦合分析方法。

参考文献:

[1] Ruehli, A.E., “Inductance Calculations in a Complex IC Environment”, IBM Journal of Research and Development, p. 470-481, September 1972.

[2] White, et al., “FASTHENRY: A Multipole-Acclerated 3D Inductance Extraction Algorithm”, IEEE Transactions on Microwave Theory and Techniques, Vol. 42, No. 9, p. 1750-1758, September, 1994.

[3] Restle, P., and Deutsch, A., “Designing the best clock distribution network”, VLSI Circuits Symposium, p. 2-5, 1998.

[4] Raman, A., et al., “Electromagnetic Crosstalk Failures and Symptoms in SoC Designs”, 2017 18th International Workshop on Microprocessor and SoC Test and Verification, p. 39-43.

[5] Papadopoulos, P., et al., “Challenges and Trends in SoC Electromagnetic Crosstalk”, 2017 2nd International Verification and Security Workshop (IVSW), p. 63-69.

技术名词解释:

NDR

全称是 Non default routing rule, 非默认绕线规则。一般用于设置 clock 时钟走线的规则。时钟的翻转频率较高,clock path 上受到的串扰以及 EM 影响也较大。因此,通常会采取双倍宽度的绕线宽度。默认的绕线规则都是单位宽度,就是指 technology lef 中定义的金属层宽度。如果我们需要采取双倍宽度的绕线规则,那我们就需要先定义 NDR,然后工具才能使用这个规则。对于 NDR,我们可以定义在 LEF 中,也可以直接用命令定义。

电磁耦合

电磁耦合又称互感耦合,它是由于两个电路之间存在互感,使一个电路的电流变化通过互感影响到另一个电路。两个或两个以上的电路元件或电网络的输入与输出之间存在紧密配合与相互影响,并通过相互作用从一侧向另一侧传输能量的现象;概括的说耦合就是指两个实体相互依赖于对方的一个量度。

(来源:Semiwiki,Tom Dillinger)