【导读】现在社会快速发展,我们都很浮躁。大家都基本贴上了急功近利的标签。市场总是变化的,当看到一个方向有利可图的时候,大家都会像潮水一样涌向那边。于是乎,市场总是逼着研发快速出产品。

现在社会快速发展,我们都很浮躁。大家都基本贴上了急功近利的标签。市场总是变化的,当看到一个方向有利可图的时候,大家都会像潮水一样涌向那边。于是乎,市场总是逼着研发快速出产品。

所以现在的产品开发周期短,成本要求低,客户体验好,质量把控严。这些标准对技术工程师的要求也越来越高。

殊不知,做产品是一门工程学,一个好的产品也是“十年磨一剑”的。历数那些留在人们心中的品牌产品无不是经过多少年慢慢磨练出来的。这不故事就是由此来的。

给客户做的一个产品还有一个月就要量产了,突然接到通知,产品里的一个模块需要切换供应商。只有硬着头皮,顶着一个月的压力,解决问题。模块与我们产品的接口是不能变的,只需做一个同样尺寸的模块,就可以满足要求。所以自己评估下硬件工作量也不是很大,软件自己评估了下也可行。

参考芯片的datasheet,做好原理图,发给原厂FAE , check后做了修改,就开始lay板了。开始还进展顺利,PCB出来,贴片完成,把新模块贴到机器上,交给软件调试了。软件与我们不在一起,机器寄给他们调试,一个多星期后,发过来个版本说可以测试。离导入量产只剩下半个月了,只能抓紧时间测试,期待尽早发现问题,不然,等到量产时候如果有问题自己只有哭了。

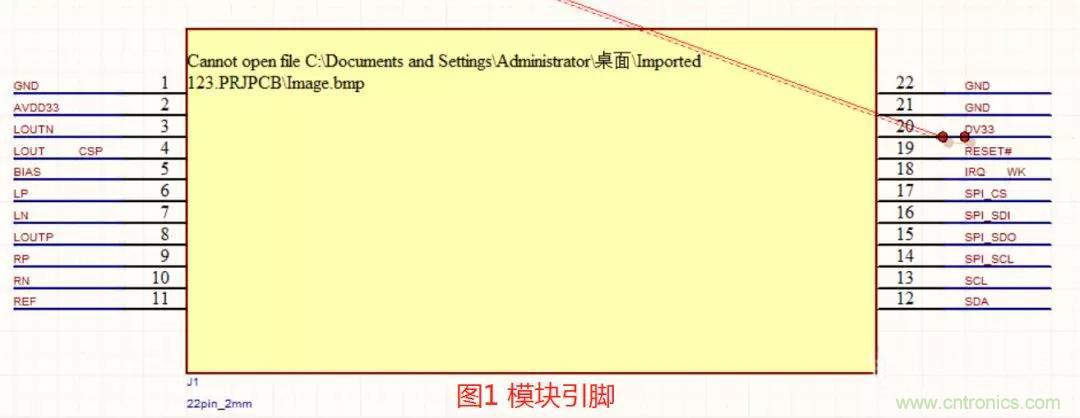

测试了几次,问题就来了。发现偶尔机器上电,这个模块的功能点击应用没有反应。查软件,发现在没有反应的时候,软件I2C读取芯片里面的寄存器,却读不到数据。硬件开始查模块AVDD3.3V和DV33供电(开始只测试了模块的22个PIN脚信号),未发现异常。测试了复位信号RESET#,复位时间也满足要求。继续测试,每次I2C上也有数据发给模块,但是异常时候却收不到模块应答。苦苦思索,没有答案。

继续测试,发现模块不是每次起不来。如果断电久一点,再上电,模块就起不来,但是如果断电后马上上电,模块就会OK。貌似发现了攻城的突破口,一丝激动。应该与上电时序有关系。马上查datasheet,查找芯片的上电时序。一瓢冷水突然泼过来,芯片有好几个引脚供电,但是没有上电时序的详解,打电话问FAE,了解到这个芯片也是第一次开始量产,目前规格书确实没有上电时序的介绍。天啊,这芯片尽然在我们这开始量产,而且还在这么短的时间,顿时没有了信心。懈怠了会,只有继续,谁让咱们是做技术的。做技术和当兵一样,技术工程师如果怕问题和当兵的怕打仗没啥区别,量产前发现的问题逃避不解决,就如战场上的逃兵。

只有继续用示波器对比测试芯片各个电源引脚断电后马上上电与等会再上电看看电源引脚上有无异常。开始怀疑某个电源必须先上电才行,因为断电后放久一点再上电异常,断电后马上上电OK。过一段时间后应该是某电源上有电容放电完了,而马上上电上一次电容上的电荷还没有放电完毕,立刻再上电相当于提前上电了。顺着这个思路继续与FAE用示波器测试,果然不出所料。

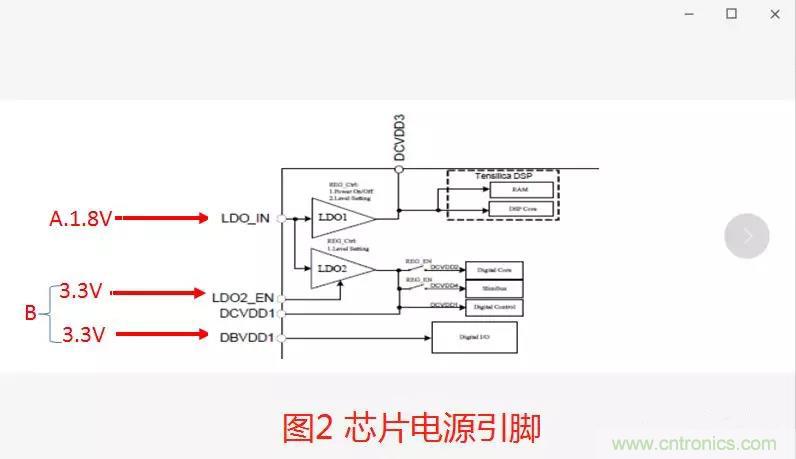

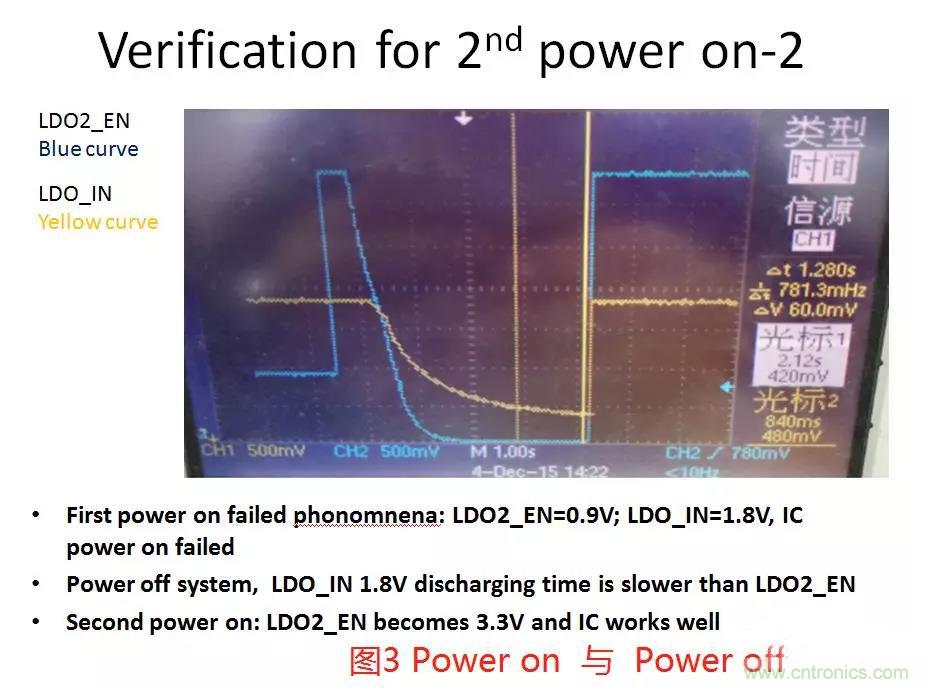

此芯片需要3.3V和1.8V 2种电源。LDO2_EN,DCVDD1和DBVDD1我们用模块引脚的3.3V直接供电,而LDO_IN我们用3.3V在模块上通过LDO转换过来的。LDO2_EN通过100K上拉电阻连接到3.3V。继续测试发现在LDO2_EN有猫腻。芯片异常的时候,LDO2_EN有0.9V电压,而芯片正常时候,LDO2_EN有3.3V电压,估计0.9V电压偏低无法使能LDO2,所以芯片不能正常工作。示波器继续抓取波形:

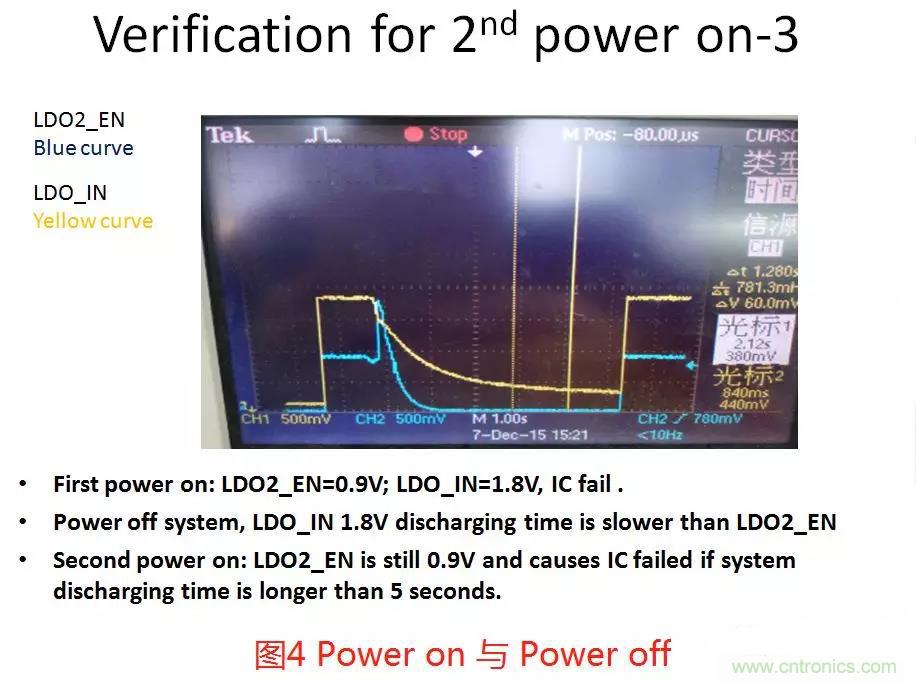

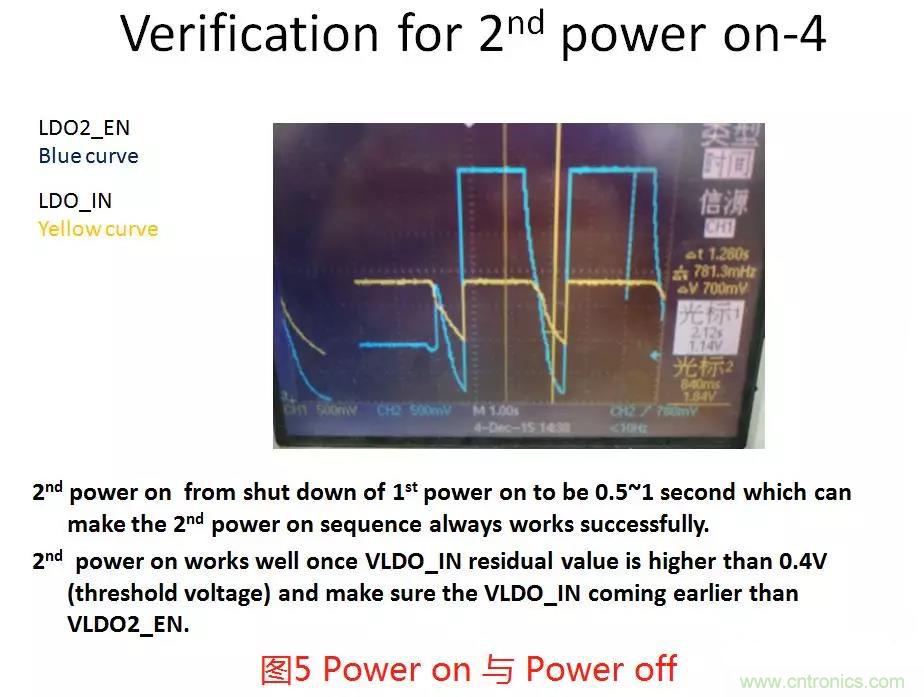

继续抓取Power on 与 Power off波形如图4:

原因慢慢露出水面,可能LDO_IN要比LDO2_EN先上电,因为每次断电后立即上电,此时LDO_IN discharging time 小于5 秒,LDO_IN电压还有近400mv,此时芯片上电每次都正常。为了验证,继续做通断电实验,示波器再抓取波形:

为了验证,从模块外另外找到一个比模块3.3V先上电的1.8V电源,飞线到LDO_IN,做通断电实验,发现每次OK。不管什么时候上电芯片都正常工作。奋战到这一步,大家都欣喜不已。抓紧再验证了2台机器,通断电实验,也是每次OK。到此刻,大家才确定算找到了原因,下一步就是找到最优化的解决方案,最小化的改动PCB板,最低成本的解决问题,最短时间的导入。

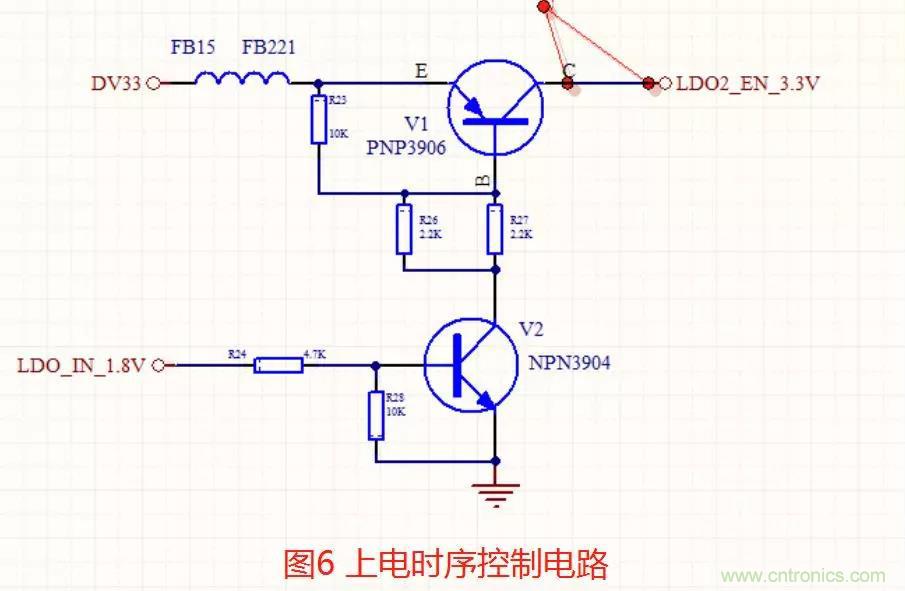

讨论后,决定在板上增加2个三极管控制,用LDO_IN 的1.8V使能3.3V后得到LDO2_EN的3.3V,这样保证LDO_IN_1.8有电压后,才会有LDO2_EN的3.3V。其它地方没有做改动。改PCB板后,立即回来焊接了10PCS,装了10台机器,做通断电实验没有发现此问题了。终于在量产前解决了这个硬件的BUG。

晚上的加班测试,分析,直到最后有了初步定论后大家都身心疲惫,看看时间已经是凌晨3点多。晚餐为了节省时间,大家点的外卖麦当劳。回到家,洗漱后,看看窗外,黎明的曙光已经照射进来。不管怎么问题总算解决了,可以安心的睡觉了,也许下一个灭火的战斗还在等待这我,但是我们还是要及时总结,避免这样的问题再次发生。

总结一下,在我们设计的时候,每一个细节还是要确认好,上电时序是最基本的要求,一定要按照datasheet来设计。顺便说一下,后来FAE联系了芯片原厂,芯片也确实有这样要求,只是在datasheet上没有体现。虽然没有体现,但是作为工程师做设计,这些基本的考虑是我们必须要主动确认好的。一个小小的疏漏,导致你可能奋战一个通宵。如果在量产后再发现,后果会更严重。

以此为教训,分享出来给大家,希望大家以后在做设计的时候都注意。同时我们还必须注意夯实自己的基础,即使时间再紧张,基础不能丢,很多时候出问题都是因为基础不扎实引起的。

(来源:面包板博客,作者:面包板博主:smile_miao)

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。