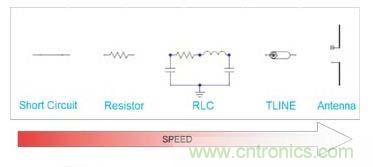

随着电子设备工作速度的不断提高,连接设备、电路板、集成电路和器件的互连系统设计越来越成为制约整个系统设计成功的关键,以高速高密度PCB设计来说,其信号完整性(SI)问题、电源完整性(PI)问题以及电磁兼容(EMC/EMI)问题已经成为设计工程当中必须解决的核心问题。随着技术的发展,越来越多的设计人员认同“高速设计就是高频设计”这一全新理念,图1很好地诠释了这一特点。

图1:“短路”特性随信号速率的变化

目前,越来越多的射频/高频设计工程师参与并指导高速互联设计,且近一半的电路设计人员发现要进行高性能SI/PI设计,就必须采用3D全波模型来处理关键互联问题。

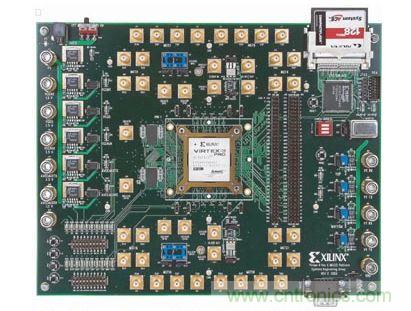

图2:Xilinx Virtex Pro X FPGA的测试评估板

实际上,要在SI/PI/EMI方面实现高性能PCB设计仿真,仿真工具必须具备以下几点关键要求:

第一,必须采用3D全波电磁模型,尤其对关键高速走线、过孔、网络等;第二,能够仿真模拟PCB上的复杂供电网络;第三,仿真器(包括场仿真器和路仿真器)必须具备高精度、高速度、大容量的特点;第四,同时提供时域和频域仿真结果;第五,还必须能与现有的PCB设计流程相兼容。

Ansoft公司的系列电磁场仿真工具再配合专门的SI设计仿真平台DesignerSI,不仅满足上述五点要求,而且由于Ansoft场工具均采用独有的自适应网格剖分技术,因此将电磁场仿真的难度大大降低,长久以来其仿真速度、精度、容量均得到验证,是工程实用化的工具。场工具帮助互连系统的设计者精确地提取并建立互连系统的3D全波模型,随后在仿真平台Ansoft DesignerSI中进行系统验证,提取串扰、眼图、误码率等时域、频域信息,用于信号完整性/电源完整性及EMC/EMI设计与仿真。

千兆比特高速信道设计

图2是Xilinx公司基于Virtex-II Pro X FPGA的测试评估板,其工作信号速率高达10Gbps以上,Xilinx采用Ansoft系列软件进行虚拟仿真,完成了对该PCB上收/发高速差分组线的设计优化,实现高速通信。在设计初始阶段,根据实际问题将整个高速串行信道分割为相对独立的子结构或子系统,如在本例中可分为封装、PCB走线和SMA接头,对各子系统分别进行设计优化,并通过场分析抽取、建立三维全波模型,然后在DesignerSI平台上通过动态链接、协同仿真功能,将各模块链接形成一个完整的信道进行整体性能验证。这样做不仅能通过Ansoft参数化设计功能实现各关键结构的最优化设计,而且能够最大限度地提高仿真效率,比如若想通过对PCB过孔、走线等部分结构的优化调整来提高整体传输性能,那么采用这种分解的子系统形式就能帮助设计人员迅速获得所需数据,避免重复低效劳动。

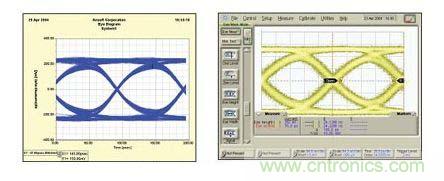

图3:DesignerSI仿真结果与测试结果

利用Q2D进行PCB走线的阻抗控制分析,确定差分线的几何结构和物理参数;利用三维场仿真工具HFSS提取封装、过孔、SMA连接器、非规则走线等的全波电磁模型;在DesignerSI中链接整个信道模型分别在时频域中进行系统验证。

在DesignerSI平台上导入芯片IBIS/Spice模型,通过与Ansoft场工具的动态链接完成整个信道的总体验证,得到眼图并与实测结果对比(见图3)。

推荐阅读:

PCB板设计绘制心得

http://www.cntronics.com/gptech-art/80020592

PCB布线在电磁兼容性设计中的影响

http://www.cntronics.com/emc-art/80020280

PCB工程师必看

http://www.cntronics.com/cp-art/80019785

[page]

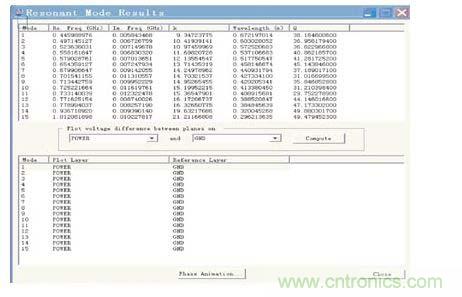

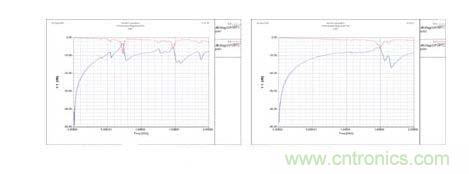

数模混合电路板的PI和SI问题

一块六层PCB板,其工作频带在1G以下,电源平面上分有2.5v、3.3v和5v三个电源分割,但具有完整的地平面。首先在SIwave中作谐振场分析以便了解电源/地平面在工作频带内的整体特性,发现在工作频带内(1G以下)会发生多个谐振现象,有14个谐振频点(见图4),同时在SIwave中可以观察PCB在各谐振频点上不同的电压(图5)。由于工作频带内的谐振不仅会带来如电源/地噪声、SSN等严重的电源完整性问题,而且对SI同样会产生严重影响。本例主要考虑通过在相关位置(如谐振场峰值/谷值位置处)加去耦电容来抑制谐振,从而间接改善SI性能。在SIwave中直接模拟该过程,根据前面得到的谐振分析结果直接仿真去耦电容的影响,为抑制这14个谐振点共加了26个去耦电容,仿真显示加去耦电容后最低谐振频点变为1.0133G,在工作带宽以外。为了了解对SI的影响,选取了一个跨电源分割的信号网络做S参数扫频分析,比较加去耦电容前后的S参数变化曲线(图6a/b),发现加去耦电容 之后,1G以下信号传输特性明显得到了改善,尤其在700M左右插入损耗和回波损耗有8dB~9dB的改善。

图4:SIwave分析得到的PCB谐振点分布

图5:谐振频率为0.4971G的电压波动情况

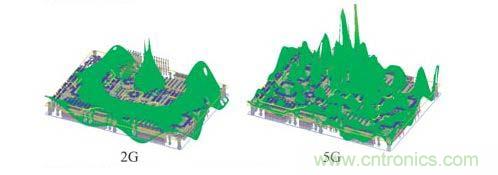

PCB EMI问题仿真

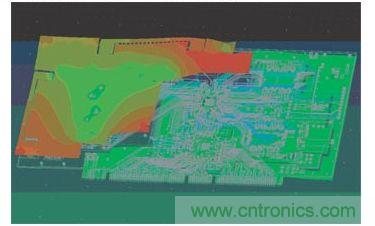

一块八层PCB,其中黄色走线为PCB上的时钟信号线,每根时钟线都与一激励源相连,为了了解该PCB的电磁辐射特性,首先在SIwave中设置扫频分析可以清楚观察到PCB板在各频点上的电压波动情况,如图7所示。

图6:加去耦电容前a和后b的信号网络IOA8的插入损耗和回波损耗曲线

图7:PCB在不同的频率上的电压波动图

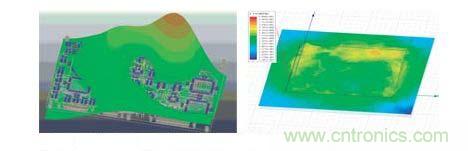

图8:1G下PCB的电压波动图和空间场分布

随后,在SIwave中计算PCB在空间的EMI辐射情况。以1G为例,图8为PCB元件正面观察到的电压波动情况,通过SIwave和Ansoft HFSS之间的动态链接,能够计算PCB板在三维空间任意位置的电磁场辐射数据,从而实现虚拟EMI测试。图8还给出了距离PCB约500mil处的电场分布云图,对比空间电场分布云图与PCB上电压波动云图可以发现:PCB上电压波峰/波谷对应的近区辐射场数值大,这也与实际情况吻合。同时根据需要可在 SIwave中直接画出各个频点上PCB板在远区的辐射场分布。

高速PCB板级设计无论SI还是PI,都是十分具有挑战性的,而由此产生的EMI问题则更为复杂。采用对虚拟原型进行仿真的方法替代反复试验的设计方法来优化电路板的设计,可以有效缩短设计周期并且节约设计成本。

推荐阅读:

PCB板设计绘制心得

http://www.cntronics.com/gptech-art/80020592

PCB布线在电磁兼容性设计中的影响

http://www.cntronics.com/emc-art/80020280

PCB工程师必看

http://www.cntronics.com/cp-art/80019785