- 可将300mm晶圆打薄至7μm

- 内存模块、CMOS元件

东京大学研究生院工学系研究专业附属综合研究机构与日本迪思科(Disco)、大日本印刷、富士通研究所以及WOW研究中心等共同开发出了可将300mm晶圆(硅底板)打薄至7μm的技术。如果采用该技术层叠100层16GB的内存芯片,芯片之间以硅通孔(TSV)连接,便能以大拇指大小的封装尺寸实现1.6TB(太拉)的内存模块。

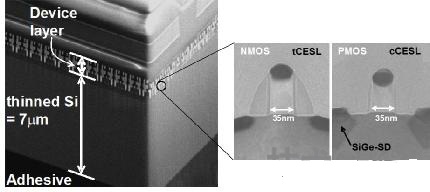

东大等在半导体制造技术相关国际会议“IEDM 2009”上发表了此次的研究开发成果。在IEDM 2009上发表的内容为,在硅晶圆上形成基于CMOS逻辑元件用45nm工艺的CMOS元件时,即使将这种晶圆打薄至7μm,也不会对n型MOSFET和p型MOSFET的应变硅、铜布线以及低介电率(low-k)层间绝缘膜产生不良影响。在不降低晶体管特性的情况下,成功实现了晶圆的薄型化。东大等表示,这是全球首次尝试将300mm晶圆打薄至7μm并进行特性评测。

此次的成果是通过东大综合研究机构特任教授大场隆之主导推进的产学项目“WOW Alliance”取得的。约20家企业及团体参与了WOW项目。该项目的目的是,预先对制作CMOS元件的晶圆进行打薄处理,接着层叠打薄后的晶圆,然后利用TSV完成布线,以此提高三维层叠LSI的量产效率。与层叠由晶圆切割而成的半导体芯片,或在晶圆上层叠芯片的三维技术相比,此次在层叠晶圆之后进行切割的技术在成本上具有更高的竞争力。此前最多只能将晶圆打薄至20μm左右,将晶圆打薄至7μm之后,不仅容易形成TSV,而且向TSV内填入金属也变得更加轻松,因而有助于进一步降低制造成本。

仅厚7μm的300mm晶圆的截面照片。采用45nm的CMOS逻辑元件工艺形成了MOSFET