【导读】FPGA的应用越来越广泛,调查报告显示,2013年全球FPGA市场将增长至35亿美元。从刚开始的简单的胶合逻辑芯片,到如今使用FPGA作为协处理器,这项技术到底有什么优势?本文将进行详细讨论。

可编程逻辑器件(PLD) 是嵌入式工业设计的关键元器件。在工业设计中,PLD 已经从提供简单的胶合逻辑发展到使用FPGA 作为协处理器。该技术在通信、电机控制、I/O 模块以及图像处理等应用中支持I/O 扩展,替代基本的微控制器(MCU) 或者数字信号处理器(DSP)。

随着系统复杂度的提高,FPGA 还能够集成整个芯片系统(SoC),与分立的MCU、DSP、ASSP,以及ASIC 解决方案相比,大幅度降低了成本。不论是用作协处理器还是SoC,FPGA 在工业应用中都具有以下优点:

1. 设计集成——使用FPGA 作为协处理器或者SoC,在一个器件平台上集成IP 和软件堆栈,从而降低成本。

2. 可重新编程能力——在一个公共开发平台的一片FPGA 中,使工业设计能够适应协议、IP 以及新硬件功能的发展变化。

3. 性能调整——通过FPGA 中的嵌入式处理器、定制指令和IP 模块,增强性能,满足系统要求。

4. 过时保护——较长的FPGA 产品生命周期,通过FPGA 新系列的器件移植,延长工业产品的生命周期,保护硬件不会过时。

5. 熟悉的工具——使用熟悉的、功能强大的集成工具,简化设计和软件开发、IP 集成以及调试。

以下将详细讨论这些优点。

设计集成

现代工业系统设计人员面临很多挑战,包括,系统复杂度、标准的变化、性能需求,以及系统总成本等,如图1 所示。

图1:关键工业设计挑战

作为一名工业系统设计人员,您可以确定是否使用FPGA 作为协处理器( 也称为I/O 辅助或者I/O hub 器件),还是完整的SoC 解决方案。您可以在相同的电路板上组合使用标准主处理器和FPGA,由外部主处理器完成系统处理功能。然而,功能固定的处理器在工业应用中通常缺少关键的接口、功能或者性能。您可以将部分处理任务移到FPGA中,从而减轻处理器的工作。或者,您在一个基于FPGA 的SoC 平台上集成所有处理器功能,降低设计复杂度,减少系统总成本。

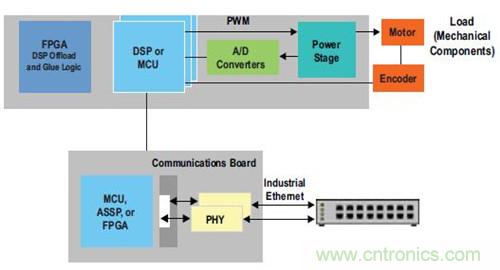

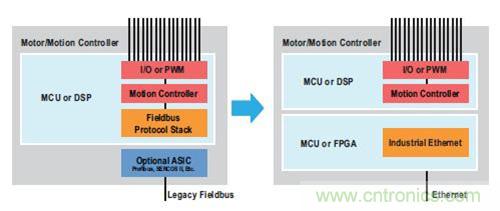

很多MCU 或者DSP 解决方案如果要同时运行电机控制任务和通信功能,其带宽将无法满足需求。结果,您可能需要增加其他的ASSP、MCU 或者FPGA 器件,如果目前的电路板无法承载这些器件,那么只能将其作为昂贵的置入卡来使用。相似的,不同的现场总线以及发展的工业以太网协议标准也需要针对每一协议采用专用ASSP、MCU 或者FPGA 器件。由于某些标准需要协议专用硬件(MAC) 和协议专用软件堆栈,因此,这些工作是必须的。FPGA可以在协处理器中集成系统功能,根据需要随时修改设计。

图2 显示了一个运动和电机控制平台,它发挥了Altera FPGA 的优势,作为DSP 卸载引擎和工业网络的协处理器。电机控制器通过控制速度和电流( 转换为扭矩设置),设置电机的能效和精度。相似的,运动控制则主要完成位置和时序精度控制功能。在很多情况下,电子硬件都是相似的,主要的差别在于控制软件或者算法,以及I/O 接口。图2 中的例子显示了一个典型的控制器,它依靠一个主MCU 或者DSP 器件( 主处理器)来运行算法,驱动电机或者运动控制器的电源级。当主处理器达到其性能极限时,设计人员可以提高器件时钟速率,以提升处理器性能。但是,对性能增益是有限制的,这种方法可能会带来其他问题,例如,需要更新到速度更快的存储器,其他硬件的性能,以及优化软件需要更多的时间等。

[page]

在这种情况下,将某些主处理器功能卸载到FPGA 协处理器中有助于简化系统,使用FPGA 进行通信,帮助随着工业以太网协议等标准的发展进行灵活的修改。然后对FPGA 重新编程,使用相同的硬件平台来满足需求。

图2:FPGA 作为运动/ 电机控制协处理器

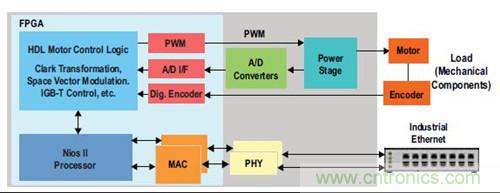

在一个SoC FPGA 器件平台上集成设计元器件,进一步简化了设计复杂度,降低了系统总成本。图3 显示了一个简单的工业电机控制系统,FPGA 现在起到了SoC 的功能,集成DSP 模块、存储器、视频图形控制器、电机编码器以及其他元器件。设计师可以简单的加入PHY 和其他模拟以及电源器件,从而完成设计。

图3:FPGA 完成SoC 运动/ 电机控制功能

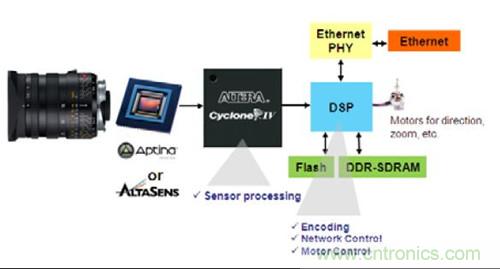

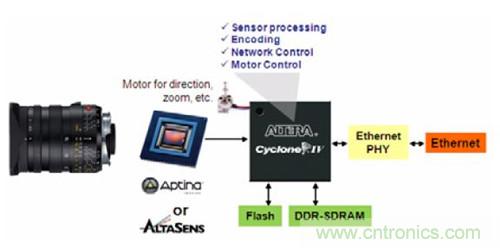

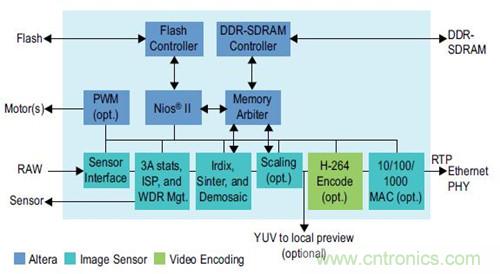

此外,电机控制应用通常还需要采用反馈机制来计算当前速率和位置。对于FPGA,很多经过优化的数字编码器接口IP 内核只能用作IP,支持在接口上使用FPGA。在FPGA上集成IP 减小了电路板尺寸,减少了元器件数量,简化了装配,降低了存储要求。这种集成方法减少了电路板上的元器件数量,从而提高了系统可靠性。Altera FPGA 支持很多其他系统功能,例如,嵌入式处理器、DSP 模块、LCD 显示屏和视频处理器等。图4 显示了另一应用实例,其FPGA 用作视频监控应用中的协处理器。视频监控市场越来越多的采用了宽动态范围(WDR) 摄像机传感器,能够分辨从背景到逆光条件下的目标物体。只有FPGA 具有WDR 图像传感器流水线(ISP) 协处理所需的带宽,将视频流送入DSP 器件进行视频编码,例如,H.264 等。DSP 器件缺少处理WDR ISP 所需的带宽和接口,不具备运行其他监控功能的性能,例如,视频分析等。

图4:FPGA 作为协处理器——WDR IP 监控摄像机

图5 显示了FPGA 作为视频监控应用中的SoC。用作SoC 时,FPGA 支持在一片FPGA 中集成所有的组件——ISP、视频分析、编码和联网功能。这一方法不需要采用后端DSP 器件,支持实现更紧凑的集成设计。

图5:FPGA 作为SoC——WDR IP 监控摄像机

图6 显示了在Cyclone IV 器件上实现的SoC 系统实例的结构图。

图6:SoC 结构图——WDR IP 监控摄像机

可重新编程能力

利用FPGA 的可重新编程能力,很容易适应标准的发展,支持设计重用。即使在工业应用中只采用一个MCU、DSP、ASSP 或者ASIC 解决方案,很多应用还是需要分立器件来处理工业通信等功能,例如,可选的现场总线专用ASIC 或者FPGA,如图7 所示。当网络规范或者功能需求出现变化时,通常会集中精力来开发多块PCB以支持不同的协议和功能,每一平台都需要额外的软件导入导出时间。这大大提高了解决方案的总成本。

图7: 现场总线过渡到工业以太网

或者可以使用FPGA 作为通信协处理器。在一个硬件平台上设计一个通信子系统,随时修改网络协议,支持多种产品。通过在一片FPGA 中更灵活的集成主MCU或者DSP 控制功能、多个处理器和其他IP 以及接口,开发小外形器件,节省空间,降低成本。

由于能够针对多种产品采用一个平台,减少了要开发的硬件数量,简化了软件的导入导出,因此将获得几个月甚至更长的产品及时面市优势。

[page]

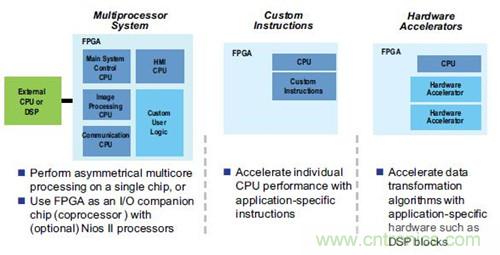

调整性能

任何工业控制系统的关键所在是主机/ 主MCU、DSP、ASIC 或者ASSP 器件的处理功能。当性能成为设计难题时,FPGA 提供以下方法来调整处理性能,如图8 所示。

■使用高性能外部处理器以及FPGA 内置的多个嵌入式处理器之一。可将所有处理功能集成到FPGA 中作为SoC。

■加入定制指令以及您的处理器代码,从而加速专用处理器指令;浮点就是一个很好的例子。

■通过DSP 模块等专用硬件加速数据转换算法。

图8:FPGA 调整性能方法

1、多核处理

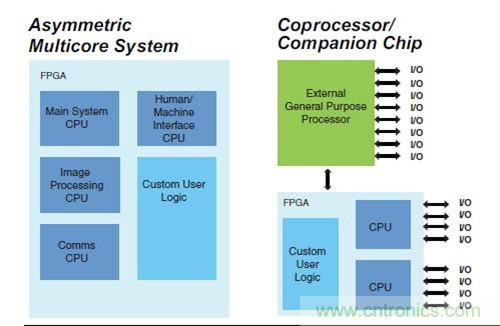

对于灵活的多处理器设计,您可以从多种实现方式中进行选择。嵌入式工业设计人员通常对非对称协处理感兴趣,把FPGA 作为I/O 辅助芯片或者SoC。非对称多处理器意味着多功能产品可以采用专用处理器来实现每一主要功能。这尤其适合满足当今迫切的应用需求,例如,智能电话等。开发人员以前在PCB 上采用多个处理器来开发这类系统。现在,您可以在一片FPGA 中每个分区的专用处理模块上来完成这一工作,如图9 所示。

图9:FPGA 作为SoC 非对称多核,以及作为协处理器

这类应用的一个例子就是高性能伺服驱动应用,它需要高性能主处理器( 或者多处理器) 来完成每一主要功能。专用处理器执行应用代码,通信处理器提供现场总线或者以太网链路,图形或者图像处理器提供显示功能,包括数字电机编码器、PWM 功能和电源控制等其他定制逻辑和接口。您还可以将所有这些功能集成到FPGA 中,作为协处理器或者完整的SoC。

[page]

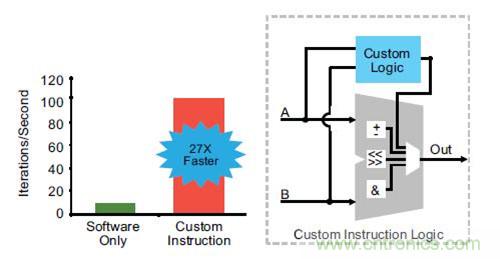

2、定制指令

设计者可以通过增加定制指令以及相应的处理器代码来调整处理器性能。这一方法加速了专用处理器指令,如图10 所示。

图10:增强定制指令的性能

设计者可以在嵌入式处理器指令集中加入定制指令,以加速对时间要求较高的软件算法。图10 中的例子显示了怎样在Altera Nios II 处理器的算术逻辑单元(ALU) 中加入定制指令逻辑。使用定制指令将复杂的标准指令序列简化为在硬件中实现的嵌入指令。

这一功能可以在各种应用中使用。例如,可以优化DSP 的软件内循环、数据包头处理以及需要大量计算的应用。Quartus II 软件提供配置GUI,支持Nios II 处理器的256 条定制指令。图10 中的例子使用了64-Kbyte CRC 缓冲。在Nios II 处理器中,与只采用软件操作相比,定制指令能够将CPU 的性能提高27 倍。

Nios II 处理器单精度、浮点定制指令是加速处理器操作的另一个例子。这些指令大幅度提高了除法、乘法、减法和加法函数的FPGA 性能。其他处理器体系结构采用相似的原理进行操作。对定制指令的实际性能加速效果会随处理器和定制指令的不同而不同。

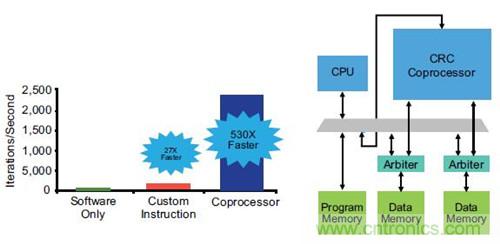

3、硬件加速

除了定制指令,还可以使用硬件加速器,例如DSP 模块、视频模块以及其他IP,从而消除数据瓶颈。图11 显示了与仅采用定制指令的同一Nios II 处理器系统相比,采用同时或者并行数据协处理器功能将系统性能提高了530 倍。在并行数据协处理器期间,处理器的中央处理单元(CPU) 启动并停止协处理器,协处理器获取数据,存储结果,CPU 同时运行应用代码。这适用于模块数据操作,例如,电机控制或者运动控制应用中常见的DSP 功能。

图11: 硬件加速器消除了处理器瓶颈

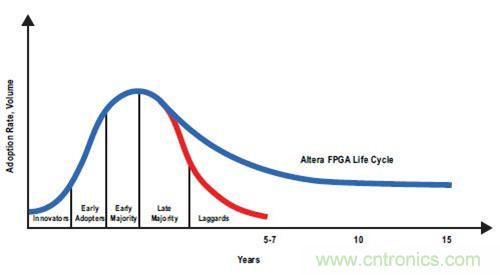

过时保护

生命周期较长的FPGA 降低了产品过时的风险。Altera FPGA 的产品生命周期非常符合工业设备的长生命周期要求,能够稳定的供应器件,如图12 所示。

图12:Altera FPGA 符合较长的工业产品生命周期要求

大部分MCU、DSP 或者ASSP 器件的产品生命周期比FPGA 短得多,这是因为和Altera相比,其供应商通常会更快的停止供应成熟器件。这类器件设计用于针对大批量用户在短期内实现特定应用。而且,虽然目前产品中的ASIC 器件可以工作15 年以上,但是很多已经接近寿命终了,迫使设计人员考虑FPGA 等其他长寿命器件。虽然新ASIC设计正在开发中,但是设计人员还不能迅速更新这些产品以跟上标准的发展,或者满足新功能的要求。

相反,FPGA 涵盖了多种应用和市场,与大批量产品的特殊应用无关。因此,Altera 在很长时间内生产的FPGA 是您的高性价比选择。用户可以更好的管理稳定的供应链,它会含有很多其他半导体元器件。在设计中使用FPGA 平台时,能够随时更新并修改设计。用户可以重复使用IP,在很短的时间内将设计导入到新系列FPGA 中,这要比设计新MCU、DSP、ASSP 或者ASIC 快得多。随着时间的推移,可以提高多条产品线的商业价值,降低产品过时的成本。

熟悉的工具

Altera 为嵌入式工业设计人员提供功能强大而又使用方便的开发工具,例如,Quartus II 设计软件、MegaCore IP 库、SOPC Builder 系统集成工具以及基于Eclipse 的Nios II 嵌入式设计套装,完善了FPGA 硬件设计,让您的设计流程更加流畅。

1、Quartus II 设计软件

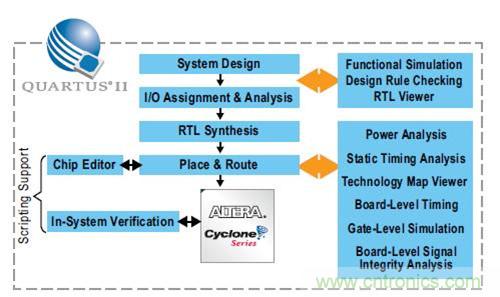

基于GUI 的Quartus II 软件有免费的网络版和拥有完全许可的版本,其设计流程包括系统设计和时序收敛方法、在系统验证以及第三方EDA 工具支持,满足了效能和性能需求,如图13 所示。

图13:Quartus II 设计流程

Quartus II 软件支持各种设计输入方法、脚本、渐进式编译、系统级集成、IP 参数赋值、I/O 引脚分析以及综合选项,从而加速了您的设计流程。在验证和电路板级,Quartus II 软件提供TimeQuest 时序分析器、功耗分析器工具、平面布局芯片规划器、SignalTap II 逻辑分析器、RTL 查看器,以及第三方验证支持。

[page]

按照下面的三个简单步骤,很容易采用Quartus II 软件开始设计:

1. 运行新工程向导,迅速设定工程名称、位置、顶层实体、设计文件、目标器件,以及工程使用的可选第三方EDA 工具。

2. 完成设计,运行时序分析和综合,构建网表。

3. 编译设计,生成器件编程文件。

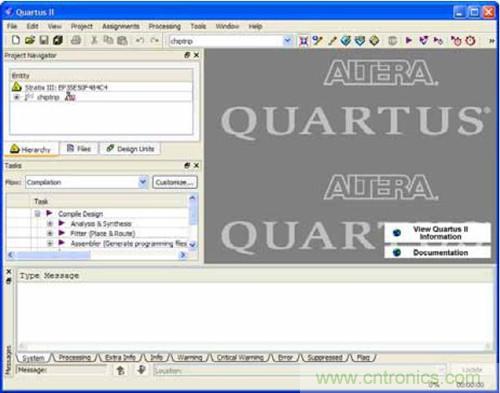

图14 显示了Quartus II 主应用窗口。

图14:Quartus II 主应用窗口

MegaCore IP 库Altera 及其第三方IP 合作伙伴提供针对Altera 器件进行了优化的多种商用可配置IP内核。这些IP 包括Altera 的Nios II 嵌入式处理器、DSP 模块、视频IP 套装等组件,以及很多标准和流行的接口,例如,存储器控制器、CAN、USB 和以太网等。随Quartus II 设计软件一起提供并安装许可和不需要许可的IP。可以直接从Altera 网站申请合作伙伴IP。IP 是模块化的,可以重复使用,通过SOPC Builder 很容易使用并编程到FPGA 中。SOPC Builder 还支持您自己IP 和接口的开发和使用。

此外,Altera 及其合作伙伴开发并提供的参考设计能够有效解决常见系统设计问题。用户可以直接从Altera 网站下载这些参考设计,也可以使用自动申请表,或者直接联系合作伙伴IP 供应商。

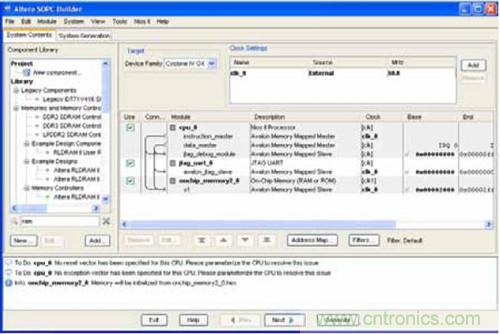

2、SOPC Builder

SOPC Builder 是功能强大的系统集成工具,它含在Quartus II 软件中,与使用传统的手动集成方法相比,能够以更快的速度生成完整的SoC 设计。SOPC Builder 很容易建立IP,在设计中自动生成并集成IP 组件。您可以通过用户友好的GUI 而不是代码HDL来管理这一过程,如图15 所示。

图15:SOPC Builder 系统集成工具

使用SOPC Builder 中的配置向导,为每一IP 组件选择合适的配置选项。完成配置后,IP 被加入到系统中,如图15 所示。以后您可以在SOPC Builder GUI 中简单的修改选项,从而改变组件基本地址、中断级以及系统互联。这样,您能够灵活方便的迅速修改、优化并设计您的FPGA 系统。

[page]

3、标准Eclipse 软件工具

一般而言,需要进行一定控制处理的任何系统都需要采用嵌入式处理器,特别是处理器必须含在SoC 设计中的情况。对于已经熟悉这些软件工具的设计人员,Altera 提供基于Eclipse 的Nios II 嵌入式设计套装,Nios II 嵌入式处理器,支持标准操作系统(OS) 以及来自多家流行供应商的实时操作系统(RTOS)。

采用这些熟悉的基于GUI 的开发工具,软件团队在设计流程中能够很好的合作。硬件和软件团队可以在标准操作系统上采用电路板支持包(BSP),利用他们的应用软件专业知识导入导出应用软件,在一个FPGA 平台上运行这些软件,而不是在多个MCU 或者DSP 器件上。可以把以前的MCU 或者DSP 编程软件经验应用到可编程嵌入式处理器上,例如,Nios II 嵌入式处理器( 使用基于Eclipsed 的工具)、ARM Cortex M1和Freescale ColdFire V1 内核,这些都可以与Altera FPGA 一起使用。开发工具流程和操作系统( 例如,Linux) 与开发分立处理器代码所使用的非常相似。基于FPGA的处理器支持Linux 和eCOS 等流行的开放源代码操作系统,具有活跃的开发人员社区这一优势,帮助不断开发新的应用程序和功能。在产品生命周期中进行开发和提供支持时,这些改进和功能有可能节省大量的投入。

而且,可以在处理器体系结构上移植C 程序。例如,面向Eclipse 的Nios II 软件开发工具(SBT) 含有一组基于流行的Eclipse 工作台的插件,以及Eclipse C/C++ 开发工具包(CDT) 插件。面向Eclipse 的Nios II SBT 为所有Nios II 处理器系统提供相同的开发平台。这些Eclipse 工具提高了大型应用软件和团队软件设计的效能。用户可以在Eclipse 中完成所有Nios II 软件开发任务,包括建立、编辑、构建、运行、调试和修改程序。

结论

FPGA 能够灵活的适应工业设计多变的各种需求,降低解决方案总成本。采用一片FPGA就可以将设计的各个部分集成到一个器件中,在本地或者远程,随时对基于FPGA 的设计重新编程。这一方法使设计能够随着标准的变化而进行修改,同时减少了支持每一协议标准或者每一额外功能所需要的电路板设计。

FPGA 是并行信号处理的理想选择,也适用于需要通过硬件加速来提高性能的系统。FPGA 中的并行硬件处理意味着不需要增加更多的控制器和功能来提高性能。设计师可以在设计中把FPGA 嵌入式处理器和IP 模块用作协处理器或者SoC,从而增强性能。软件团队可以在标准操作系统(OS) 上采用电路板支持包(BSP),利用他们的应用软件专业知识导入导出应用软件,在一个FPGA 平台上运行这些软件,而不是在多个MCU 或者DSP 器件上。可以在处理器体系结构上移植C 程序。

一个FPGA 平台能够支持多条产品线,提供具有商业价值的途径,以高性价比方式向市场迅速推出实施方案。利用Cyclone IV 器件等FPGA 的集成和灵活性优势,与其他技术相比,您能够更迅速的将产品推向市场,从而占据更大的市场份额,延长工业设计的生命周期。

相关阅读:

Altera推出10代FPGA和SoC,最高节省70%功耗

http://www.cntronics.com/gptech-art/80021003

Mouser备货Altera低功耗FPGA

http://ep.cntronics.com/voice/274

台积16FinFET工艺助力Xilinx打造最高性能FPGA器件

http://www.cntronics.com/power-art/80020971