【导读】想知道有几哪种芯片测试方法吗?混合测试法又有哪些优点?请看本文Mentor Graphics 近日发布一份题为《汽车如何推动新的可测性设计(DFT)技术》的研究报告。

《汽车如何推动新的可测性设计(DFT)技术》的中文版研究报告全文可在 Mentor Graphics 的官方网站阅读和下载: http://mentorg.com.cn/aboutus/view.php?id=256 。

背景介绍

随着人们对安全关键应用设备,尤其是汽车 IC(集成电路),提出了新的需求,DFT(可测性设计)技术又再次受到重视。越来越多的处理器被运用于汽车的刹车系统、发动机控制、平视显示器、导航系统和图像传感器等等。这些芯片必须满足非常高的质量和可靠性标准,所以芯片制造商也必须进行高水平的生产测试和系统内部测试。不仅如此,他们还必须在尽可能提升测试水平的同时,确保测试时间和成本不会增加。

全文要点与大纲如下:

●几种芯片测试方法

如今有两种测试方法被众多安全关键设备开发商迅速采纳 -- 单元识别 (Cell-Aware) 自动测试向量生成 (ATPG) 法和 ATPG/逻辑内建自测试 (LBIST) 综合运用法。单元识别测试法可实现每百万缺陷数 (DPM) 为零的目标。综合测试法则通过将ATPG和LBIST 逻辑电路测试法相结合来提高测试质量和效率。

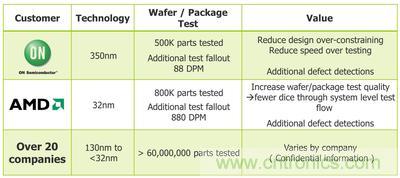

事实证明,单元识别 ATPG 测试法是唯一可以发现传统方法检测不出的缺陷的方法。它可以发现一套完整的针对固定故障、节点跳变和时延缺陷的测试方法发现不了的缺陷,因为这种方法首先就对标准单元进行物理布局时可能出现的实际缺陷进行模拟。在新技术的改进下,单元识别测试法中的测试向量大小得以缩小,但整个测试向量仍大于传统的测试方法产生的测试向量,因此要进行嵌入式压缩。许多公司因为采用单元识别测试法而收效显著。部分成效的概述请见图1。

图1:截至2013年12月来自使用单元识别测试法的公司的硅结果。安森美半导体 (On Semiconductor) 结果在2013年 ETS 上进行了发布;AMD 结果在2012年 ITS 上进行了发布。

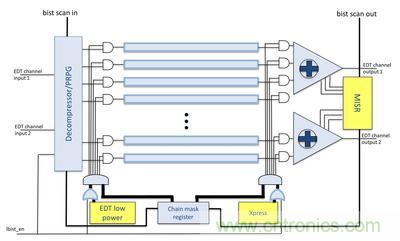

越来越多的客户在设计相同的电路时同时采用嵌入式压缩和 LBIST 测试法。由于这两种技术能够以类似的方式运用扫描链,因此可以将两者整合成可共享的统一逻辑,从而帮助客户更有效地运用这种方法。综合测试逻辑架构请见图2。

图2:混合压缩逻辑架构和逻辑内建自测试共享大部分解压单元/LFSR 和压缩单元/MSIR 逻辑。

嵌入式压缩解压单元在设计上也可整合进线性反馈移位寄存器 (LFSR),为逻辑内建自测试带来伪随机模式。逻辑内建自测试和嵌入式压缩逻辑都可通过相移位器为扫描链提供数据,这样逻辑得以完全共享。扫描链结果通过嵌入式压缩挤压到一起。该逻辑主要与逻辑内建自测试混合使用,减少进入一个签名计算器的扫描链结果数量。与单独进行嵌入式压缩和逻辑内建自测试相比,该共享逻辑可让控制器尺寸缩小20%至30%。

●混合测试法的优点

混合使用嵌入式压缩和逻辑内建自测试的一大好处便是双方互补。例如,嵌入式压缩可实现非常高品质的生产测试。这意味着您需要较少的逻辑内建自测试点就可以提高随机抵抗性逻辑的可测性,这可缩小逻辑内建自测试点的面积。相反地,X-bounding 以及任何为逻辑内建自测试增加的测试点都可提高电路的可测性,并改善嵌入式压缩覆盖和模式计数结果。

汽车电子是半导体行业增长最迅速的领域之一,这些安全关键型设备标准正推动新DFT技术的出现。嵌入式压缩的发明是重要的测试进步。

报告作者简介

Ron Press 是明导硅测试解决方案产品的技术营销经理。他在测试和 DFT(可测性设计)行业有着25年的经验,曾多次出席全球各地的 DFT 和测试研讨会。他发表了数十篇与测试相关的论文,是国际测试会议 (ITC) 指导委员会的成员、IEEE 计算机学会 (IEEE Computer Society) 的 Golden Core 成员以及 IEEE 的高级会员。Press 拥有多项减少引脚数测试和无毛刺的自由时钟切换的专利,并正在申请3D DFT 专利。