【导读】求助啊!请教下有经验的各位,这个数据总线上的波形到底应该是什么样的,我这个板子上第二条数据总线上挂着4个芯片,分别是一个SRAM,双口ram,一块FPGA和一块DSP,到底是什么问题导致数据总线出问题。

先简单介绍一下电路板,上面有两条数据总线,分别用两个DSP控制,两个DSP通过双口RAM通信。一条总线上挂着FPGA,一条挂着一个CPLD。

说说问题,就是发现用DSP给FPGA写数,然后发到测试点看波形,发现本来写0的数有的时候会读成1。

开始以为是FPGA程序使用inout的口没有释放总线,就把FPGA的数据线配置成了输入,相当于只能写不能读,仍然存在写错数的情况,而且没有什么规律。

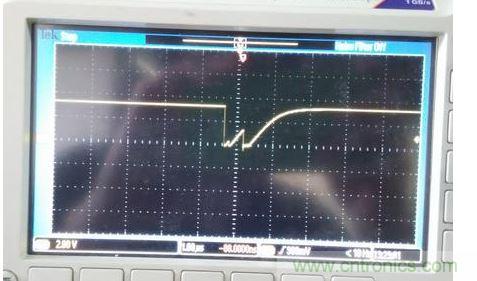

于是测量数据总线。有下面的图。这里的程序是写一次数再读一次数。感觉这个明显不对劲。

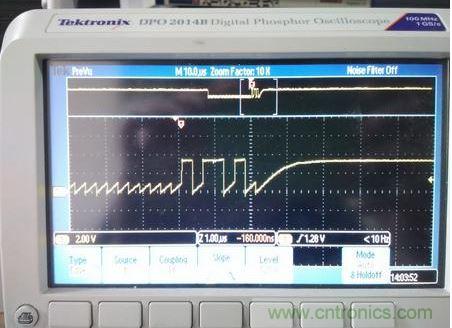

后来又把FPGA没有加载程序,单从双口RAM里读数据。有下面的波形。

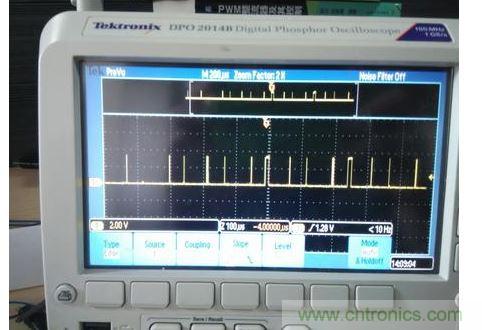

看起来好像跟FPGA没有什么关系。后来我又测量了另外一条总线的波形如下图

这个看起来就比较正常。后来我怀疑是不是哪个芯片自带上拉电阻,又把FPGA的输出口配置上了下拉电阻有下面的波形。

感觉像是DSP的IO口出了问题,因为这个板子上FPGA刚换上新的。

我记得只有一次不当使用,就是之前程序有句话写错了,只要不读写FPGA,FPGA就会把所有数据线拉低。不知道这样会不会由于FPGA的驱动能力过强,将DSP的IO口烧坏。

所以请教下有经验的各位,这个数据总线上的波形到底应该是什么样的,我这个板子上第二条数据总线上挂着4个芯片,分别是一个SRAM,双口ram,一块FPGA和一块DSP,到底是什么问题导致数据总线出问题。

还有一点就是,在这个板子上,就是通过数据线把这四个芯片连了起来,数据线上没有任何串入的电阻和并入的电容,希望各位大虾帮帮忙,困扰了挺久的时间了。