【导读】早在4年前,宜特就开始研究WLCSP第一代FIB电路修补技术,当年不仅入选国际材料工程与科学协会(ASM)所举办的ISTFA论坛,更通过材料科学期刊(jMS)的审核,成为该论文的期刊文章...

近日,宜特利用独特前处理工法,研发出第二代WLCSP(Wafer-level chip scale package,晶圆级芯片尺寸封装)电路修补解决方案,可以更有效缩短工时,提升电路修补成功率。

宜特第一代WLCSPFIB电路修补技术,也从研发阶段,走向开案阶段,成功协助多家电源管理、模拟、多媒体IC设计与手机芯片业者,缩短产品验证及除错的时程,使产品可顺利上市。

今年更再接再厉,开发独特WLCSP电路修补前处理工法,非常荣幸获得IEEE半导体故障分析领域最高殿堂IPFA(International Symposiumonthe Physical and Failure Analysisof Integrated Circuits,集成电路失效分析论坛),邀请宜特发表WLCSP第二代FIB电路修补解决方案。

宜特科技材料分析与FIB工程部经理陈声宇博士表示,WLCSP意指在晶圆切割前,利用锡球来形成接点,直接在晶圆上完成IC封装的技术,比起传统打线封装,可有效缩减封装体积;面对穿戴式、智能手持式装置轻薄化的趋势,具有面积最小、厚度最薄等特征的WLCSP封装方式,也受到越来越多厂商采用。

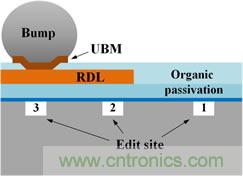

“然而此封装形式的IC产品,在进行FIB线路修补时将面临到两大挑战,一是IC下层的电路,绝大部分都会被上方的锡球与RDL(RedistributionLayer,线路重布层)给遮盖住,这些区域在过往是无法进行线路修补的。二是少数没有遮盖到的部分,也会因上方较厚的Organic Passivation(有机护层),大大增加线路修补的难度与工时。”陈声宇进一步指出。

宜特今年所研发出的第二代WLCSP电路修补技术,已为此类产品带来解决方案,透过独特的前处理工法,任何在锡球、RDL、或有机謢层下方的区域,都能顺利完成电路修补(参见下图);比起利用宜特第一代使用导电电子连接金属导线的线路修补接合方法,施工工时大幅缩短一半,良率提升一倍。

图说:透过独特的前处理工法,任何被锡球(site-3)、RDL(site-2)、或有机謢层(site-1)遮盖的区域都能顺利完成FIB线路修补。

宜特研发技术与设备能量的升级,将可协助使用先进封装的IC设计者,在电路验证、侦错、失效分析上更直接、灵活且快速,加速产品上市时间(Time-to-market)。

除了在先进封装产品上的研发成果,宜特在先进制程上的技术进展也不停歇,日前引进了业界具有极佳分辨率及稳定度的FEIV400ACEFIB机台,能成功执行16nm制程IC的线路修补。