产品特性:

- 具有高击穿电压并基于逻辑制程的CMOS高压晶体管

- 适用于无线设备的功放,能处理用于WiMAX和其它高频应用的功放的高输出要求

- 使用该新技术能够将功放和CMOS逻辑控制电路集成在同一块芯片上

富士通微电子(上海)有限公司近日宣布,富士通实验室和富士通株式会社联合开发出一款具有高击穿电压并基于逻辑制程的CMOS高压晶体管,该晶体管适用于无线设备的功率放大器。作为先进科技的先驱,富士通开发完成了世界上第一代基于45纳米工艺的CMOS晶体管,能够处理10V功率输出,这使得晶体管能够处理用于WiMAX和其它高频应用的功率放大器的高输出要求。这一新技术能够将功能放大器和CMOS逻辑控制电路在同一块芯片上集成,可实现单芯片的工作模式,从而使生产出高性能和低功耗的功能放大器成为可行。

2008年12月15日到17日在旧金山举办的2008年IEEE国际电子元器件大会(IEDM)上已展示该技术的详细信息(会议/报告: 19.1)。

背景

因为用于无线设备的功率放大器产生高频时需要高功率输出,目前广泛使用砷化镓(GaAs)等化合物半导体,功率放大器作为单独的芯片贴装,与通用CMOS逻辑芯片上的控制电路分离。如果在单一芯片上集成所有的功能可降低整个模块的成本,并有可能被用于满足无线设备及无线通信标准(WiMAX和LTE.)的通讯速度要求。这要求晶体管不仅能够兼容CMOS逻辑处理技术,而且能满足WiMAX及其它无线通信标准对功率放大器的要求。

技术挑战

功率放大器在面对高频应用(如WiMAX)时,其所需功率输出会超过使用标准CMOS逻辑制程的晶体管的击穿电压。要克服这一难题并同时维持CMOS工艺技术的兼容性,需要增加晶体管的击穿电压,而击穿电压的增加可通过降低漏极周围的电场来实现,同时要注意电场的调整容易致使晶体管出现故障。另外,高击穿电压的结构往往容易增加晶体管的导通电阻,致使高频时难以获取满意的性能。所以,无论使用种方案都需要增加击穿电压并同时避免导通电阻的升高。

新研发的技术

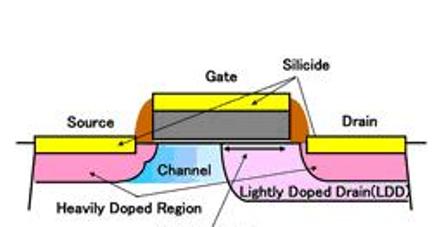

图1: 富士通新研发的晶体管的结构

为应对上述问题,富士通开发出带有下列关键特性的新型晶体管结构(图1):

1.“低掺杂漏极”(LDD)区包围该晶体管的漏极,并与门极重叠。这一结构既能降低水平扩展至漏极的电场,也能降低垂直扩展至门极氧气层的电场,从而增加了击穿电压。

2.晶体管沟道内的掺杂物横向斜度分布。这样能够降低沟道内漏极一侧的掺杂物密度,同时限制漏电阻(漏电阻是导通电阻的重要组成部分)的增加。还能降低横向向漏极扩展的电场,并能增加击穿电压。

通常提高CMOS晶体管击穿电压的方法是增加门极和漏极之间的宽度。与以往的方法相比,这一新结构不增加宽度也能有效抑制导通电阻。

此外,由于该结构只需形成LDD区和定制沟道区两个额外步骤,因此能够实现高度兼容3.3 V I/O的标准晶体管。

效果

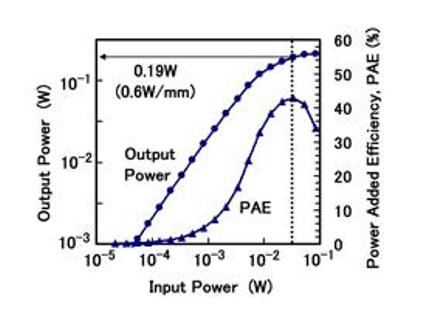

图2: 富士通新型功率晶体管的特性

(测量频率: 2.1 GHz; 门极宽度: 0.32 mm)

富士通通过使用45nm工艺技术把新型晶体管技术应用到3.3 V I/O的标准晶体管上,从而开发出了世界上首个能把击穿电压从6 V 提高到 10 V的晶体管。新型晶体管适用于功率放大器,它在最大振荡频率为43 GHz (图2)时每个1mm门极宽度能够输出0.6 W(0.6 W/mm),展示了其作为功率放大器在面向WiMAX等高频应用方面的卓越性能。新型晶体管在基本的可靠性测试上也取得了良好的测试结果。

未来发展

富士通新型开发的高压晶体管为带高击穿电压的CMOS逻辑晶体管在功率放大器中的使用铺平了道路。富士通将利用该技术的进一步发展,持续在单一芯片上集成功率放大器和控制电路方面做出努力,以实现成本更低和性能更高的功率放大器模块。