【导读】POE (Power Over Ethernet)指的是在现有的以太网Cat.5布线基础架构不作任何改动的情况下,在为一些基于IP的终端(如IP电话机、无线局域网接入点AP、网络摄像机等)传输数据信号的同时,还能为此类设备提供直流供电的技术。POE技术能在确保现有结构化布线安全的同时保证现有网络的正常运作,最大限度地降低成本。

1 概述:

定义:PoE全称Power Over Ethernet,是指10BASE-T、100BASE-TX、1000BASE-T以太网网络供电,即数据线和电源线在同一根网线上传输,其可靠供电的距离最长为100米。

PoE供电系统包含两种设备PSE和PD,PSE(power-sourcing equipment),主要是用来给其它设备进行供电的设备,PD(power device),在PoE供电系统中用来受电的设备。

2 POE主要供电特性

2.1 PSE特性参数:

(1)电压在44~57V之间,典型值为48V

(2)允许最大电流为550mA,最大启动电流为500mA

(3)典型工作电流为10~350mA,超载检测电流为350~500mA

(4)在空载条件下,最大需要电流为5mA

2.2 PD功率等级

PD功率等级分为CLASS 0、CLASS 1、CLASS 2、CLASS 3、CLASS 4、CLASS 5

CLASS 0 设备需要的最高工作功率为0.44W ~12.95W

CLASS 1 设备需要的最高工作功率为0.44W ~3.84W

CLASS 2 设备需要的最高工作功率为3.84W ~6.49W

CLASS 3 设备需要的最高工作功率为6.49W ~12.95W

CLASS 4 设备需要的最高工作功率为12.95W ~25.5W

CLASS 5 设备需要的最高工作功率为>25W

设计师可以根据功率要求将他们的设备指定为特定的级别。

2.3 POE供电的工作过程

在分级阶段,PSE将向PD施加15~20V的电压,并通过测量电流大小来确定PD的特定级别。在此阶段,PD的电源部分将被欠压锁定(UVLO)电路维持在无源状态,以便隔离开关级,直至特征和分级阶段完成。一旦分级完成后,PSE将会向PD提供全额工作电压。

当在一个网络中布置PSE供电端设备时,POE以太网供电工作过程如下所示:

检测:

首先PSE会发送一个测试电压给在网设备以探测受电设备中的一个24.9kΩ共模电阻。测试信号开始为2.5V,然后提升到10V,这将有助于补偿Cat-5电缆自身阻抗带来的损失。因为这种电缆最长可达100m。如果PSE检测到来自PD的适当阻抗特征(24.9kΩ),它便会继续提升电压。如果检测不到特征阻抗,PSE将不会为电缆加电。受电设备电路中的齐纳二极管会保证系统其余部分不受测试信号的干扰。

PD端设备分类:

当检测到受电端设备PD之后,PSE将向PD施加15~20V的电压,并通过测量电流大小来确定PD的特定级别。如果除了探测到第一级的电阻外没发现其他分级电路,该设备被定义成零级别。在此阶段,PD的电源部分将被欠压锁定(UVLO)电路维持在无源状态,以便隔离开关级,直至特征和分级阶段完成。

开始供电:

分级完成后,在一个可配置时间(一般小于15μs)的启动期内,PSE设备开始从低电压向PD设备

a)供电,直至提供48V的直流电源。

b)供电:为PD设备提供稳定可靠48V的直流电,满足PD设备不越过12.95W的功率消耗。

c)断电:若PD设备从网络上断开时,PSE就会快速地(一般在300~400ms之内)停止为PD设备供电,并重复检测过程以检测线缆的终端是否连接PD设备。

3 POE电源模块简介

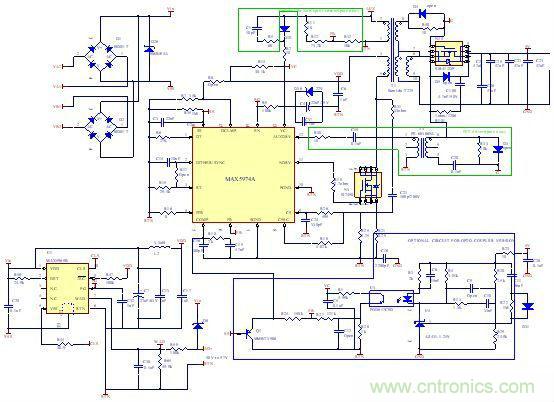

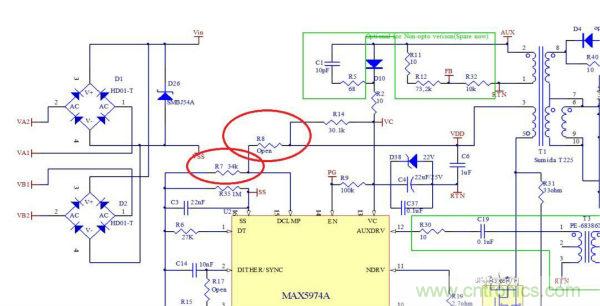

本次POE电源模块采用MAX5969B和MAX5974A芯片来实现,功率等级为CLASS 4的POE电源。POE电源模块的电路拓扑结构采用反激式变换器实现,运用变压器原边反馈稳压以及副边同步整流技术。输入电压范围在36V~57V之间,输出电压稳点在5V,具有过压保护、过流保护等特点。如图1所示为POE电源的原理图。

3.1 POE电源模块芯片

芯片MAX5969B为用电设备(PD)提供符合以太网供电(PoE)系统IEEE802.3af/at标准的完整接口。MAX5969B为PD提供检测信号、分级信号以及带有浪涌电流控制的集成隔离功率开关。发生浪涌期间,MAX5969B将电流限制在180mA以内,直到隔离功率MOSFET完全开启后切换到较高的限流值(720mA至880mA)。器件具有输入UVLO,带有较宽的滞回和长周期干扰脉冲屏蔽,以补偿双绞线电缆的阻性衰减,确保上电/掉电期间无干扰传输。MAX5969B输入端能够承受高达100V的电压。

MAX5969B芯片特性如下:

(1)兼容于IEEE 802.3af/at

(2)2级事件分级

(3)简易的墙上适配器接口

(4)0至5级POE分级

(5)100V绝对最大额定输入

(6)180mA最大浪涌电流限制

(7)正常工作期间电流限制在720mA至880mA

(8)电流限制和折返式保护

(9)传统的36V UVLO (MAX5969A)

(10)IEEE 802.3af/at兼容、40V UVLO (MAX5969B)

(11)过热保护

(12)增强散热的3mm × 3mm、10引脚TDFN封装

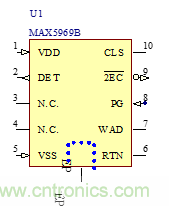

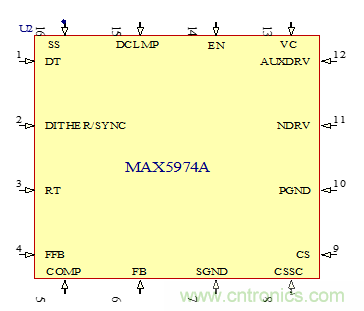

如图2所示为MAX5969B的引脚图,接下来简要介绍下每个引脚。

图2 MAX5969B引脚图

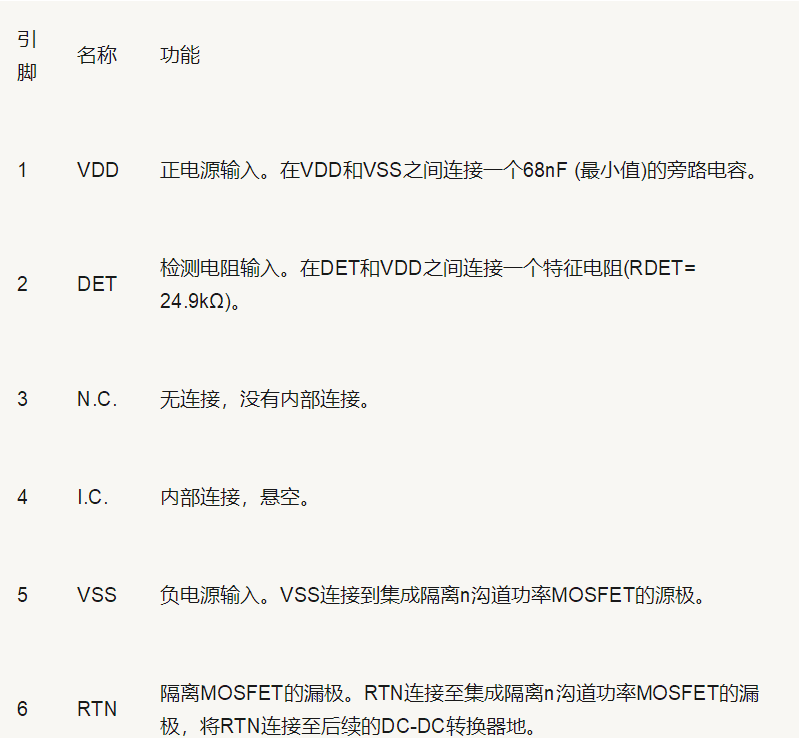

表1 MAX5969B引脚简介

芯片MAX5969B工作过程的简单介绍,MAX5969B有4种不同的工作模式:

PD检测、PD分级、标记事件和PD供电模式。检测模式是用来检测设备是不是PD设备;分级模式是用来给PD设备确定输入功率为多大;标记事件一般用于2级分级模式检测;供电模式为正式给PD设备供电。

当输入电压在1.4V和10.1V之间时器件进入PD检测模式;当输入电压在12.6V和20V之间时,器件进入PD分级模式;一旦输入电压超过VON,器件则进入PD供电模式。

检测模式(1.4V≤ VIN ≤ 10.1V):

检测模式下,PSE向VIN施加1.4V至10.1V范围(最小步长为1V)的两个电压,并记录这两点处的电流测量值。然后,PSE计算DV/DI以确保连接了24.9kΩ特征电阻。在VDD和DET之间连接特征电阻(RDET),以确保正确的特征检测。检测模式下,MAX5969B将DET拉低。当输入电压超过12.5V时,DET变为高阻态。检测模式下,MAX5969B的大多数内部电路都处于关断状态,偏置电流小于10μA。

分级模式(12.6V≤ VIN ≤ 20V) :

分级模式下,PSE根据PD所需的功耗对PD进行分级,使PSE能够有效管理功率分配。0至5级的定义可通过查看数据手册知道(IEEE 802.3af/at标准仅定义了0至4级,5级用于特殊要求)。CLS与VSS之间连接一个外部电阻(RCLS),用于设置分级电流。PSE通过向PD输入施加电压并测量PSE输出的电流来确定PD的级别。当PSE施加的电压在12.6V和20V之间时。PSE使用分级电流信息来对PD功率要求进行分级。分级电流包括RCLS吸收的电流和MAX5969B的电源电流。所以PD吸收的总电流在IEEE 802.3af/at标准的指标范围之内。当器件处于供电模式时,则关闭分级电流。

供电模式(唤醒模式)

当VIN上升到欠压锁定门限(VON)以上时,MAX5969B进入供电模式。当VIN上升到VON以上时,MAX5969B开启内部n沟道隔离MOSFET,将VSS连接至RTN,内部浪涌电流限制设置为135mA (典型值)。当RTN处的电压接近VSS并且浪涌电流降至浪涌门限以下时,隔离MOSFET完全开启。一旦完全开启隔离MOSFET,MAX5969B将电流限制更改为800mA。在功率MOSFET完全开启之前,电源就绪开漏输出(PG)保持为低电平,持续时间至少为,以在浪涌期间禁止后续的DC-DC转换器。

芯片还有一些其它的工作状态,例如欠压锁定、热关断保护、墙上电源适配器检测和工作等。

芯片MAX5974A为宽输入电压范围、有源钳位、电流模式PWM控制器,用于控制以太网供电(PoE)的用电设备(PD)中的正激转换器。MAX5974A适用于通用或电信系统的输入电压范围。芯片MAX5974A独特的电路设计能够在不需要光耦的前提下获得稳定的输出。

MAX5974A有很多特性,以下简要介绍几个:

(1)峰值电流模式控制、有源钳位、正激PWM控制器

(2)无需光耦即可获得稳压输出

(3)100kHz至600kHz可编程、±8%抖动控制的开关频率,可同步至高达1.2MHz

(4)可编程频率抖动,支持低EMI、扩频工作

(5)可编程死区时间、PWM软启动、电流斜率补偿

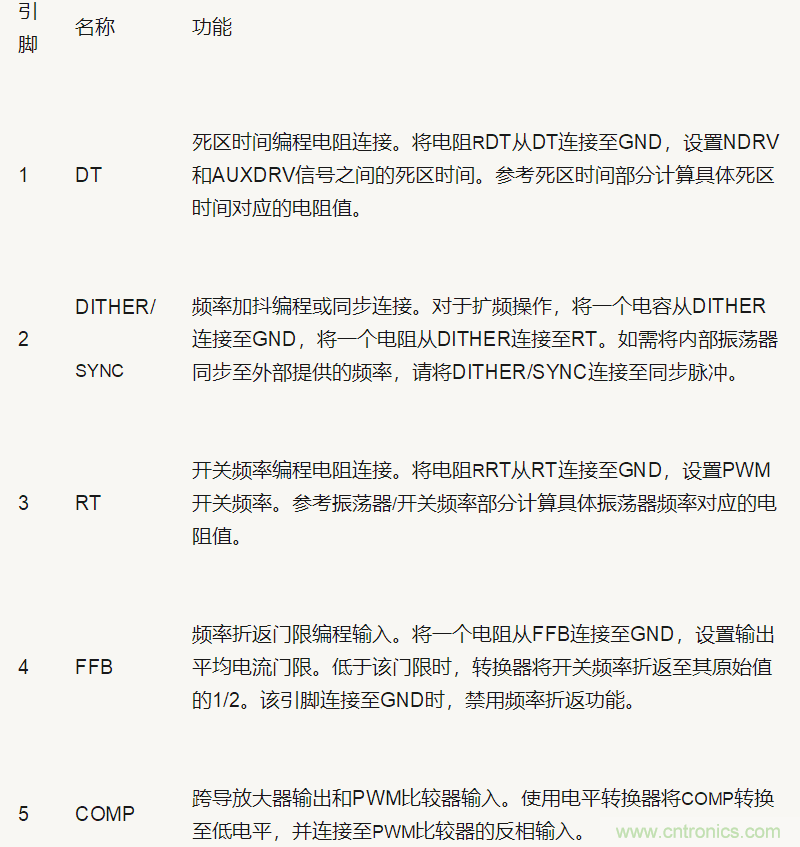

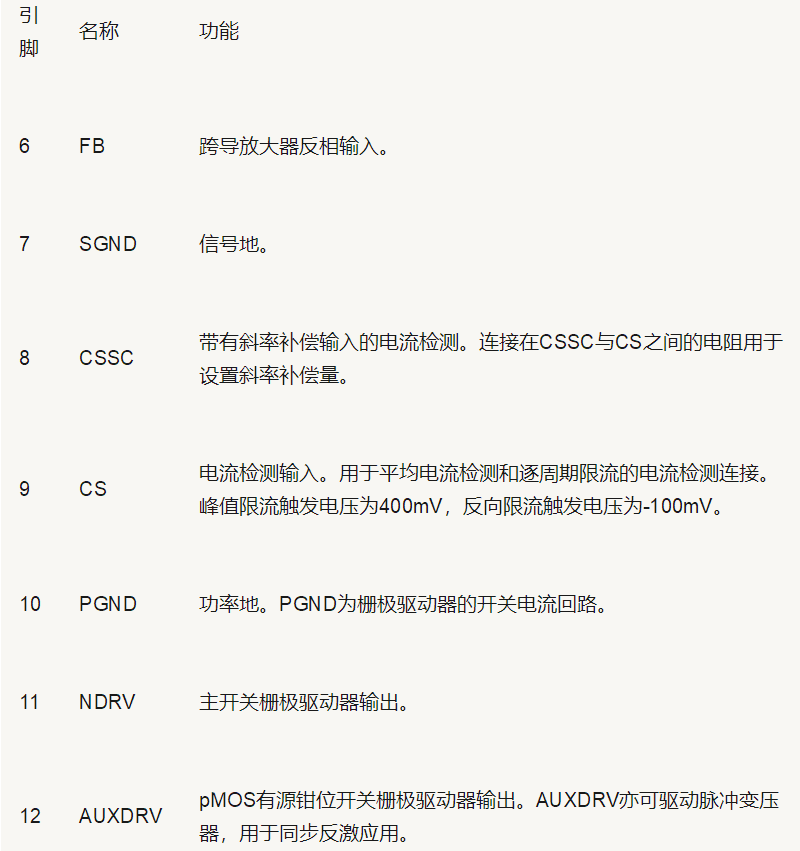

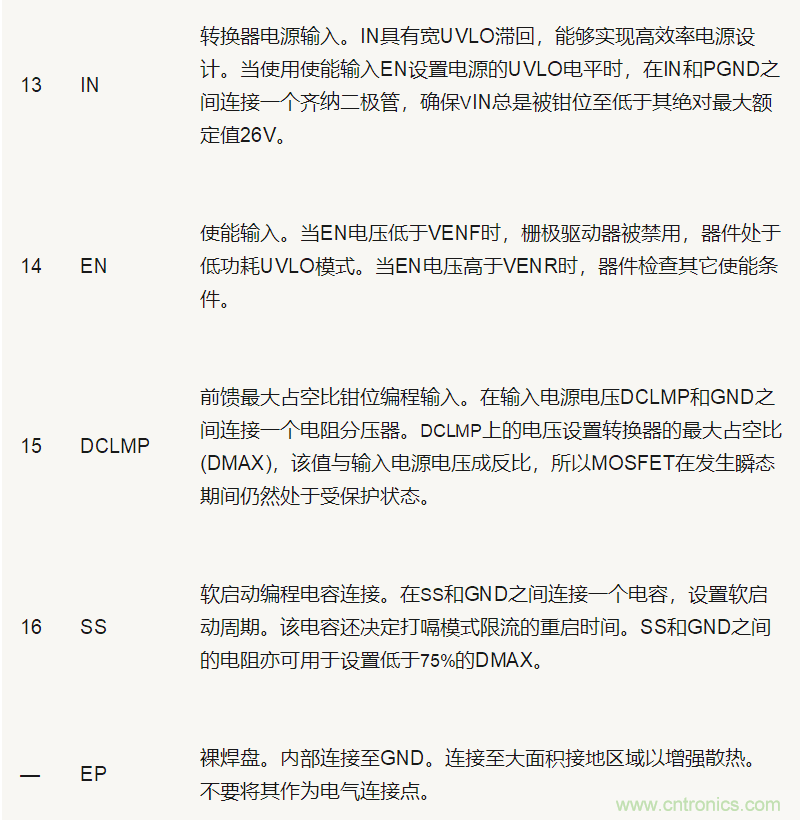

如图3所示为芯片的引脚图。

图3 MAX5974引脚图

表2 MAX5974A引脚简介

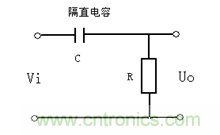

3.2 输入电路以及输出电路简介

输入电压取自于网络端口的48V电源,输入电压经过两个整流桥D1、D2,其中D26是一个瞬态抑制二极管SMBJ54A用来保护输入过压。

输出电压通过反激变压器的副边整流后得到,由于整流后脉动电压较大,所以会在整流后添加输出滤波电容,输出滤波电容一般会选择几个大电容再加一个小电容并联,大电容起到储能和滤波的作用,小电容用来高频去耦,几个电容并联可以将输出电阻降到最小。本模块POE电源选择3颗封装为1206,容值大小为47uF的陶瓷电容。反激变压器选择SIR412DP开关管实现有源整流,利用变压器副边绕组来获得驱动电压,这样变压器原边就不需要消磁电路或者吸收电路,而是把能量用来驱动SIR412DP开关管,实现同步整流技术。开关管的漏极和源极并联RCD吸收电路,用来抑制开关管漏源端的电压尖峰而达到保护开关管的目的。虽然说MOSFET的是一种压控压型的开关管,但是对于开关管开通和关闭都是给开关管的寄生电容充电来打开或关闭,这就需要一定的驱动电流。所以在驱动电路中串联一个10欧姆的电阻。

3.3 芯片外围电路简介

芯片MAX5969B主要作用体现在刚刚上电的时候和PSE供电模块用来通信的芯片,对于每一个POE电源来说,这种类似的芯片是必不可少的。市面上有些号称是POE电源的往往只是把48V的电压变成5V或者其它的电压,在上电的时候并没有检测、分级的阶段,这对于受电设备来说是危险的。检测电源是POE电源还是非POE电源的一般方法是,拿万用表测量供电脚,一般是网络端口的4,5、7,8脚,如果端口输出是稳定的48V电压,这说明电源是非POE电源;如果测量的电压在2~10V跳动,则说明电源是POE电源,电压跳动是在对PD端进行检测。

芯片MAX5969B的VDD是电源引脚,VDD和VSS之间接有0.1uF的电容用来旁路,电容C7和C13用来储能和滤波。

DET接一个24.9K的电阻到Vin,这个电阻是特征电阻不可更改,要是把这个电阻的阻值改变了,POE电源工作会不正常。

VSS引脚是接输入整流过后的地端,VSS内部通过MOSFET管和变压器原边的接地端相连。当芯片处于检测与分级阶段时候,内部MOSFET处于断开的状态。

RTN引脚接变压器原边的地端,是后继DC-DC的功率地端。

WAD引脚是用来接墙上适配器电源供电,本模块的POE电源没有用上墙上适配器,但是在电路设计的时候也考虑到了,只是没有焊接相关器件。

PG引脚内部是MOSFET漏极输出,在芯片内部的MOSFET完全开启之前,PG保持为低电平,PG端接MAX5974A的使能端,故PG在保持低电平期间,MAX5974A是处于不工作状态。PG外接1nF的电容旁路。

2EC引脚是2级事件检测脚,本模块没有用上直接上拉100K电阻到RTN,以防PD设备处于2级状态时,2EC引脚有一个回路。

CLS引脚是分级电阻输入引脚,CLS引脚接多大电阻到VSS地端,就决定了POE电源是处于哪一级。可查看数据手册知当接30.9欧姆电阻时,PD设备设置为4级电路状态,也就是说PD设备要消耗12.95-25.5W的功率。

芯片MAX5974A是一款电源管理芯片,芯片内部集成了许多功能,只要根据芯片数据手册推荐的外围电路搭建方法,只需简单的配置些电容和电阻很快就可以设计出一块电源模块。接下来将介绍芯片每个引脚外围电路的搭建,来更好的理解芯片以及反激式开关电源。

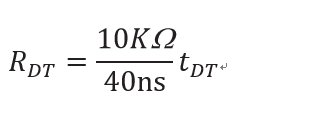

DT引脚是用来设置死区时间的,由于MAX5974A这款芯片提供了两个栅极驱动器输出,一个是NDRV主开关栅极驱动器输出,是用来驱动变压器原边是处于断开状态还是出来接通状态。一个是AUXDRV是用来给变压器副边开关管实现同步整流的驱动信号,由于变压器原边开关管和变压器副边开关管不能够同时开启,尽管NDRV和AUXDRV是互补输出的,但是由于开关管本身的开通和关断过程不理想,在开通和关断的时候有一定的时间延迟,故此需要添加一定的死区时间。死区时间设置时间在40ns至400ns之间,死区时间的设置是通过外接一个电阻到RTN地端,具体多大的电阻设置多长的死区时间,可通过如下公式得到:

本模块选择=27KW,死区时间就为108ns,对于这个死区时间已经足够了,因为本次使用的MOSFET的延迟时间都在40ns以内。

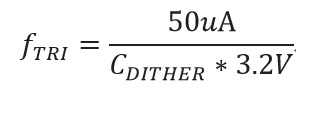

DITHER/SYNC引脚为频率加抖编程或者同步连接引脚。在DITHER/SYNC和RTN地之间连接一个电容,在DITHER/SYNC和RT之间连接一个电阻,可以在范围内对转换器的开关频率加抖,从而降低EMI。具体过程是DITHER/SYNC处的电流源以50uA电流将电容C14充电至2V。达到该点后,以50uA电流将C14放电至0.4V。电容充电和放电会在DITHER/SYNC上产生一个三角波,峰值分别为0.4V和2V,通常情况下,频率为1KHZ。电容C14的计算公式为:

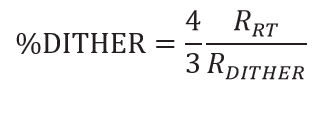

本模块选择C14=10nF,其中连接电阻公式如下:

其中,%DITHER为加抖量,表示为开关频率的百分比。将RDITHER设置为10 RRT,产生±10%的抖动。本模块中没有焊接次电阻,但是也预留了位置,需要的时候可以焊上次电阻。

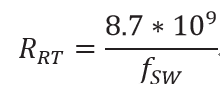

RT引脚是开关频率编程电阻连接。将连接至RTN地,设置PWM开关频率在100KHZ~600KHZ之间。可参考如下公式:

为PWM波的开关频率,本模块电源选择为29.4K,也就是说开关频率为296KHZ。

FFB引脚是频率折返门限编程输入。将一个电阻从FFB连接至RTN地,设置输出平均电流门限。低于该门限时,转换器将开关频率折返至其原始值的1/2。该引脚连接至RTN地时,禁用频率折返功能。这脚的功能是为了在轻载的时候降低开关频率,以降低开关损耗,提高转换器效率,节约能源的作用。连接的电阻计算可通过如下公式得到:

其中,RFFB为FFB和RTN地之间的电阻,ILOAD(LIGHT)为轻载条件下触发频率折返的电流,RCS为连接在CS和RTN地之间的检测电阻,IFFB为FFB源出至RFFB的电流(30µA,典型值)。本模块通过一个0欧姆电阻相连。

COMP引脚是跨导放大器输出和PWM比较器输入。使用电平转换器将COMP转换至低电平,并连接至PWM比较器的反相输入。此引脚是用来改善环路稳定性,使输出电压稳定纹波小。本模块采用二型环路补偿网络来实现环路的稳定,具体由原理图中C15、C16和R10构成的电路来完成。

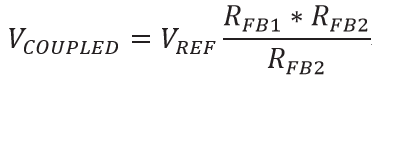

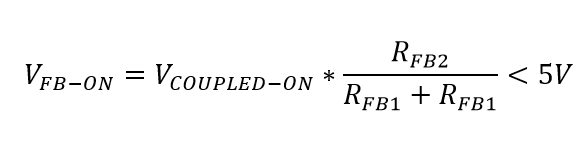

FB引脚是跨导放大器反相输入。MAX5974A包含一个带有采样-保持输入的内部误差放大器。误差放大器的同相输入连接至内部基准,在反相输入提供反馈。高开环增益和单位增益带宽可实现良好的闭环带宽和瞬态响应。采用下式计算变压器原边耦合的输出电压:

MAX5974A的为1.52V,其中反馈电压可通过如下公式得到:

本模块的

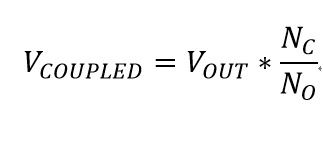

本模块的反馈电压取自于变压器原边耦合的电压,而没有使用传统的利用TL431和PC817的方案来获得反馈电压从而使输出电压稳定,但是在电路设计的时候也预留了TL431和PC817反馈的方案来获得输出电压稳定。变压器原边耦合的电压还有一个作用就是给MAX5974A芯片提供电源输入。可通过设置反馈部分的电压来改变输出电压,可以由如下公式可知:

其中, VOUT为输出电压, NC/NO为耦合输出与主输出绕组的匝数比。选择的匝数比要使VCOUPLED高于UVLO关断电平(7.35V,最大值)达一定裕量,该裕量由“跨越”一次掉电所需的保持时间决定。

SGND引脚为信号地引脚连接到RTN地。

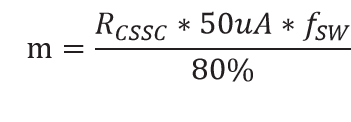

CSSC引脚带有斜率补偿输入的电流检测。连接在CSSC与CS之间的电阻用于设置斜率补偿量。器件在CSSC端产生电流斜坡,其峰值在振荡器占空比为80%时达50μA。连接在CSSC至CS的外部电阻将该电流斜坡转换至可编程斜率补偿幅值,加至电流检测信号,用于稳定峰值电流模式控制环路。斜率补偿信号的变化率由下式给出:

其中,m为斜率补偿信号的变化率;RCSSC为连接在CSSC和CS之间的电阻值,用于设置变化率;fSW为开关频率。本模块选择电阻R18为4.02K。

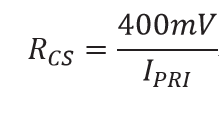

CS引脚是电流检测输入。用于平均电流检测和逐周期限流的电流检测连接。峰值限流触发电压为400mV,反向限流触发电压为-100mV。连接在n沟道MOSFET源极和RTN地之间的电流检测电阻(典型应用电路中的RCS)用于设置限流值。限流比较器的电压触发电平(VCS-PEAK)为400mV。利用下式计算RCS值:

其中,IPRI为变压器原边的峰值电流,该电流也流经MOSFET。当该电流(通过电流检测电阻)产生的电压超过限流比较器门限时,MOSFET驱动器(NDRV)在35ns()内终止电流导通周期。本模块的限流电阻选择R21、R25为1206封装阻值为0.25欧姆。利用一个小型RC网络,对检测波形上的前沿尖峰进行额外的滤波。滤波电路的角频率设置在10MHz至20MHz之间。本模块选择R26为499欧姆和电容C24为330pF。

PGND引脚为功率地接RTN地端。PGND为栅极驱动器的开关电流回路。

NDRV引脚为主开关栅极驱动器输出。此脚通过一个小电阻接到主开关管SI7450的栅极来驱动SI7450。此脚输出的频率为296KHZ。

AUXDRV引脚pMOS有源钳位开关栅极驱动器输出。AUXDRV亦可驱动脉冲变压器,用于同步反激应用。此引脚和NDRV为互补输出,本模块是采用变压器副边耦合来驱动输出整流开关管,故此脚并没有用上,处于悬空状态,但是在设计的时候,把其驱动的外围电路也包含了进去,需要用其来驱动输出整流开关管时可以把相关电路焊上,但是不能同时有变压器副边耦合驱动和用AUXDRV驱动存在。

VC引脚是转换器电源输入。IN具有宽UVLO滞回,能够实现高效率电源设计。当使用使能输入EN设置电源的UVLO电平时,在IN和PGND之间连接一个齐纳二极管,确保VIN总是被钳位至低于其绝对最大额定值26V。本模块的电源输入取自变压器原边耦合的电压,变压器原边耦合的电压通过D10整流后给芯片的VC,芯片VC和RTN地之间接有22V稳压管D28以及电容C4和C37。其中与二极管D10并联的RC电路是用来,在上电瞬间防止二极管有大电流的冲击,在上电瞬间电流先通过RC电路,而保护二极管D10。

EN引脚使能输入。当EN电压低于VENF时,栅极驱动器被禁用,器件处于低功耗UVLO模式。当EN电压高于VENR时,器件检查其它使能条件。使能输入EN用于使能或禁用器件。EN连接至IN时,器件始终保持工作。EN连接至地时,可禁用器件,并将电流损耗降低至150μA。本模块的EN端通过一个100K的电阻连接到VC端,EN端也和MAX5969B的PG引脚相连,以用于在供电之前禁用MAX5974B。

DCLMP引脚是前馈最大占空比钳位编程输入。在输入电源电压DCLMP和GND之间连接一个电阻分压器。DCLMP上的电压设置转换器的最大占空比(DMAX),该值与输入电源电压成反比,所以MOSFET在发生瞬态期间仍然处于受保护状态。可以由如下公式得到分压电阻:

本模块

分别为原理图中的R8和R7。

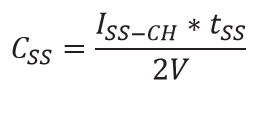

SS引脚是软启动编程电容连接。在SS和GND之间连接一个电容,设置软启动周期。该电容还决定打嗝模式限流的重启时间。SS和GND之间的电阻亦可用于设置低于75%的DMAX。在SS和GND之间连接一个电容CSS,设置软启动时间。VSS控制启动期间的振荡器占空比,使占空比缓慢、平滑地增大至其稳态值。按下式计算CSS值:

其中,ISS-CH (10μA,典型值)为软启动期间的CSS充电电流,tSS为设置的软启动时间。通过在SS和地之间连接电阻,可将SS上的电压设为低于2V。VSS计算如下:

本模块电源选择电容C3=22nF,电阻R35=1MW。

3.3 变压器和开关管的选择

反激变压器设计的成功与否很大一部分要取决于变压器设计的好坏,不同的电路拓扑结构有不同的计算公式,但是基本都是基于AP法来设计变压器。有些做电源具有丰富经验的人往往能够设计出很好的变压器,并且在设计的时候并没有过多的计算。通过公式所计算出来的变压器参数往往只有变压器匝比、线径、变压器磁芯以及变压器骨架等,要想设计一个好的变压器只有这些是不够的,还要考虑变压器的绕法,变压器怎样绕是一个重要的参数。因为不同的变压器绕法所得到的变压器最终性能有很大差别,比如采用三明治绕法的变压具有较低的漏感。反正变压器的设计有太多东西需要考虑,如果所绕的变压器性能较差,可以适当调整匝数、改变绕法或者换一个变压器磁芯等。

本模块选用外购的变压器Sumida T225,因为本模块的开关频率较高,对于变压器尺寸也有所要求,经过多次讨论决定外购变压器而不是自己绕。通过测试发现此变压器性能很好,变压器在重载的时候没有什么异常发生,输出电压也正常。

反激式开关电源的开关管选择要满足漏源能够承受输入电压外加变压器副边耦合过来的电压的1.5倍,才能保证开关管不会在关断的时候被击穿。开关管漏源也要能够流过2倍的输入电流,才能保证开关管不会因过流导致损坏。开关管的损耗在整个电源模块损耗中占有一定比例,一般会选择开关管上升和下降时间短的MOSFET,保证在开关管导通和关闭的一段时间里电压和电流叠加的部分少,降低开关管的损耗。

4 电源PDN和纹波噪声

4.1 电源PDN

电源纹波噪声测试是一个比较复杂的测试难题,不同方法测量到的结果不同,即使同一种测试方法不同人测试结果一般也会存在差别。

对于终端类产品,不管是CPU、GPU、DDR等,其芯片内部都有成千上万的晶体管,芯片内不同的电路需要不同的电源供电,常见有Vcore、Vcpu、Vmem、VIO、Vgpu、Vpll等,这些电源有DC-DC电源模块供电,也有LDO电源模块供电,都统一由PMU来管理。

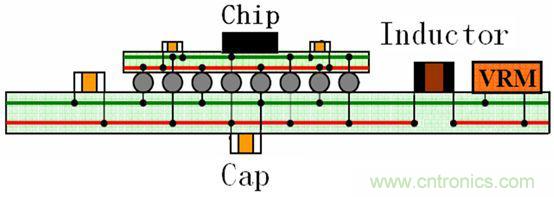

如图4所示,为芯片的PDN图,芯片的供电环路从稳压模块VRM开始,到PCB的电源网络,芯片的ball引脚,芯片封装的电源网络,最后到达die. 当芯片工作在不同负载时,VRM无法实时响应负载对电流快速变化的需求,在芯片电源电压上产生跌落,从而产生了电源噪声。对于开关电源模块的VRM,电源自身会产生和开关频率一致的电源纹波,始终叠加在电源上输出。对于电源噪声,需要在封装、PCB上使用去耦电容,设计合理的电源地平面,最终滤去电源噪声。对于电源纹波,需要增大BULK电感或者BULK电容。

图4 芯片电源分布网络(PDN)示意图

对于板级PCB设计,当频率达到一定频率后,由于走线的ESL、电容的ESL的影响,已经无法滤去高频噪声,业界认为PCB只能处理100MHz以内的噪声,更高频率的噪声需要封装或者die来解决。因此对于板级电源噪声测试,使用带宽500M以上的示波器就足够了。一般情况下,示波器的带宽越大,低噪也会随之上升,因此建议测试电源时示波器的带宽限制为1GHz。

4.2 电源纹波和电源噪声

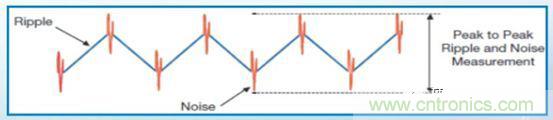

电源纹波和电源噪声是一个比较容易混淆的概念,如下图5所示,蓝色波形为电源纹波,红色波形为电源噪声。电源纹波的频率为开关频率的基波和谐波,而噪声的频率成分高于纹波,是由板上芯片高速I/O的开关切换产生的瞬态电流、供电网络的寄生电感、电源平面和地平面之间的电磁辐射等诸多因素产生的。因此,在PMU侧测量电源输出为纹波,而在SINK端(耗电芯片端,如AP、EMMC、MODEM等)测量的是电源噪声。

图5 电源纹波噪声图

电源纹波测量时,限制示波器带宽为20MHz,测量PMU电源输出的波形峰峰值即可电源纹波。由于PMU芯片在设计完成后,芯片厂商会做负载测试,测试PMU在不同负载时输出电源的纹波情况,因此在终端类产品板上,没必要在做这方面的测试,纹波大小参考PMU手册即可。

电源噪声测试时,测试点放在SINK端,由于SINK端工作速度大都在几十MHz以上,因此示波器带宽设置为全频段(最高为示波器带宽上限),测试点要尽量靠近测试芯片的电源引脚,如果存在多个电源引脚,应该选择距离PMU最远端的那个引脚。电源噪声跟PCB布局布线,DECAP电容的位置的位置相关,同时电源噪声影响CPU的工作状态和单板的EMI,终端类产品板需要对每块单板测试电源噪声。

5 常见的纹波噪声测试方案

5.1 纹波噪声测试基本要求

目前芯片的工作频率越来越高,工作电压越来越低,工作电流越来越大,噪声要求也更加苛刻,以MSM8974的CORE核为例,电压为0.9V,电流为3A,要求25MHz时,交流PDN阻抗为22mohm,电源噪声要求在±33mV以内。对于DDR3芯片,要求VREF电源噪声在±1%以内,若1.5V供电,则噪声峰峰值不大于30mV。

这类低噪声的电源测试非常具有挑战,影响其测量准确性的主要有如下几点:

(1)示波器通道的底噪;

(2)示波器的分辨率(示波器的ADC位数);

(3)示波器垂直刻度最小值(量化误差);

(4)探头带宽;

(5)探头GND和信号两个测试点的距离;

(6)示波器通道的设置;

在测试电源噪声时,要求如下条件:

(1)需要在重负载情况下测试电源纹波;

(2)测试电源纹波时应该将CPU、GPU、DDR频率锁定在最高频;

(3)测试点应该在SINK端距离PMU最远的位置;

(4)测试点应该靠近芯片的BALL;

(5)带宽设置为全频段;

(6)示波器带宽大于500MHz;

(7)噪声波形占整个屏幕的2/3以上或者垂直刻度已经为最小值;

(8)探头地和信号之间的回路最短,电感最小;

(9)测试时间大于1min,采样时间1ms以上,采样率500Ms/s以上;

(10)纹波噪声看Pk-Pk值,关注Max、Min值;

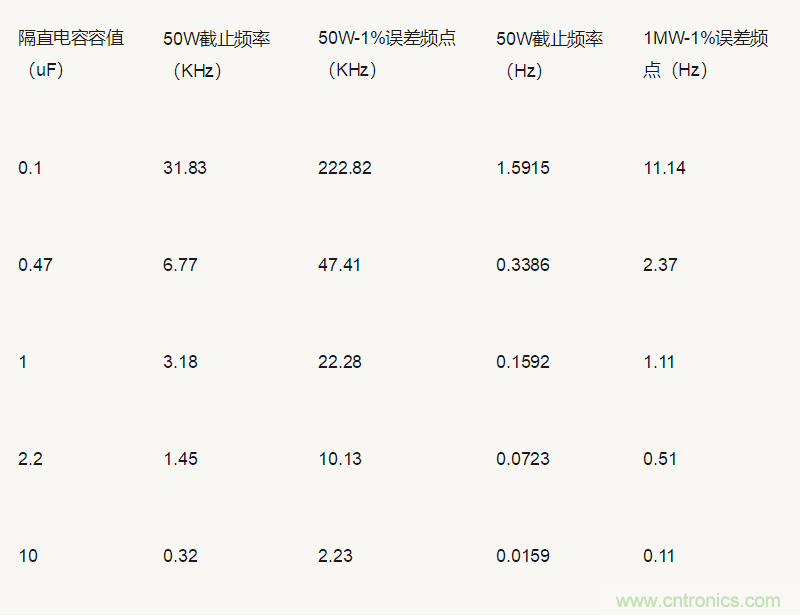

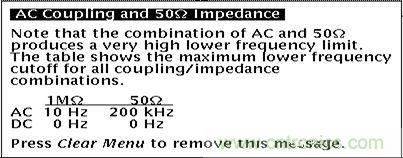

5.2 高通滤波器特性分析

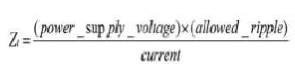

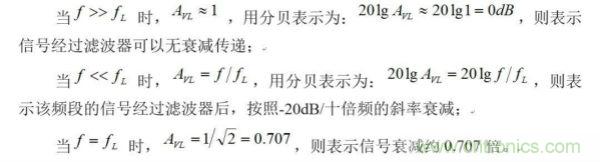

示波器有AC和DC两种耦合方式,当采用AC耦合时,其内部等效电路如图6所示,C为隔值电容,R为终端对地阻抗,Vi为输入信号,Vo为测量信号,滤波器的截止频率为

为信号频率,则有:

图6加隔值电容后高通滤波器等效电路

表3 不同隔值电容对应的频点

5.3 无源探头DC耦合测试

使用无源探头DC耦合测试,示波器内部设置为DC耦合,耦合阻抗为1Mohm,此时无源探头的地线接主板地,信号线接待测电源信号。这种测量方法可以测到除DC以外的电源噪声纹波。

如图7所示,当采用普通的鳄鱼夹探头时,由于地和待测信号之间的环路太大,而探头探测点靠近高速运行的IC芯片,近场辐射较大,会有很多EMI噪声辐射到探头回路中,使测试的数据不准确。为了改善这种情况,推荐用无源探头测试纹波时,使用右图中的探头,将地信号缠绕在信号引脚上,相当于在地和信号之间存在一个环路电感,对高频信号相当于高阻,有效抑制由于辐射产生的高频噪声。更多时候,建议测试者采用第三种测试方法,将一个漆包线绕在探头上,然后将漆包线的焊接到主板地网络上,移动探头去测试每一路电源纹波噪声。同时无源探头要求尽量采用1:1的探头,杜绝使用1:10的探头。

图7 无源探头地线两种处理方法

对于示波器,若垂直刻度为xV/div,示波器垂直方向为10div,满量程为10xV,示波器采样AD为8位,则量化误差为10x/256 V。例如一个1V电源,噪声纹波为50mV,如果要显示这个信号,需要设置垂直刻度为200mV/div,此时量化误差为7.8mV,如果把直流1V通过offset去掉,只显示纹波噪声信号,垂直刻度设置为10mV即可,此时的量化误差为0.4mV。

使用无源探头DC耦合测试,示波器设置如下:

(1)1Mohm端接匹配;

(2)DC耦合;

(3)全带宽;

(4)offset设置为电源电压;

5.4 无源探头AC耦合测试

使用无源探头DC耦合需要设置offset,对于电源电压不稳定的情况,offset设置不合理,会导致屏幕上显示的信号超出量程,此时选择AC耦合,使用内置的搁置电路来滤去直流分量。对于大多数的示波器,会有如下参数,设置为AC耦合,此时测量的为10Hz以上的噪声纹波。

图8 示波器两种耦合方式频点

使用无源探头AC耦合测试,设置如下:

(1)1Mohm端接匹配;

(2)AC耦合;

(3)全带宽;

(4)offset设置为0

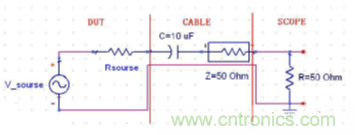

5.5 同轴线外部隔直电容DC50欧耦合测试

由于无源探头的带宽较低,而电源开关噪声一般都在百MHz以上,同时电源内阻一般在几百毫欧以内,选择高阻1Mohm的无源探头对于高频会产生反射现象,因此可以选择用同轴线来代替无源探头,此时示波器端接阻抗设置为50欧,与同轴线阻抗相匹配,根据传输线理论,电源噪声没有反射,此时认为测量结果最准确。

利用同轴线的测量方法,最准确的是采用DC50欧,但是大部分示波器在DC50欧时offset最大电压为1V,无法满足大部分电源的测量要求,而示波器内部端接阻抗为50欧时,不支持AC耦合,因此需要外置一个AC电容,如图9所示,当串联电容值为10uF时,根据表3可以看到,此时可以准确测试到2KHz以上的纹波噪声信号。

图9 同轴线DC50测量图

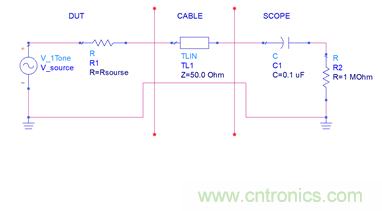

5.6 同轴线AC1M欧耦合测试

由于从PMU出来的电源纹波噪声大多集中在1MHz以内,如果采用同轴线DC50外置隔直电容测量方法,低频噪声分量损失较为严重,因此改用图10所示的测量方法,利用同轴线传输信号,示波器设置为AC1M,这样虽然存在反射,但是反射信号经过较长CABLE线折返传输后,影响是有限的,示波器在R2上采集电压值可以认为仍然可以被参考。

图10 同轴线AC1M测量图

为了避免反射,在同轴线接到示波器的接口处端接一个50ohm电阻,使示波器输入阻抗和cable线特征阻抗匹配。

图11 同轴线AC1M测量改进图

5.7 差分探头外置电容DC耦合测试

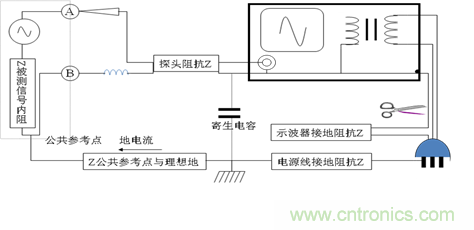

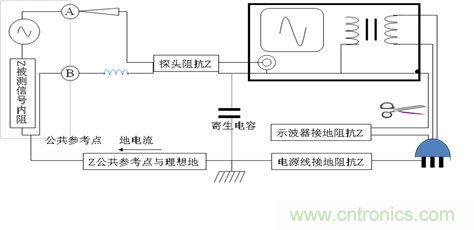

由于示波器的探头地和机壳地通过一个小电容接在一起,而示波器的机壳地又通过三角插头和大地接在一起,在实验室里,几乎所有的设备地都和大地接在一起,示波器内部地线接法如图12所示,因此上面介绍的两种方法都无法解决地干扰问题,为了解决这个问题,需要引入浮地示波器或者差分探头。

图12示波器内部地线接法

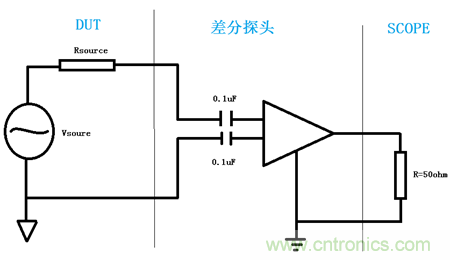

如图13所示,为差分接法,由于差分探头为有源探头,外置差动放大器,可以将待测信号通过差分方式接入,使示波器的地和待测件地隔离开,达到浮地效果。但是差分探头在示波器内部只能DC50欧耦合,而offset最大一般不超过1V,因此需要在差分探头上串联隔直电容。使用差分探头测量时关键是探头的CMRR要足够大,这样才能有效抑制共模噪声

图13差分探头外置电容DC耦合接法示意图

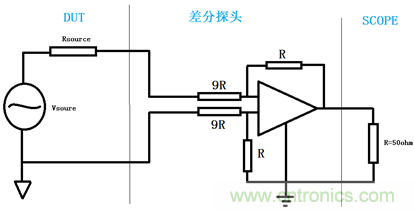

5.8 差分探头衰减DC耦合测试

当采用差分探头外置电容DC耦合时,同样存在截止频率的问题,测量的结果会损失一些低频分量,为了解决这个问题,可以将差分探头衰减10倍,示波器会将采集到的电压值乘10显示出来,这个时候offset设置也会放大到10V,能够满足终端类产品的直流电压偏置。

图14 差分探头衰减DC耦合测试接法示意图

6 电源模块电压测试

由于本模块是POE电源,测试所使用的输入电压取自于网口,PSE供电模块会和本模块先进行握手通信,PSE设备确定后面所接的是PD设备后,才给PD设备供电。如图15所示为一个PoE SWITCH设备。

图15 PoE SWITCH设备

如图16所示为本模块电路,电路长大约6.2cm,宽大约2.65cm,高大约1.5cm。

图16 POE电源模块

由于给POE电源是通过网口供电的,本模块没有特别设计一个网络端口来给供电,而是使用“硬件十万个为什么”提供的开发板,此开发板是用来给物联网编程用的,属于工业兼学习使用的一块开发板,可以使用开发板来实现wifi、GPRS、蓝牙、串口、LORA、POE等功能的使用,故直接选择此块开发板来实现网络端口供电。如图17所示为网络供电端口。

图17 网络端口供电模块

6.1 输入电压测量

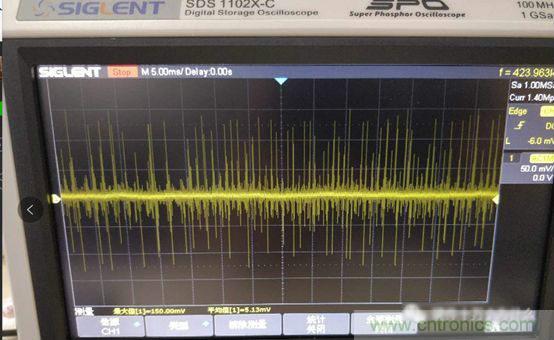

图18所示为通过网络端口过后在POE电源输入端口测的电压,此次所使用的示波器是鼎阳牌SDS1000X-C数字示波器。

图18 输入电压波形

输入电压也有一定的纹波,图19所示就是输入电压的纹波,可以看出纹波还是比较小的,是可以接受的纹波范围。

图19 输入电压纹波测试

6.2 输出电压测量

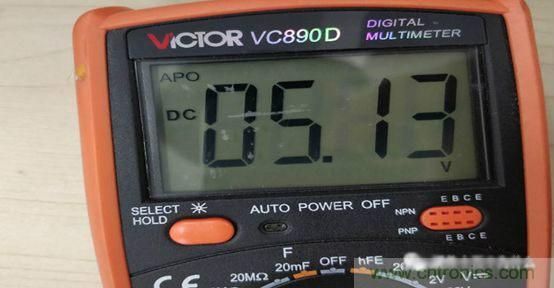

本模块输出电压应该是5V输出,但是由于很难把电压一直稳定在5V不变。

图20所示就是输出电压测试,从万用表中看出,输出电压在5.1V。

图20 输出电压测试

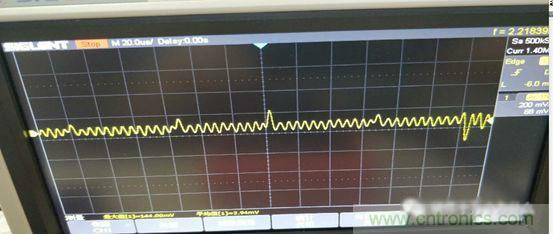

输出电压也是有纹波的,图21所示就是输出电压的纹波测试图。

图21 输出电压纹波

从输出纹波可以看出,此纹波在可接受范围内的。

7 总结

本文档简要介绍了POE电源的基础知识,以及整块电路芯片以及元件选型,电路原理的介绍。电源纹波的产生以及测试方法的介绍,POE电源的测试设备介绍,以及输入输出电压的测量等。

推荐阅读: