【导读】随着集成电路设计迈入超大规模时代,芯片规模已从早期小规模集成电路的数千门级,跃升至当前先进制程下的数十亿门级。这一指数级增长不仅带来了功能复杂度的爆发式提升,更使芯片验证环节面临“验证鸿沟”——传统基于仿真的验证手段,因算力消耗大、迭代周期长,难以覆盖超大规模设计的全功能场景,无法满足产品快速上市对高效、精准验证的需求。

随着集成电路设计迈入超大规模时代,芯片规模已从早期小规模集成电路的数千门级,跃升至当前先进制程下的数十亿门级。这一指数级增长不仅带来了功能复杂度的爆发式提升,更使芯片验证环节面临“验证鸿沟”——传统基于仿真的验证手段,因算力消耗大、迭代周期长,难以覆盖超大规模设计的全功能场景,无法满足产品快速上市对高效、精准验证的需求。

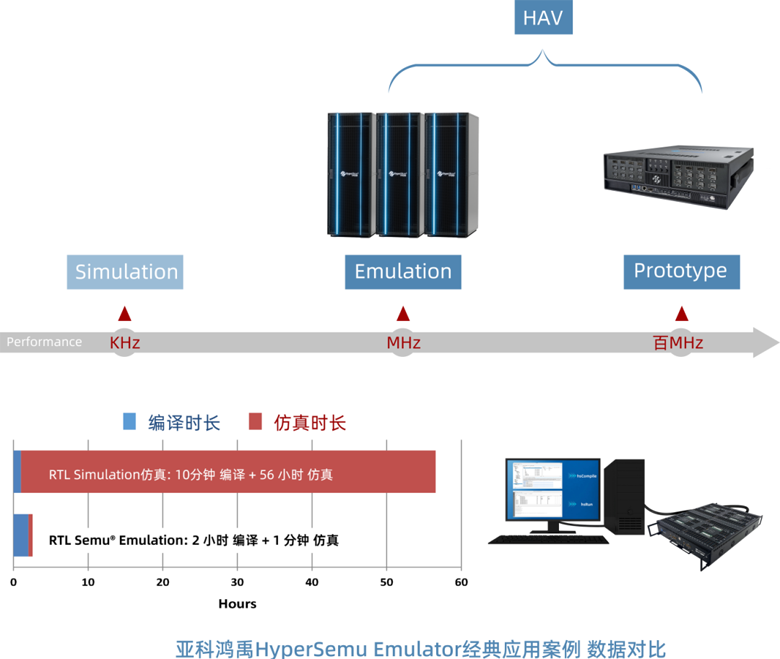

在此背景下,硬件辅助验证(HAV: Hardware-Assisted Verification)凭借其接近真实芯片的运行速度和全功能映射能力,成为弥合这一鸿沟的核心技术,而将芯片设计高效映射到验证芯片阵列的“分割技术”,则是决定硬件辅助验证性能的关键。

硬件辅助验证分割:从需求到核心价值

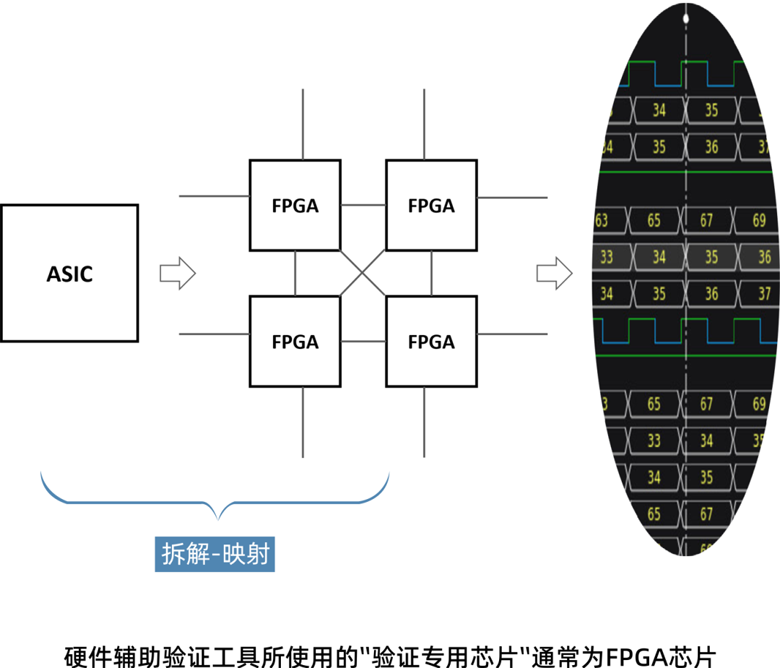

硬件辅助验证的核心逻辑,是将超大规模芯片的RTL(寄存器传输级)设计,拆解为多个可适配单颗验证专用芯片(通常为FPGA芯片)资源的子模块,再通过验证芯片阵列的协同工作,模拟真实芯片的功能与应用环境。这一“拆解-映射”过程即为分割,其本质是解决“超大规模设计”与“单颗验证芯片有限资源”之间的矛盾。

分割的质量直接决定硬件辅助验证的最终效果:

优质分割:可实现验证芯片资源(逻辑单元、存储单元、I/O引脚)的均衡利用,最大限度减少跨验证芯片的信号交互(即“割边”),降低关键路径延时,保障硬件辅助验证的高工作频率,同时减少人工调整成本。

劣质分割:会导致部分验证芯片资源过载(需手动删减功能)、部分资源闲置,或跨验证芯片割边过多。前者可能引入功能性错误,后者会因外部连线延时增加,大幅拉低验证频率,甚至无法满足软件调试对实时性的需求。

经典图分割算法:大规模设计分割的基础框架

芯片设计的分割问题,在数学模型上可转化为“图分割”——将芯片的模块(节点)与模块间的信号连接(边,含权重)构成的图,拆分为多个子图,且需满足“分区资源平衡”(各子图适配单颗验证芯片资源)与“割边最小”(减少跨验证芯片信号交互)两大目标。

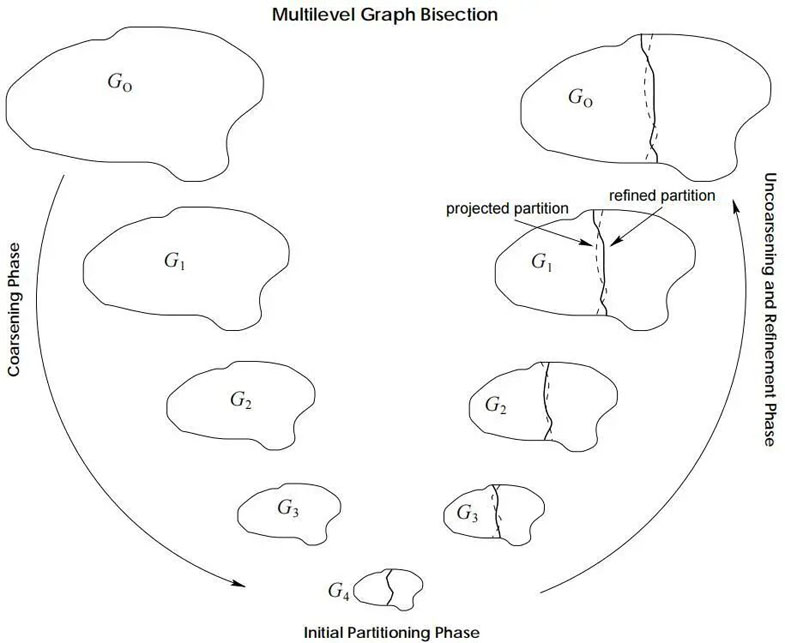

主流的“多层次图划分”框架,通过“粗化-初始划分-细化”三步流程,高效解决大规模图分割问题,其核心逻辑如下:

粗化(Coarsening):简化规模,保留核心结构

核心目标:将百万级节点的原始设计图,通过迭代合并,逐步压缩为数千级节点的“粗化图”,在降低后续计算复杂度的同时,完整保留原图中“高权重边”(如关键信号连接)和”紧密关联节点”(如同一功能模块的子模块)的结构特征。

实现逻辑:采用“节点匹配”策略,优先合并满足以下条件的节点:

➭节点间边的权重高(信号交互频繁)

➭节点的资源属性相似(如均为逻辑运算模块,或均为存储模块)

➭合并后不破坏局部功能完整性(如不拆分一个完整的运算单元)

每轮合并后生成“超节点”(由多个原始节点构成)和“超边”(由超节点间的原始边合并而成),最终形成一系列规模递减的粗化图。

初始划分(Initial Partitioning):为粗图制定基础方案

核心目标:在规模最小的粗化图上生成首个满足“资源平衡”与“割边最小”的分区方案,为后续细化提供起点。

常见算法:

➭随机划分:将粗化图的超节点随机分配到目标分区(分区数量=验证芯片数量),优点是计算速度快,可作为基础方案;缺点是割边较多,需后续优化

➭贪心划分:基于“局部最优”原则,优先将连接紧密(超边权重高)的超节点分配到同一分区,逐步减少跨区超边数量。例如,先将权重最高的超边连接的两个超节点划入同一分区,再以该分区为核心,逐步吸纳相邻的高权重超节点,最终实现初步的平衡划分

细化(Uncoarsening/Refinement):反向映射,优化分区质量

核心目标:将初始划分方案从最小粗化图,逐步“反向映射”回原始图(即从超节点拆解为原始节点),并在每一步映射中优化分区,最终提升原始设计图的分割精度——进一步减少割边数量,同时确保各分区的资源完全平衡。

核心算法:FM算法(Fiduccia-Mattheyses):

➭计算“增益”:对每个待移动的节点,计算其从当前分区移动到目标分区后,“割边权重减少量”(正增益)与“资源平衡破坏度”(负增益)的差值,即“净增益”

➭选择最优移动:优先移动净增益最大的节点,直到无法通过移动节点提升分区质量(如所有节点移动的净增益均为负)

➭迭代优化:每完成一轮粗化图到更细一级图的映射,就执行一次FM算法优化,确保分区质量随图规模的扩大而持续提升

“多层次图划分”框架三步流程示意图

时序驱动分割:突破频率瓶颈的关键优化

经典图分割算法以“割边最少”为核心目标,但在硬件辅助验证中,验证工作频率才是最终衡量标准——频率过低会导致软件调试周期延长,甚至无法模拟芯片的真实运行场景。而频率的核心制约因素是“关键路径延时”,因此需要在传统图分割框架中引入“时序”维度,形成“时序驱动分割算法”。

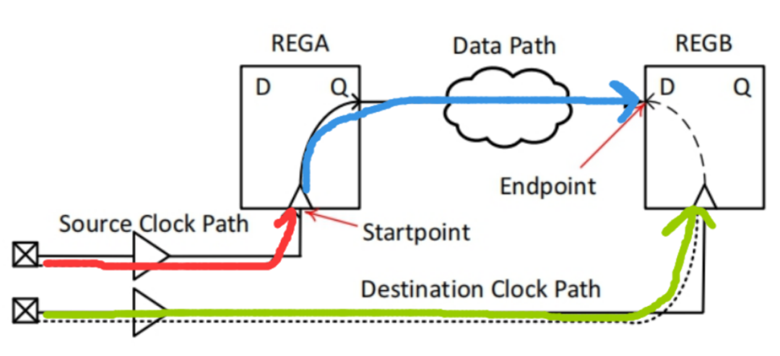

时序路径与关键路径

时序路径:芯片中信号从起点(如输入端口、寄存器时钟端)到终点(如输出端口、寄存器数据端)的传播路径,其延时由路径上所有逻辑单元(如与门、触发器)的延时之和决定。

时序路径示意图

关键路径(Critical Path):所有时序路径中,延时最长的路径。它直接决定芯片的最高工作频率——时钟周期必须大于等于关键路径的延时,否则信号无法在规定时间内到达终点,会违反寄存器的“建立时间”要求,导致电路功能错误。

时序驱动分割的核心策略

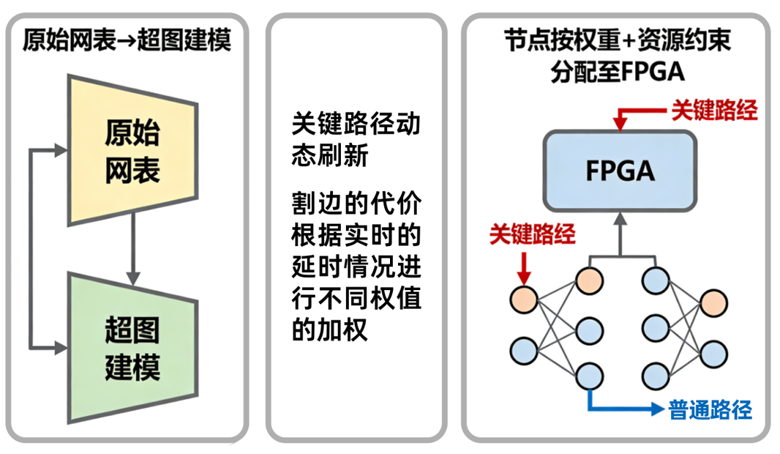

时序驱动分割的本质,是在“资源平衡”、“割边最少”的基础上,增加“关键路径延时最小”的目标,通过以下优化贯穿分割全流程:

粗化阶段:强化关键路径的节点关联

对关键路径上的节点,提升其“合并优先级”——即使这些节点的边权重并非最高,也优先将其合并为同一超节点,避免后续划分时被拆分到不同验证芯片,从而减少关键路径上的跨验证芯片割边(跨验证芯片连线的延时远大于验证芯片内部连线)

细化阶段:优先优化关键路径的割边

调整FM算法的“增益计算逻辑”:对关键路径上的割边,赋予更高的权重——移动关键路径相关节点时,若能减少关键路径上的割边,其“净增益”会被额外提升,从而优先被选择移动,最大限度减少关键路径上的跨验证芯片信号交互

结合时分复用(TDM)的特殊优化

TDM技术的作用与矛盾:当跨验证芯片割边数量超过验证芯片的I/O引脚数量时,需通过时分复用(Time Division Multiplexing) 技术,让多个割边信号“轮流使用”同一组I/O引脚(即划分不同时间时隙传输),从而解决物理连线不足的问题。但TDM会增加信号延时(每个信号需等待其专属时隙),且TDM比率越高(共享同一引脚的信号越多),延时越大

时序驱动的TDM优化策略:

➭对关键路径上的割边信号,禁用TDM或采用最低TDM比率(如1:1,即无复用),避免额外延时叠加

➭对非关键路径上的割边信号,可适当提高TDM比率,节省I/O引脚资源,在不影响整体频率的前提下满足连线需求

亚科鸿禹的时序驱动分割方案:技术特色与实践价值

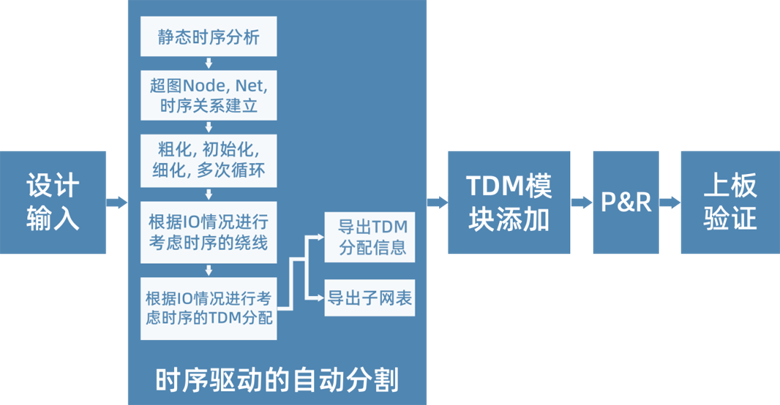

针对超大规模芯片的硬件辅助验证需求,亚科鸿禹基于上述技术原理,开发了定制化的时序驱动分割流程,核心特色如下,可有效提升分割效率与硬件辅助验证频率:

定制化分割引擎:内存高效,支撑更优算法

分割引擎基于时序网表的结构特点,采用定制化的数据存储架构,这使得引擎能在有限硬件资源下,加载更大规模的设计图(如轻松加载十亿门级),同时有更多内存余量尝试更复杂的优化算法(如多轮迭代的FM算法),为寻找最优分割结果奠定基础

全时序路径动态刷新:实时适配时序需求

分割过程中,实时动态刷新所有时序路径的延时数据(而非仅依赖初始时序分析结果),可精准捕捉分割调整对时序的影响——例如,某一节点移动后,不仅更新其所在路径的延时,还会联动更新关联路径的时序状态,确保分割策略始终贴合最新的时序需求,避免因时序信息滞后导致的优化偏差

自动优化跳数与TDM比率:平衡资源与时序

➭自动分析分割后的“信号跳数”(信号从源节点到目标节点经过的验证芯片数量),优先减少关键路径的跳数(跳数越多,跨验证芯片延时越大)

➭结合时序要求,智能分配TDM比率:对关键路径信号默认禁用TDM,对非关键路径信号根据I/O资源情况自动计算最优TDM比率(如2:1或8:1),在满足连线需求的同时,最大限度降低时序损耗

用户干涉的自动分割模式:兼顾自动化与灵活性

支持“自动分割为主、用户干预为辅”的模式:用户可根据实际需求(如某一模块需固定在特定验证芯片上、某一信号需优先保障时序),预先设置约束条件(如节点分区锁定、信号TDM比率限制),分割引擎会在约束范围内自动优化,既减少人工调整成本,又能满足定制化验证需求

超大规模设计支持:应对多FPGA阵列场景

可支持数十亿门级设计的分割任务,最多适配数百片验证芯片构成的阵列,且能通过“分层分割”策略(先将整体设计拆分为多组子系统,再对每组子系统进行FPGA级分割),确保大规模阵列的协同工作效率,满足先进制程SoC(系统级芯片)的硬件辅助验证需求

亚科鸿禹HAV平台时序驱动分割方案框图

总结

在超大规模芯片设计的征程中,硬件辅助验证的分割技术已然完成了从简单资源分配到复杂系统工程的华丽转身。经典多层次图分割框架搭建起了分割的基础逻辑架构,时序驱动的优化策略如关键路径优先、TDM智能适配等成功突破频率限制。亚科鸿禹推出的定制化分割方案,凭借内存高效利用、时序动态更新以及用户灵活操作等独特优势,进一步提升了分割的效率与适配程度,为超大规模芯片的快速验证筑牢了坚实根基,助力芯片产业在超大规模时代稳健前行。

推荐阅读: