【导读】本文为实现对水声信号的多通道同步采集并存储,提出了基于FPGA的多通道信号同步采集、高速大容量实时存储的系统设计方案,并完成系统的软硬件设计。该系统的硬件部分采用模块化设计,通过FPGA丰富的外围接口实现模块间的数据交互,软件部分采用Verilog HDL硬件描述语言进行编程,能够灵活的实现信号的采集及存储。实际应用表明,该设计具有功耗低,可高速实时存储,存储容量大,通用性强,易于扩展升级等特点。水声信号采集存储系统是海洋环境调查仪器的重要组成部分。开展水声环境调查所使用的海洋仪器要求设备通道多、同步性好、采样率高、数据存储容量大。

市场上常见的数据采集器多是采集某些固定种类的信号,动态范围比较小,通道数一般也比较少,有些还要求与主机进行接口等,这些都限制了其在水声信号采集中的应用。为满足需要,本文设计了适合于水声数据采集存储的较为通用的系统,系统单板具有8个采集通道,多个单板级联可实现多通道同步采集、USB高速存储。

1 总体设计

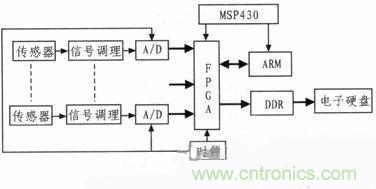

该系统总体结构如图1所示,上级电路通过级联接口发送采集指令,单片机初始化控制FPGA,控制FPGA首先判断单板是否为级联单板,再初始化相应的FPGA。采集模块的FPGA向需要同步采集的通道对应的A/D芯片提供统一的时钟,使得A/D同步的选择相应的通道进行数据的同步采样和转换,其结果传给负责缓存的FPGA,缓存在DDR对应的存储空间,然后由ARM控制存储模块的FPGA从DDR空间读取数据进行本地存储。

图1:系统总体结构图

2 系统硬件设计

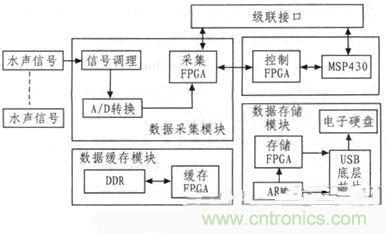

系统硬件主要由控制模块、数据采集模块、缓存模块、存储模块几部分组成,系统硬件结构图如图2所示。单片机功耗低、接口丰富、可靠性高,被系统用做上电引导芯片;FPGA器件具有集成度高、内部资源丰富、特别适合处理多路并行数据等明显优于普通微处理器的特点,所以系统采用XILINX公司不同型号的FPGA作为不同模块的主控芯片。针对系统设计中对采集存储实时性和同步性的要求,存储模块采用FPGA与ARM相结合的设计,采集主控制逻辑用ARM实现,FPGA负责数据的高速传输和存储。

图2:系统硬件结构图

控制模块相当于系统的值班电路,当系统作为从板工作时,只有控制模块和数据采集模块带电,其他模块关闭。由于FPGA内核电压只有1.2 V,在这种情况下系统工作电流不大于1 A,低功耗的设计保证系统可在无人值守的情况下长时间连续进行采集存储工作。系统需要多通道数据同时采集存储时,用户通过配置主板的控制模块参数设定8、16或32通道采集,主控FPGA通过级联接口发送统一的采集时钟到系统从板,从而实现系统多通道水声信号的同步采集及存储。另外,通过单片机接口也可以随时监控系统工作状态,系统具有修复功能,采集存储过程中出现错误时,可根据用户配置自动进行相应的错误处理。

数据采集模块具有8路数据采集存储通道,每通道采用TI公司的24位高精度模数转换器ADS1258,A/D采用15.36 MHz的外部输入时钟。设计中数字电源、模拟电源、参考电压单独布线,保证8通道信号隔离度几乎为零,降低了系统测量噪声。模块中FPGA并行控制多路数据转换,包括转换启动、转换同步、转换停止、转换数据输出等。

数据缓存模块采用64M byte的DDR作为缓存,因为DDR在一个时钟周期内进行两次数据传输操作,它能够在时钟的上升沿和下降沿各传输一次数据,具有双倍的数据传输量,DDR可以在与SDRAM相同的总线频率下达到更高的数据传输率。缓存模块中的FPGA对DDR的数据写入和存储

模块中的FPGA对数据的读取是通过兵乓传输结构实现的。当FPGA写满DDR上半区后,向存储模块申请中断,存储模块响应中断后,读出上半区数据到存储模块;同时FPGA向DDR的下半区写数据,写满下半区后也向存储模块发出中断,通知存储模块读出下半区数据。通过乒乓传输保证了系统数据采集和数据传输可连续进行。

数据存储模块的作用是将多通道24 bit数据经过缓存模块,按采样的时间顺序,以低字节到高字节的次序,依次将其写入电子硬盘。系统采用IPD的iPD-USB型300G电子硬盘作为存储器。由于它没有普通硬盘的旋转介质,因而抗震性极佳,同时工作温度很宽,可工作在-40~+85℃,再加上重量较硬盘轻很多,非常适用于水下声信号采集存储设备。根据系统要求,采用USB底层芯片配合存储模块实现大容量高速USB存储,速度可达480Mbit/s,比全速USB存储快了40倍。

[page]

3 系统软件设计

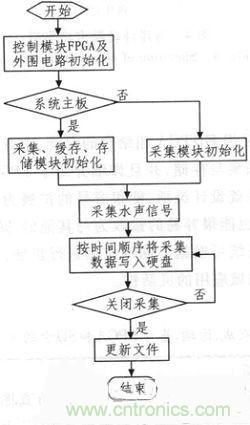

程序设计采用Verilog HDL硬件描述语言,软件采用模块化设计,提高了程序的可移植性和可维护性。系统的软件主要分为初始化模块、水声数据采集模块、数据缓存模块、数据存储模块、中断服务程序模块等构成。初始化程序仅在系统复位及程序开始时执行一次,完成各模块主控芯片及外围电路的初始化;数据采集模块通过模拟量输入端口采集水声信号;数据缓存模块负责将DDR中缓存的数据依次输出给存储模块;数据存储模块每分钟向电子硬盘中写入一个文件。软件设计的流程图如图3所示。

图3:软件系统流程图

4 试验应用

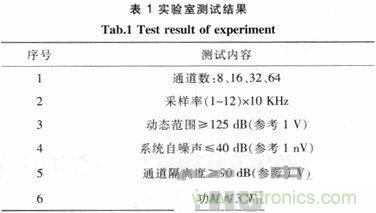

4.1 实验室测试结果

系统的性能测试是保证系统稳定,可靠工作的重要手段。在实验室测试过程中,主要对系统的整体性能进行考察,其中包括:多通道采集同步误差、数据吞吐量、系统功耗、自噪声等。测试结果如表1所示。

4. 2 海上试验结果

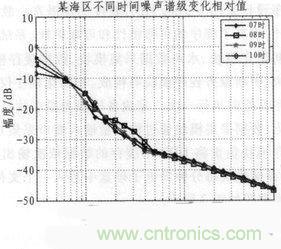

本系统应用的海洋环境噪声测量潜标在中国某海域进行了海上实验,系统连续工作3个月,性能稳定可靠,并获取了大量完整有效的海洋环境噪声数据。测量的海洋环境噪声功率谱符合海洋环境噪声的自然分布规律。实测海洋环境噪声功率谱如图4所示。

图4:海洋环境噪声功率谱

本系统采用多FPGA相结合的设计,很好的完成了高速多通道数据采集与存储,并且详细介绍了FPGA各模块的设计方法。本系统设计灵活,能很容易的扩展为多通道数据采集存储系统,也能很容易的修改为与其他的A/D转换芯片接口。

相关阅读:

技术达人:音频信号采集与AGC算法的DSP实现

霍尔传感器信号采集与显示系统设计

麦克风阵列信号系统采集的设计